# **EIC Roman Pots / AC-LGAD**IJCLab Progress Report

BNL-IJCLab-OMEGA Meeting - May 6th, 2021

**Dominique Marchand** on behalf of IJCLab team:

Carlos Munoz Camacho, Emmanuel Rauly, Ana-Sofia Torrento, Laurent Serin

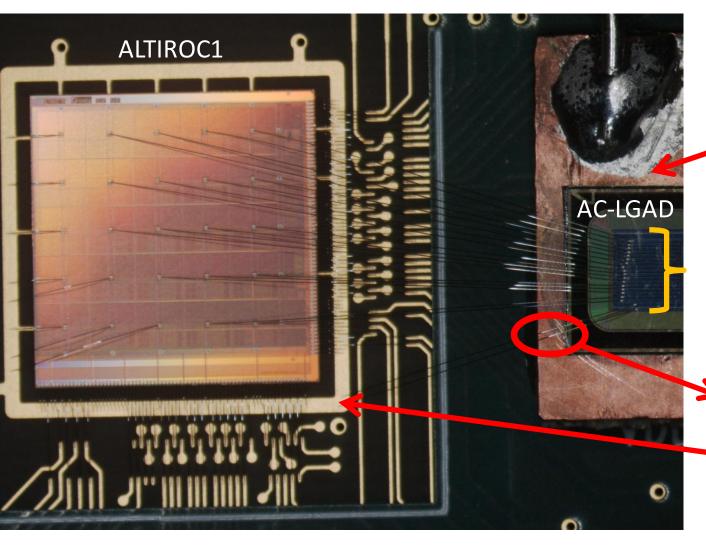

- Progress report on activities related to an AC-LGAD (strips) sensor wire-bonded by BNL onto an ALTIROC1\_V2 (PCB #30)

- **➢** Outlook

#### **Progress report summary**

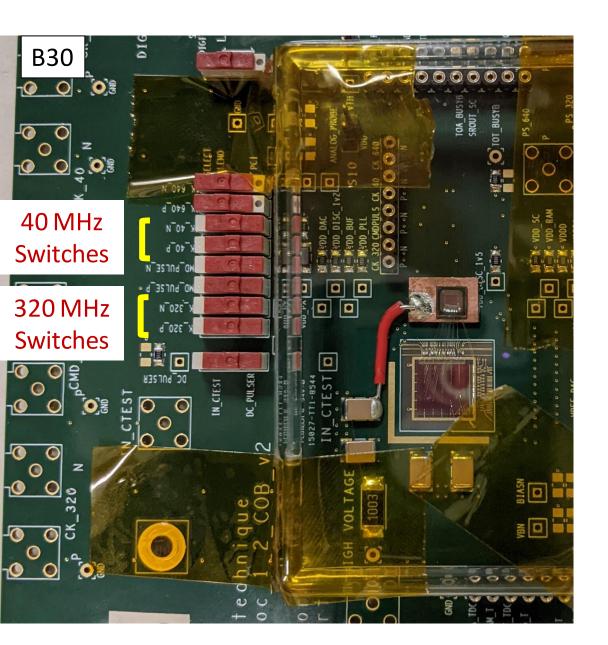

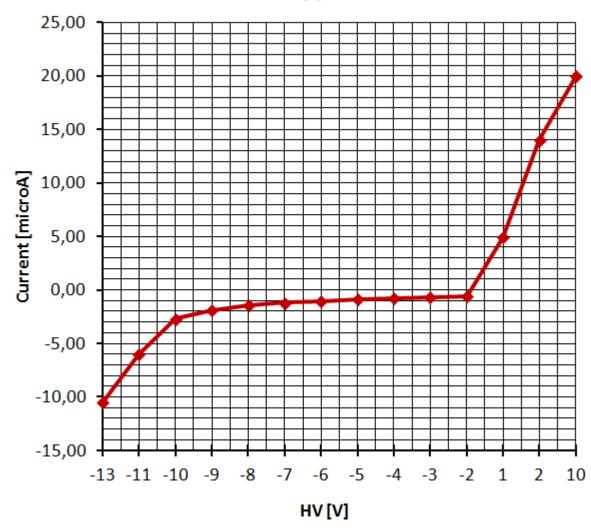

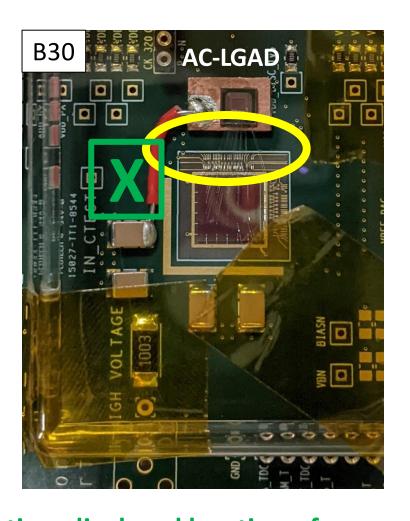

- ASIC PCB B30 including an AC-LGAD (stripped) sensor wire-bonded by BNL team onto an ALTIROC1\_V2 (only 17 channels wire bonded to 25 channel ALTRIROC1) received on March 23<sup>rd</sup>

- Installation of ALTIROC1\_V2 specific software suite onto a dedicated "EIC" laptop under the guidance of Laurent Serin and Nikola Makovec, ATLAS/High Granularity Timing Detector (HGTD), April 7<sup>th</sup> and 13<sup>th</sup>.

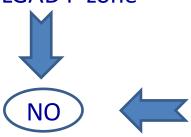

- Observation of some ALTIROC1 channels on scope => attempt to proceed to a depletion of AC-LGAD: leakage current observed much higher than expected (-10.5  $\mu$ A for an applied voltage of -13 V, increasing with HV) => Measurements I = f(HV)

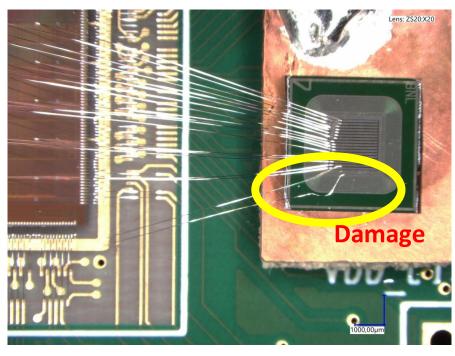

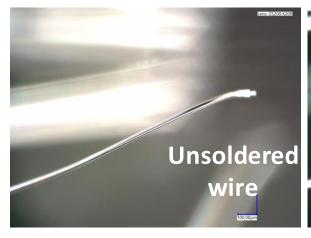

- under microscope and multimeter measurements: no obvious short; 2 wires connected to the guard ring accidently damaged (1 unsoldered, 1 crooked)

- Attempt to use the Captinnov semi-automated probe station => requires a chuck adaptor or to use the manual one

- Observation on scope of the 25 individual ALTIROC1 PreAmplifier channels triggered by the ALTIROC1 command pulse => identification of the 17 channels wire-bonded / 8 channels connected to the ground.

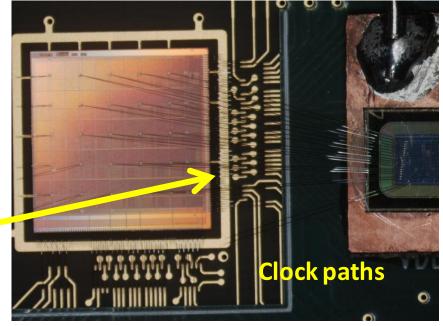

#### Layout of OMEGA ALTIROC1 wire-bonded by BNL to an AC-LGAD (strips) on ASIC PCB #30

## -HV probe touches here

Whatever we do, these wires (Ac-pads and inputs of the ALTIROC) should stay ~ GND, as only 100nm of dielectric separates them from the n-pad at GND

Guard Ring & n-pad go to GND So you can touch here:

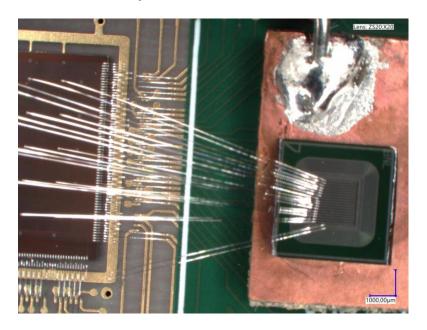

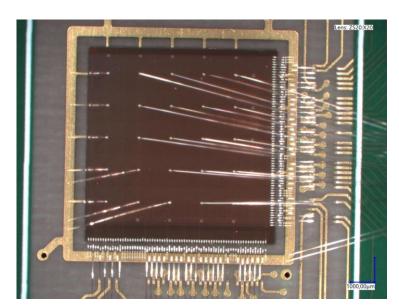

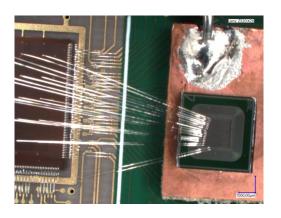

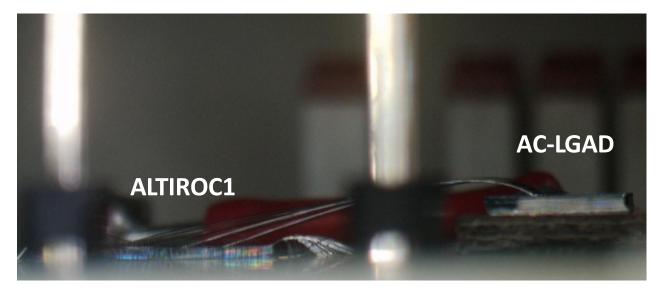

## Microscope snapshots

April 20<sup>th</sup>, 2021

## April 30<sup>th</sup>, 2021

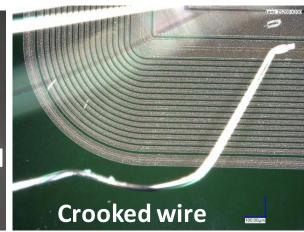

## IJCLab, AC-LGAD testbench setup

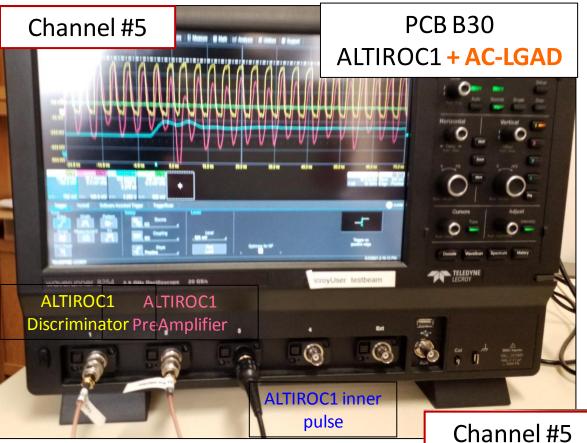

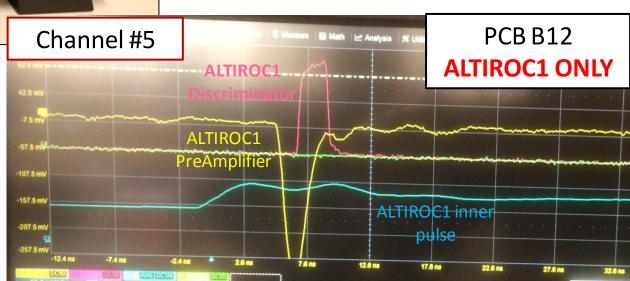

## (ALTIROC1\_V2 + AC-LGAD) typical observed output signals on scope: B30 and B12 PCBs

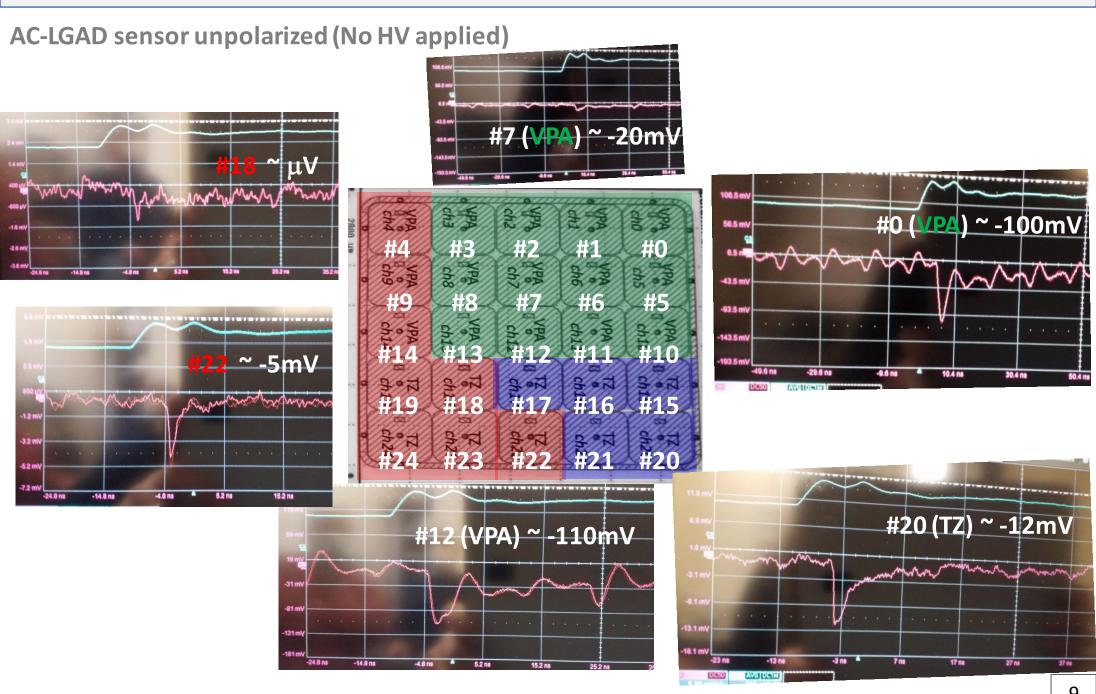

AC-LGAD sensor unpolarized (No HV applied)

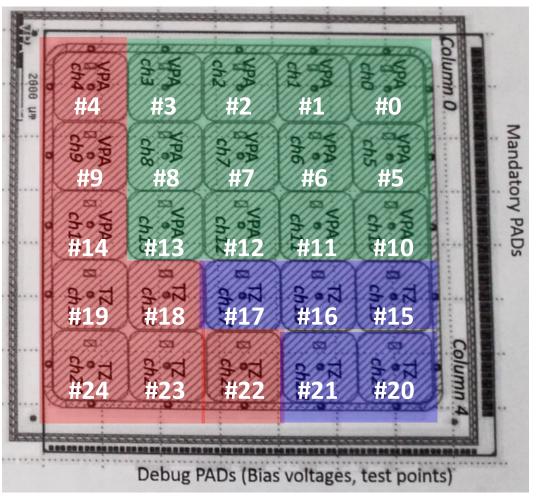

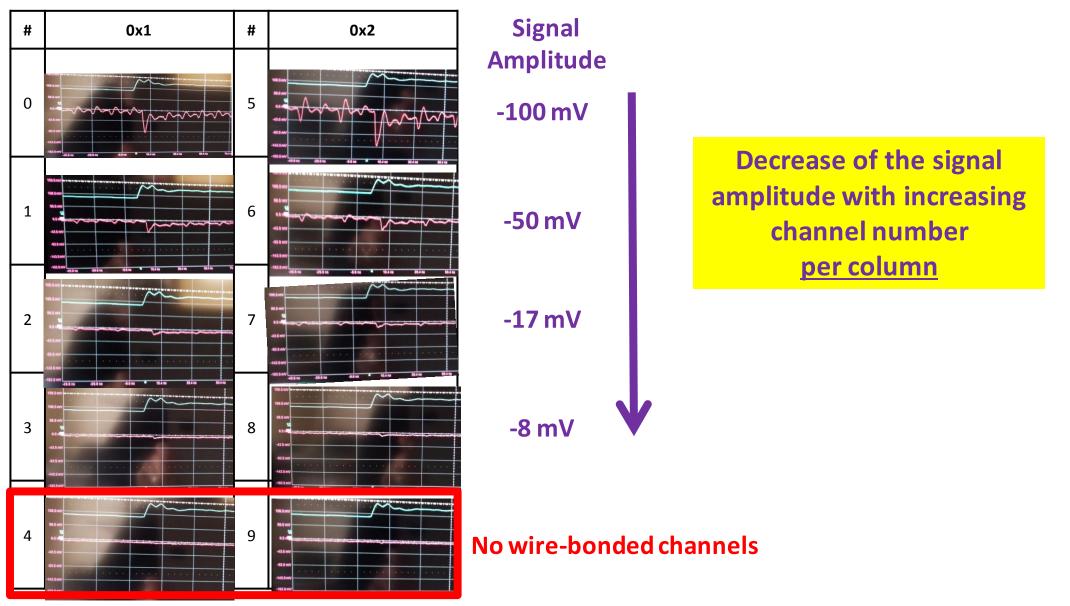

## **ALTIROC1\_V2** mapping / identification of AC-LGAD wire-bonded channels

#

AC-LGAD channels connected to GND

#

AC-LGAD channels connected to an ALTIROC1

Voltage PreAmplifier channel

#

AC-LGAD channels connected to an ALTIROC1

TransImpedance PreAmplifier channel

#### ALTIROC1\_V2

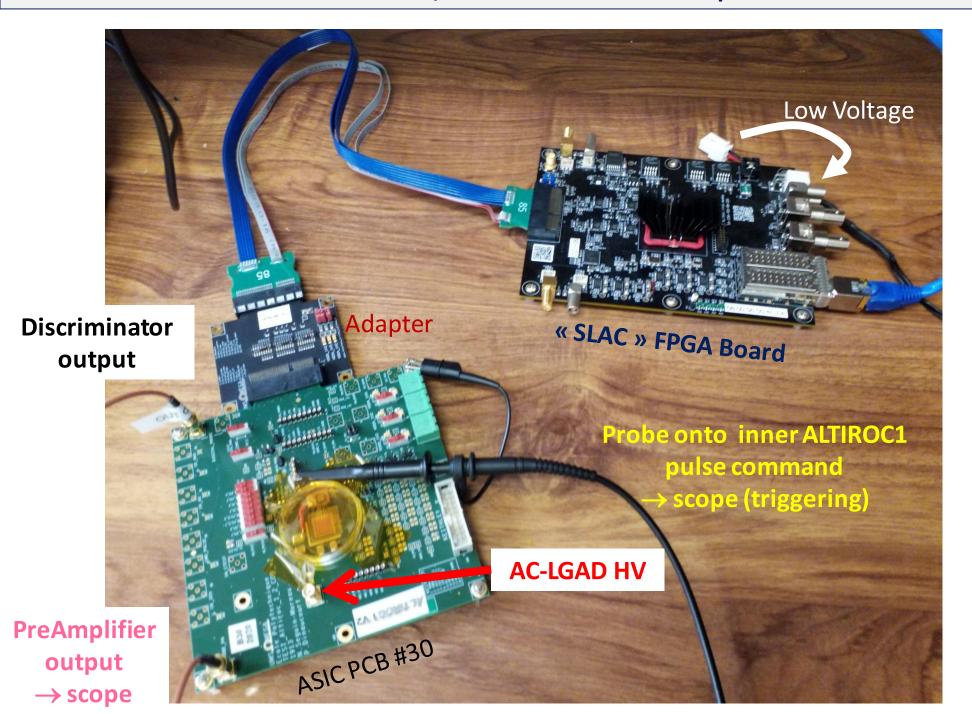

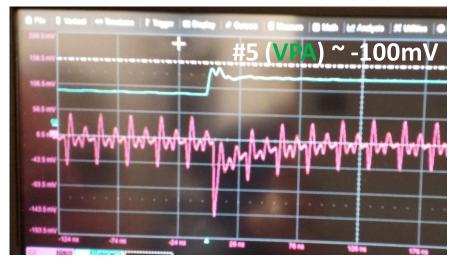

## (ALTIROC1\_V2 + AC-LGAD) typical observed output signals on scope

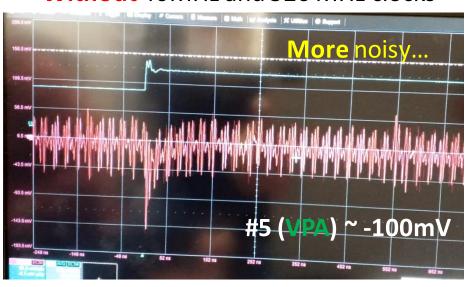

## (ALTIROC1\_V2 + AC-LGAD) observed output signals on scope : impact of 40MHz/320MHz clocks

## AC-LGAD sensor unpolarized (No HV applied)

#### With 40MHz and 320 MHz clocks

#### Without 40MHz and 320 MHz clocks

#### Measurements of B30 PCB including ALTIROC1\_V2 + 17 channels wire-bonded LGAD-AC (strips)

Same scale for all 25 channels of ALTIROC1: (No additionnal capacitance -  $0x0 \cong 6$  pF; Discriminator output signal disabled)

\*vertical: -193.5 mV  $\rightarrow$  156.5 mV; 50 mV / div.

\* horizontal: -49.6 ns  $\rightarrow$  50.4 ns; 20 ns / div.

Command pulse signal (triggering) [Amplitude 0x3f = max] PreAmplifier output signal

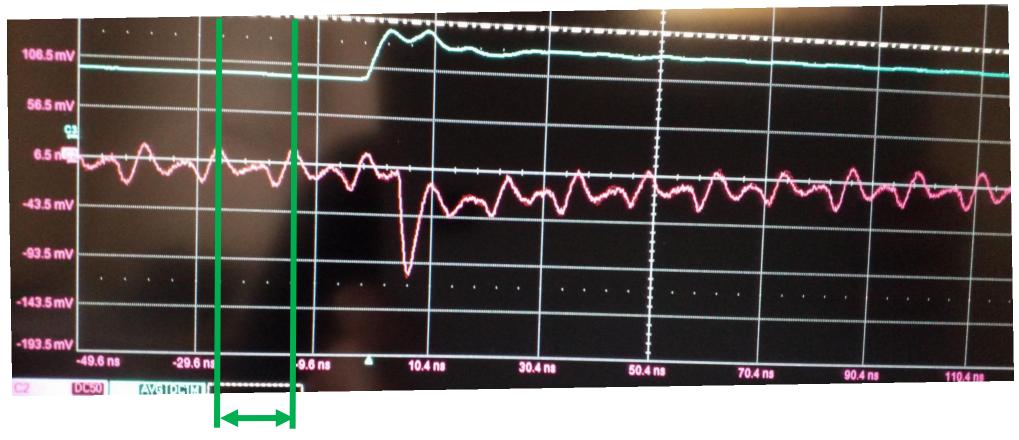

## Channel #0 (ALTIROC1)

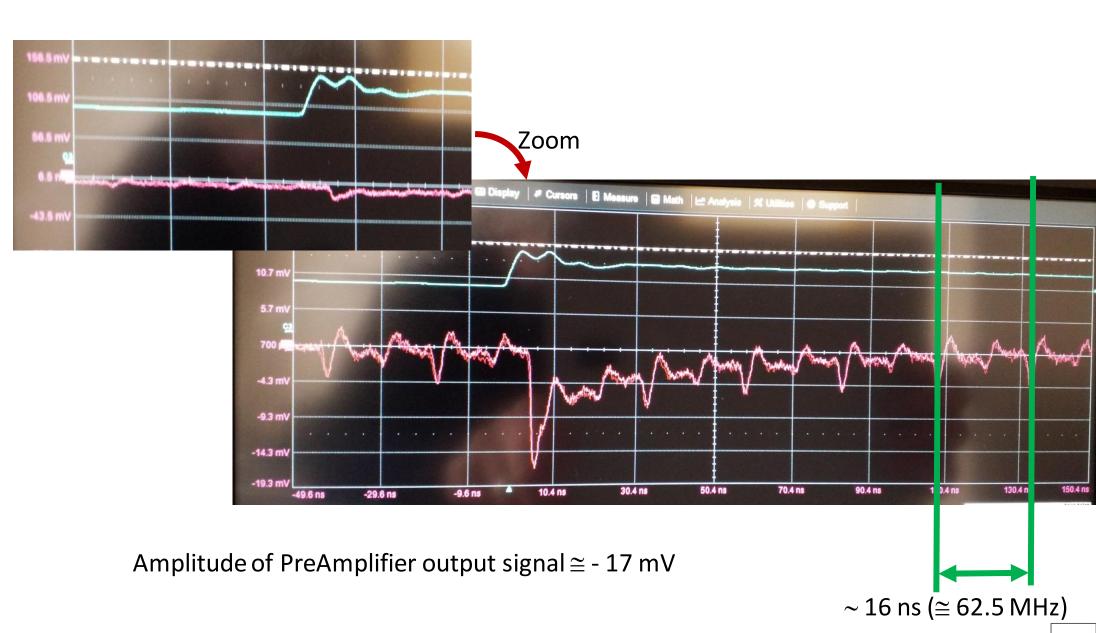

Amplitude of PreAmplifier output signal  $\cong$  - 100 mV

$\sim$  16 ns ( $\cong$  62.5 MHz)

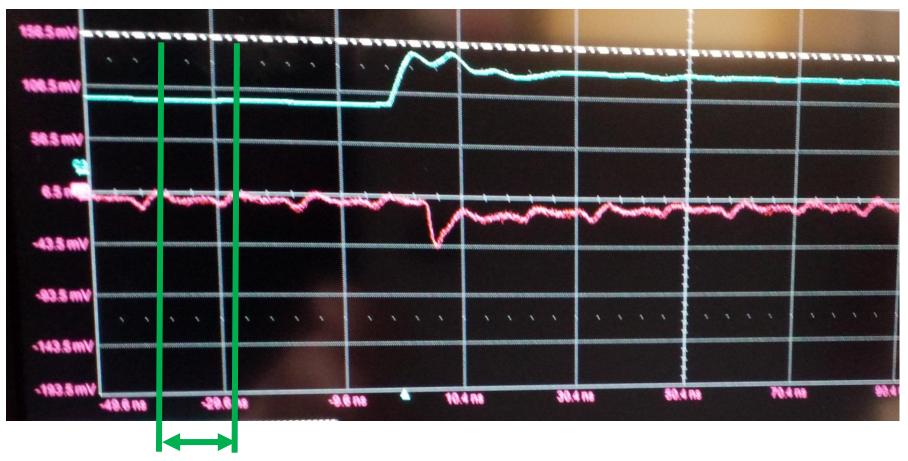

## Channel #1 (ALTIROC1)

Amplitude of PreAmplifier output signal ≅ - 50 mV

~ 16 ns (≅ 62.5 MHz)

## Channel #2 (ALTIROC1)

We measure impedance with ohm-meter between HV input and GND Measurement > 10Mohms

## Attempt to deplete AC-LGAD: measurement of the current versus HV applied

First exploration: -10  $\mu$ A at -13V, current increasing with the HV applied

Suspecting a bad polarization of the AC-LGAD P zone

Observed leakage current too high

Reasons?

#### Current versus HV applied to AC-LGAD

## (ALTIROC1\_V2 + AC-LGAD) Wire-bonding concerns (1/2)

How the AC-LGAD sensor is connected to HV copper plate? Conductor glue, adhesive tape?

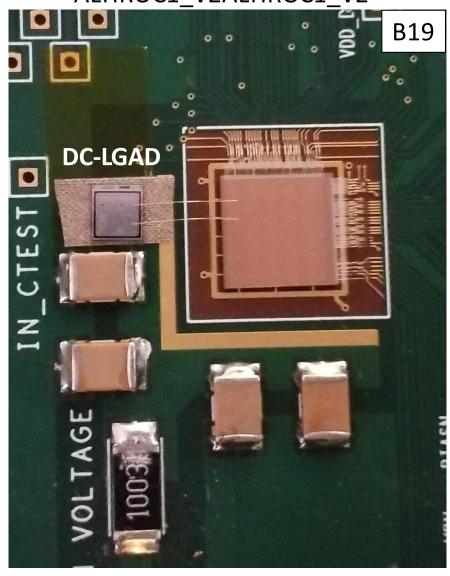

## (ALTIROC1\_V2 + AC-LGAD) Wire-bonding concerns (2/2)

PCB **#19** (at IJCLab): example of an **DC-LGAD** wire-bonded onto an ALTIROC1\_V2ALTIROC1\_V2

Suggestion: displaced location of the wire-bonding / AC-LGAD to avoid clock paths

## **Summary**

- > 2 wires connected to guard ring have been accidentally damaged

- Observed AC-LGAD leakage current too high (no depletion)

- No obvious short cut observed

- ➤ Order of magnitude of PreAmplifier output signal amplitude not understood for AC-LGAD wire-bonded channels onto ALTIROC1\_V2

- ➤ Coupling with a clock-like signal: ~60 MHZ??

- > Removing 40 MHz and/or 320MHz clock(s) has no effect

- ➤ PreAmplifier output signal amplitude of AC-LGAD wire-bonded channels onto ALTIROC1\_V2 decrease with increasing channel number per column (from #0 to #3; #5 to #8; #10 to #13; #15 to #17; #20 to #21

- ➤ Impact of PreAmplifier type (VPA / TZ) on output signals: less coupling with TZ

- ➤ Coupling with command pulse observed on AC-LGAD channels not wire-bonded to ALTIROC1

- ➤ Investigation on-going to design a dedicated support for the PCB enabling to use IJCLab probe station

# **Questions / suggestions**

- ➤ Which typical signal should we observe? Amplitude order of magnitude?

- > Prescription for connected AC-LGAD guard ring to Ground?

- ➤ How the voltage under the AC-LGAD capacitance defined?

- > Should the wire-bonding be displaced?

# **Outlook?**