# EIC Roman Pots / AC-LGAD IJCLab Progress Report

BNL-IJCLab-OMEGA Meeting - June 2<sup>nd</sup>, 2021

Dominique Marchand

on behalf of IJCLab team:

Carlos Munoz Camacho, Emmanuel Rauly, Laurent Serin, Ana-Sofia Torrento, Philippe Vallerand

- Progress report on activities related to:

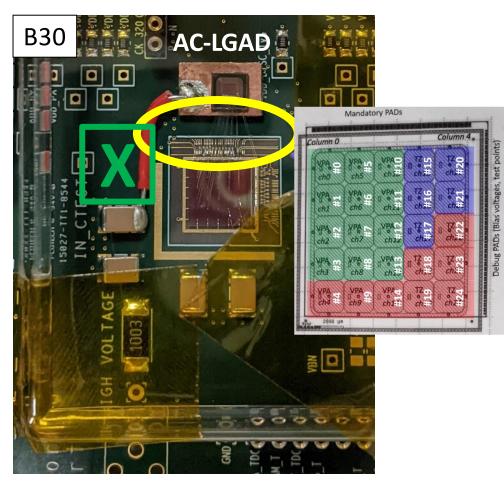

- \* an AC-LGAD (strips) sensor, 17 channels wire-bonded by BNL to an ALTIROC1\_V2 (PCB #30)

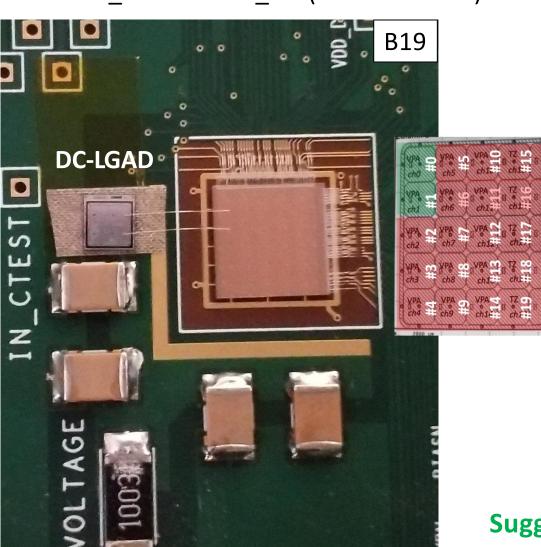

- \* a DC-LGAD (pixels) sensor, 2 channels wire-bonded to an ALTIROC1\_V2 (PCB #19)

B19 and B30 PCBs shipped to BNL: estimated delivery on Thursday June 3rd

- **≻** Outlook

- \* suggestions for next the wire-bonding(s) of an AC-LGAD to an ALTIROC1\_V2

- \* foreseen activities at IJCLab

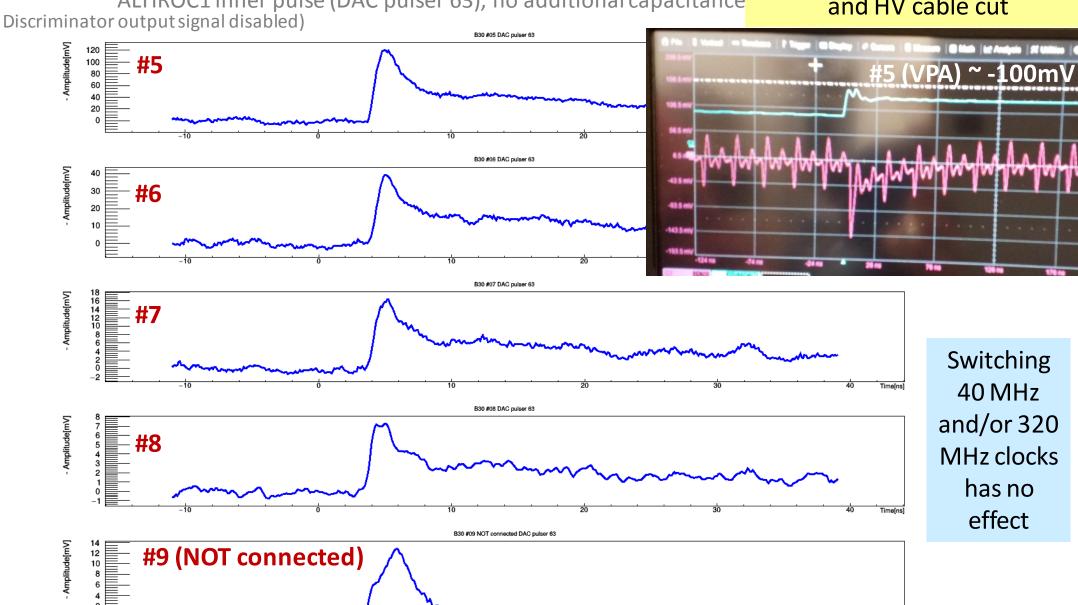

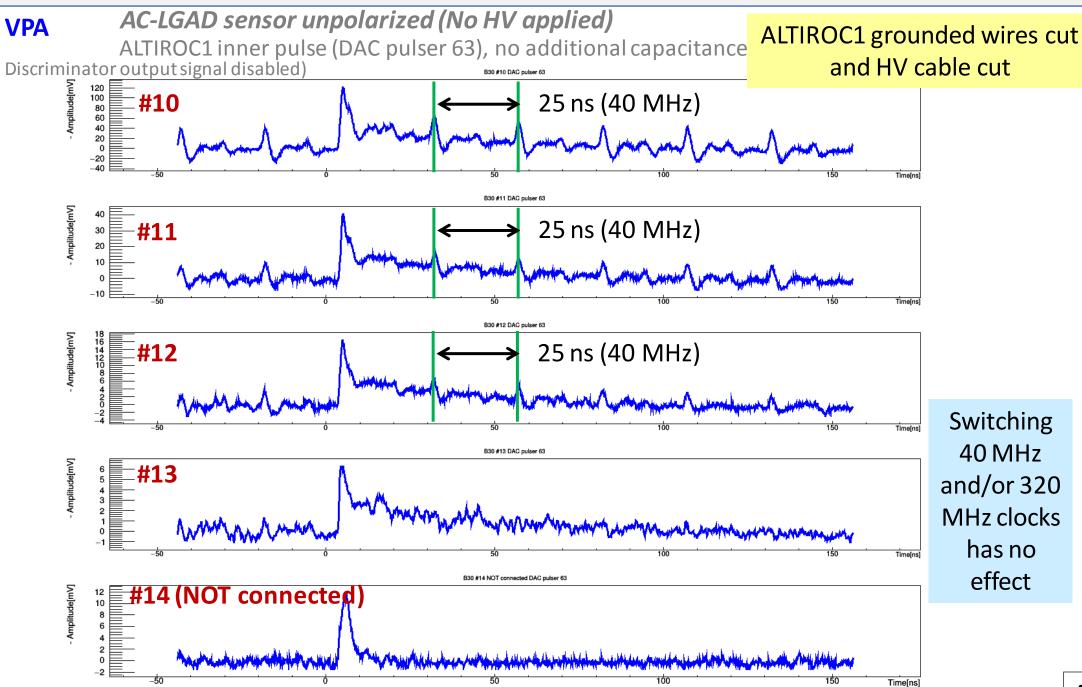

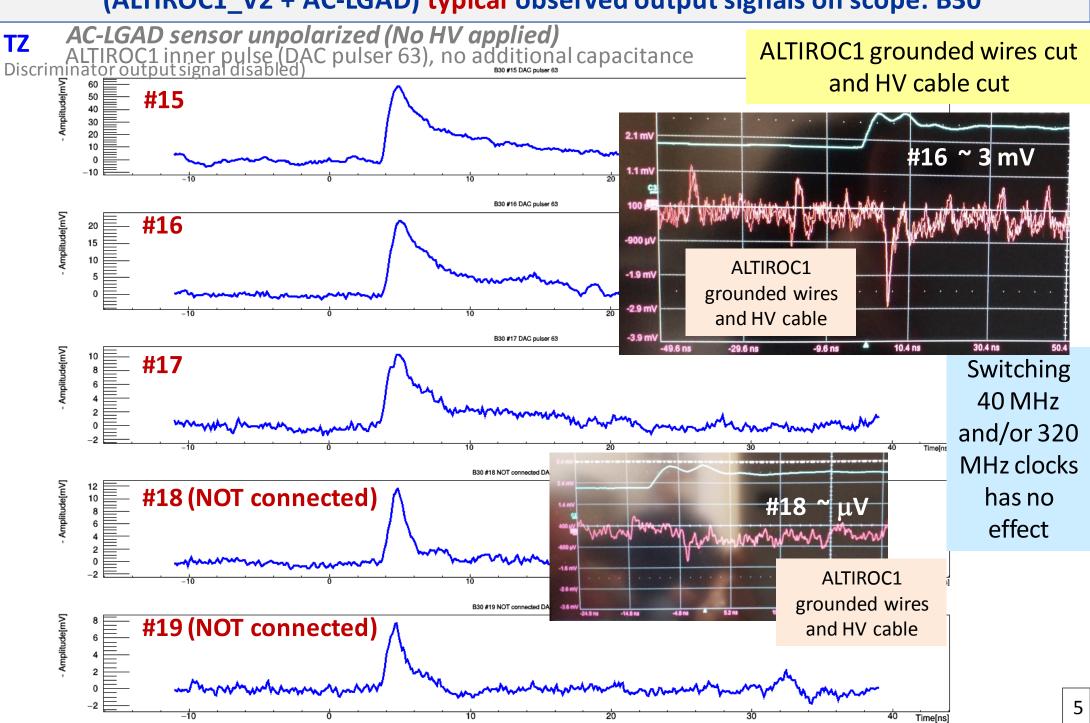

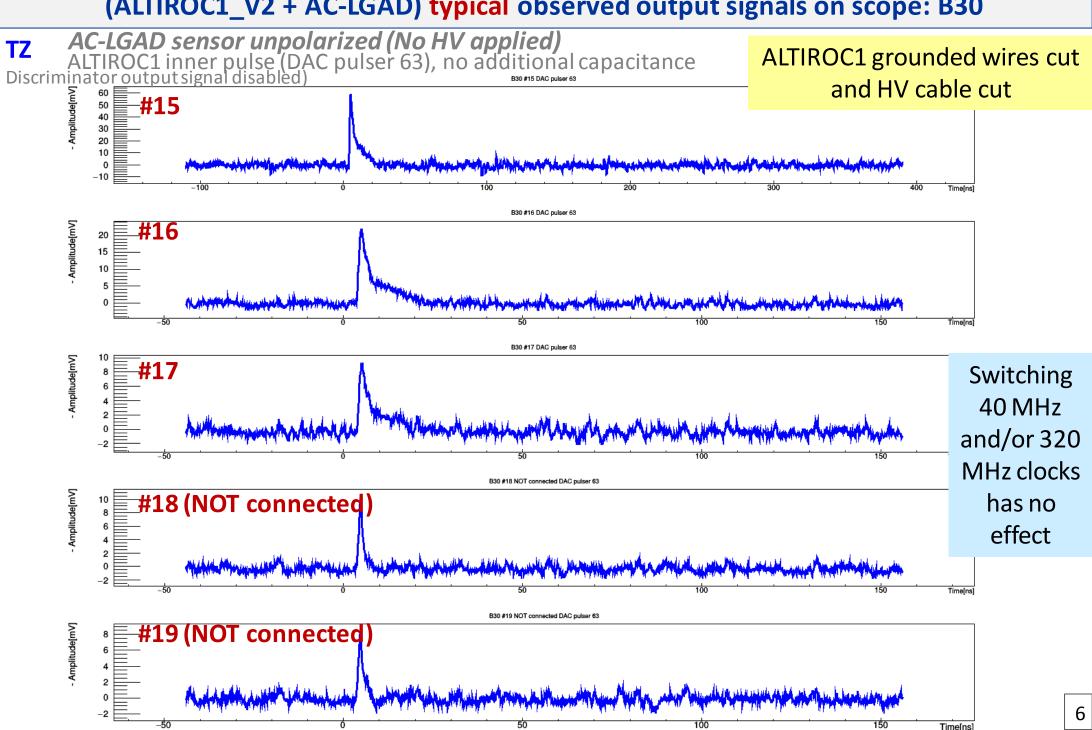

#### **VPA** AC-LGAD sensor unpolarized (No HV applied)

ALTIROC1 inner pulse (DAC pulser 63), no additional capacitance

ALTIROC1 grounded wires cut and HV cable cut

Time[ns]

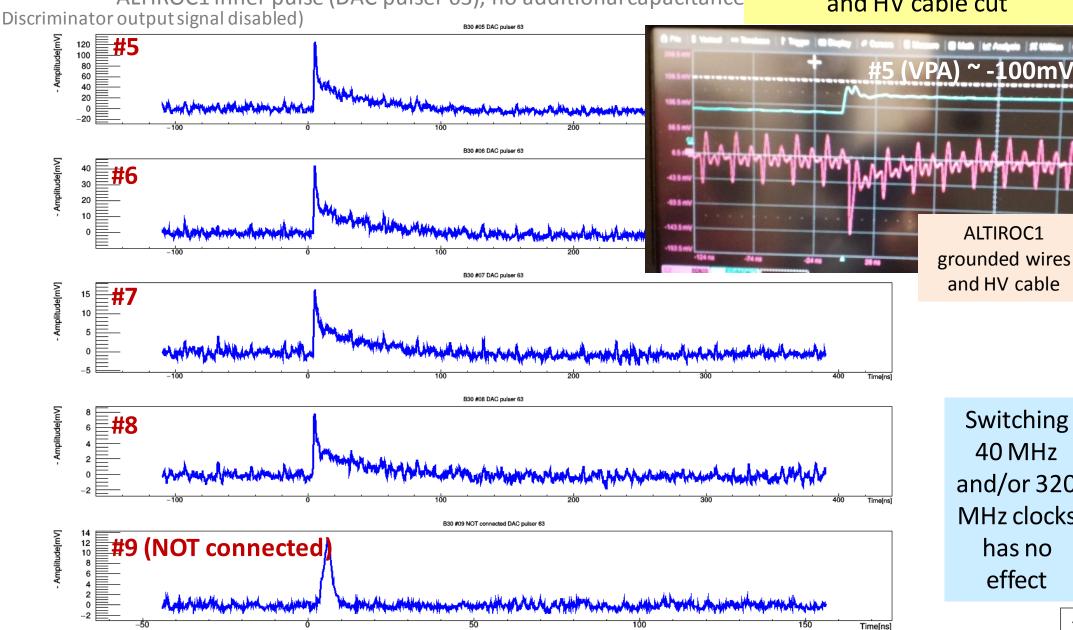

#### **VPA** AC-LGAD sensor unpolarized (No HV applied)

ALTIROC1 inner pulse (DAC pulser 63), no additional capacitance

ALTIROC1 grounded wires cut and HV cable cut

Switching 40 MHz and/or 320 MHz clocks has no effect

**ALTIROC1**

and HV cable

# (ALTIROC1\_V2 + AC-LGAD) observed output signals on scope: B30 SUMMARY

# AC-LGAD sensor unpolarized (No HV applied): no way to deplete the sensor ALTIROC1 inner pulse (DAC pulser 63), no additional capacitance

- ➤ Disconnecting wires from ALTIROC1 to ground for non wire-bonded channels had an impact on output signal amplitudes: « proportional » to inner pulser

- > Disconnecting HV cable reduced coupling: much cleaner signals

- Switching 40 MHz and/or 320 MHz clocks on PCB has no effect (slightly more noisy)

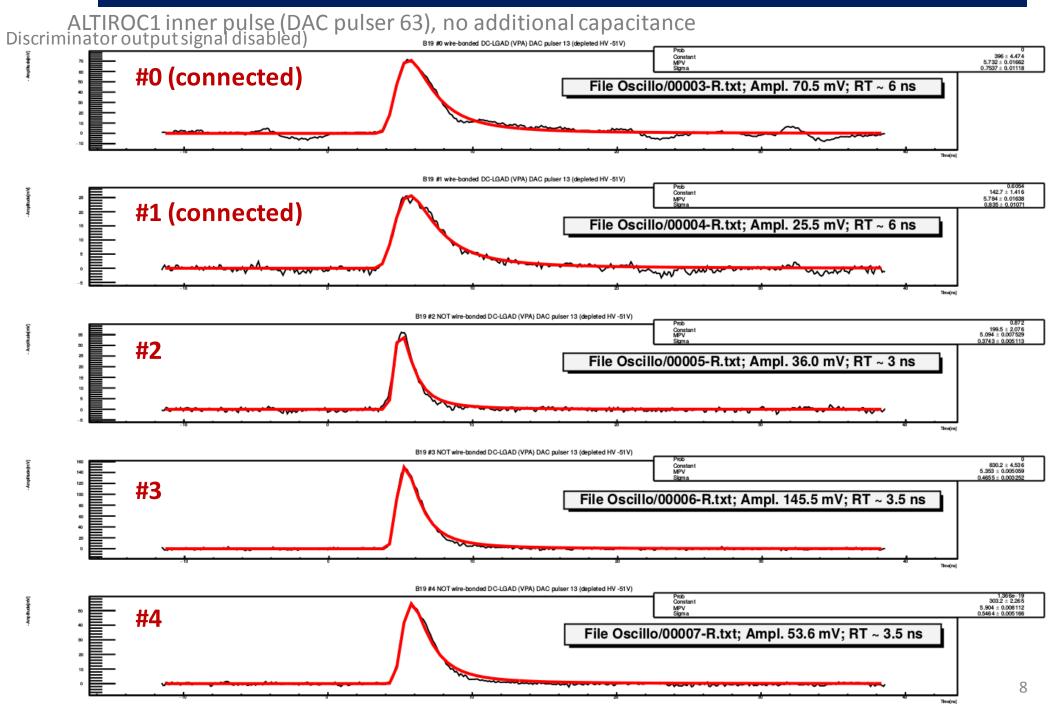

# B19 (wire-bonded ALTIRC1 to DC-LGAD (depleted -51V): channels #0 -> # 4

ALTIROC1 inner pulse (DAC pulser 63), no additional capacitance Discriminator output signal disabled) B19 #15 NOT wire-bonded DC-LGAD (VPA) DAC pulser 13 (depleted HV -51V) 162.7 ± 1.521 #15 File Oscillo/000018-R.txt; Ampl. 29 mV; RT ~ 2 ns B19 #16 NOT wire-bonded DC-LGAD (VPA) DAC pulser 13 (depleted HV -51V) 89.76 ± 1.608 4.677 ± 0.009249 0.2699 ± 0.006446 #16 #16 File Oscillo/000019-R.txt; Ampl. 16 mV; RT ~ 2 ns B19 #17 NOT wire-bonded DC-LGAD (VPA) DAC pulser 13 (depleted HV -51V) #17 File Oscillo/00020-R.txt; Ampl. 10 mV; RT ~ 2 ns B19 #18 NOT wire-bonded DC-LGAD (VPA) DAC pulser 13 (depleted HV -51V) Prob Constant MPV #18 File Oscillo/00021-R.txt; Ampl. 6 mV; RT ~ 2.5 ns B19 #19 NOT wire-bonded DC-LGAD (VPA) DAC pulser 13 (depleted HV -51V) 31.02 ± 0.7674 4.692 ± 0.01974 0.4244 ± 0.01427 #19 File Oscillo/00022-R.txt; Ampl. 5 mV; RT ~ 3 ns

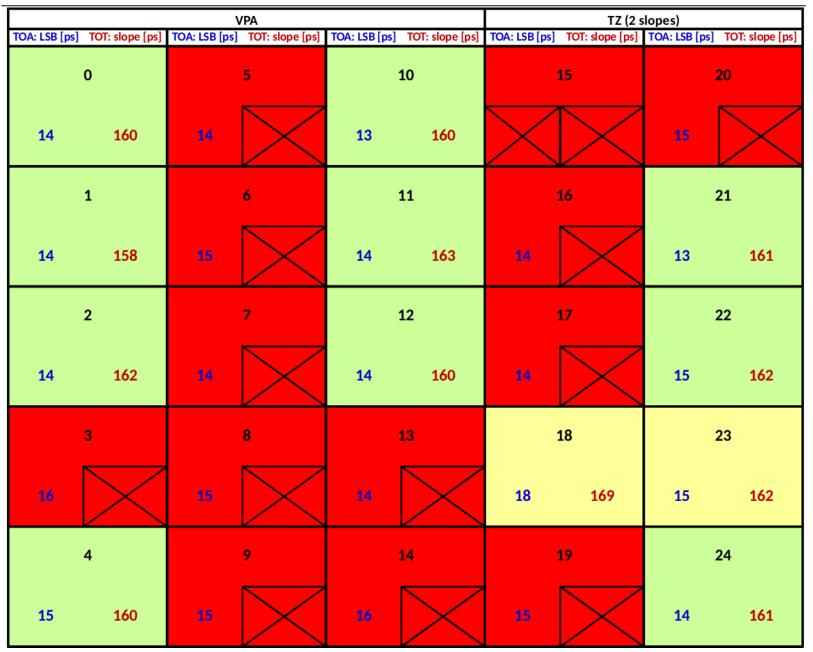

#### **TDC measurements on B19 and B30 PCBs**

- ➤ 2 TDCs in ALTIROC1: 1 for TOA, 1 for TOT

- ➤ 3 Delay-Locked Loop to adjust soldering discrete resistance on PCB for TOA (LSB ~20ps) and for TOT (slope ~160 ps)

- B19: adjustment performed May 12th (Nathalie and Laurent)

- B30: DLL NOT adjusted (a jumper added)

- ➤ Requires to set a switch (#18) on interface board (has to be blue) to generate sliding delays within a 2.5 ns window (TOA) and to vary the width (TOT)

- → GOAL: to identify « good » / «working » ALTIROC TDC channels to suggest for next AC-LGAD wire-bonding to ALTIROC1 V2.

# TOA and TOT measurements; DLL adjusted

| VPA           |                 |      |     |               |                 | TZ (2 slopes) |                 |               |                 |

|---------------|-----------------|------|-----|---------------|-----------------|---------------|-----------------|---------------|-----------------|

| TOA: LSB [ps] | TOT: slope [ps] |      |     | TOA: LSB [ps] | TOT: slope [ps] | TOA: LSB [ps] | TOT: slope [ps] | TOA: LSB [ps] | TOT: slope [ps] |

| 0             |                 | 5 27 |     | 10<br>28 153  |                 | 15            |                 | 20<br>26 153  |                 |

| 1             |                 | 6    |     | 11            |                 | 16            |                 | 21            |                 |

| 26            | 152             | 27   | 152 | $\times$      | $\times$        | 26            | 153             | 28            | 153             |

| 2             |                 | 7    |     | 12            |                 | 17            |                 | 22            |                 |

| 27            | 152             | 26   | 152 | 26            | 147             | 27            |                 | 28            |                 |

| 3             |                 | 8    |     | 13            |                 | 18            |                 | 23            |                 |

| 26            |                 | 26   |     | 28            |                 | 27            | 153             | 27            |                 |

| 4             |                 | 9    |     | 14            |                 | 19            |                 | 24            |                 |

| 26            | 153             | 27   |     | 27            | $\times$        | 28            | 153             | 25            | 153             |

# TOA and TOT measurements; DLL NOT adjusted (jumper added)

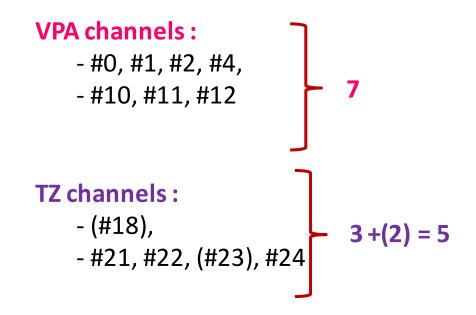

10 + 2 ALTIROC1 TDC channels OK

# (ALTIROC1\_V2 + AC-LGAD) wire-bonding concerns (1/2): suggestion of TDC channels

PCB #30: 10 (+2) functional TDC channels

We suggest that at least 3 VPA AND 3 TZ channels to be wire-bonded

### (ALTIROC1\_V2 + AC-LGAD) wire-bonding concerns (2/2): sensor implantation

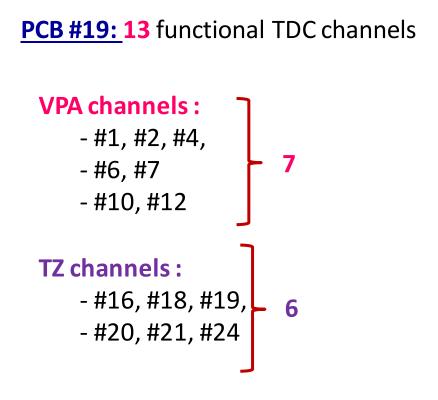

#### PCB **#19**:

a **DC-LGAD** wire-bonded to an ALTIROC1\_V2ALTIROC1\_V2 (channels 0 & 1)

#### PCB **#30**:

an **AC-LGAD** wire-bonded to an ALTIROC1\_V2ALTIROC1\_V2 (17 channels)

Suggestion: displaced the location of the wire-bonding / AC-LGAD to avoid clock paths and use the copper plate for HV

# Summary of suggestions for next AC-LGAD wire-bonding

- To use both, B30 and B19 PCB, if possible

- > NOT to connect ALTIROC1 non wire-bonded channels to ground

- > Displace the location of AC-LGAD sensor on PCB to avoid clock paths

- > To avoid to add an additional HV cable candidate for selfic noise

- > To choose ALTIROC1 TDC functional channels

- To measure on a probe station I(V) curve prior to shipping to IJClab

# Questions

- > AC-LGAD (4 x 4 pixels) availability at BNL?

- ➤ When the next wire-bonded could be ready to be shipped to IJCLab?

# **Outlook**

- To make measurements at ILJCLab on previously tested PCBs holding an ALTIROC1\_V2 to check our setup.

- To make a simulation of resulting peak position resolution to evaluate the necessary number of bits (10 // 8) for ADC option based on Maxime's simulation of signal amplitude sharing in neighboring pads (3 x 3).

- > A PCB with an ALTIROC1\_V3B might be available after the summer.