# Universita' di Trieste and INFN Trieste Contributions to EIC SC

- Past/current activities within ITS3

- Plans

#### Giacomo Contin

Università di Trieste and INFN Sezione di Trieste

EIC Silicon Consortium meeting – July 26<sup>th</sup> 2021

#### Pixel sensor bending

First bending development

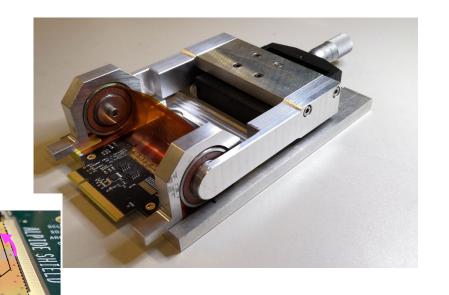

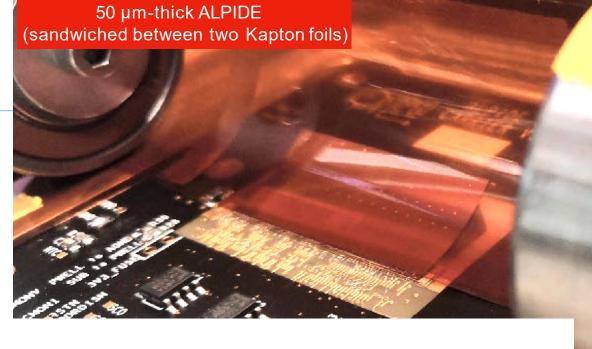

Design and production of sensor bending tools

- Prototyping of bending tools for existing sensors

- Bent sensor surface description

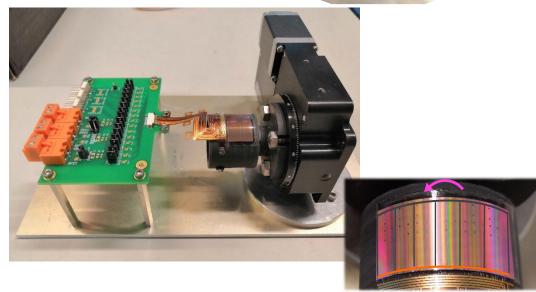

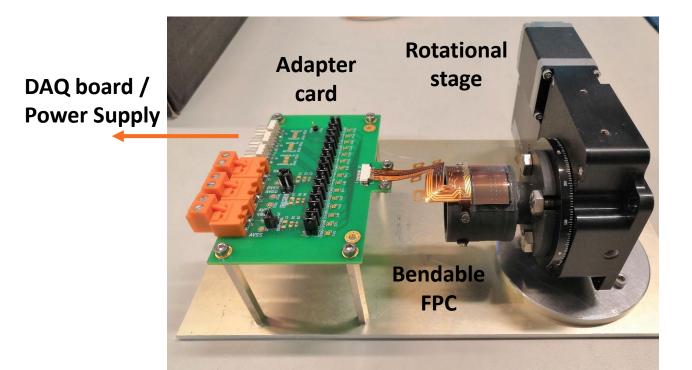

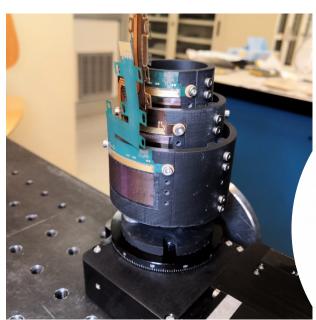

#### **Laboratory tests to characterize bent ALPIDEs**

- in terms of thresholds and fake-hit rate

- different set-ups are tried

- experience on handling is gained

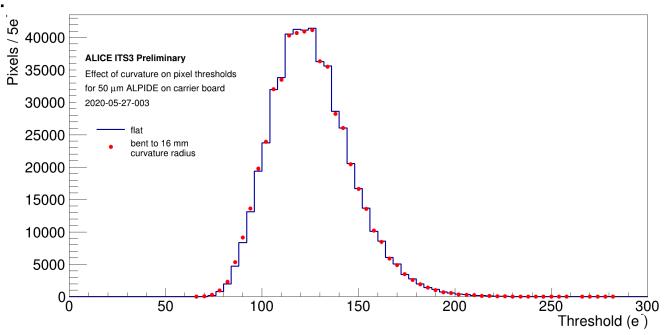

- The curvature effect is not noticeable on:

- pixel thresholds, FHR, pixel responsiveness

- tested down to below nominal bending radius

- Multiple chips successfully installed and tested in lab, and sent to testbeams

DUT assembly and lab-characterization

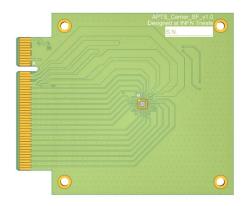

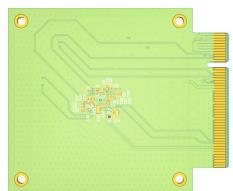

Development of APTS Sf carrier board

Test system concept CE65 carrier card **APTS SF** carrier card USB to PC **APTS** USB to PC APTS OA carrier card **DPTS** carrier To scope card Proximity cards have Readout identical PCB layout, but To scope different components

Carrier board layout

### Plans for future R&D in Trieste

#### Future activities within ITS3

- Continue with ALPIDE DUTs preparation and lab-testing

- Test and characterization of MLR1 test structures

- Development characterization setup for bent MLR1 structures

- Moving to larger-size chips for bending and interconnections

### Long term tentative plans for EIC-specific development

- Characterization of next submissions after fork-off

- Development of test setups for EIC-specific chips

- Bending and interconnections at EIC target radius/dimensions