# Preliminary Roman Pot DAQ considerations

Outline:

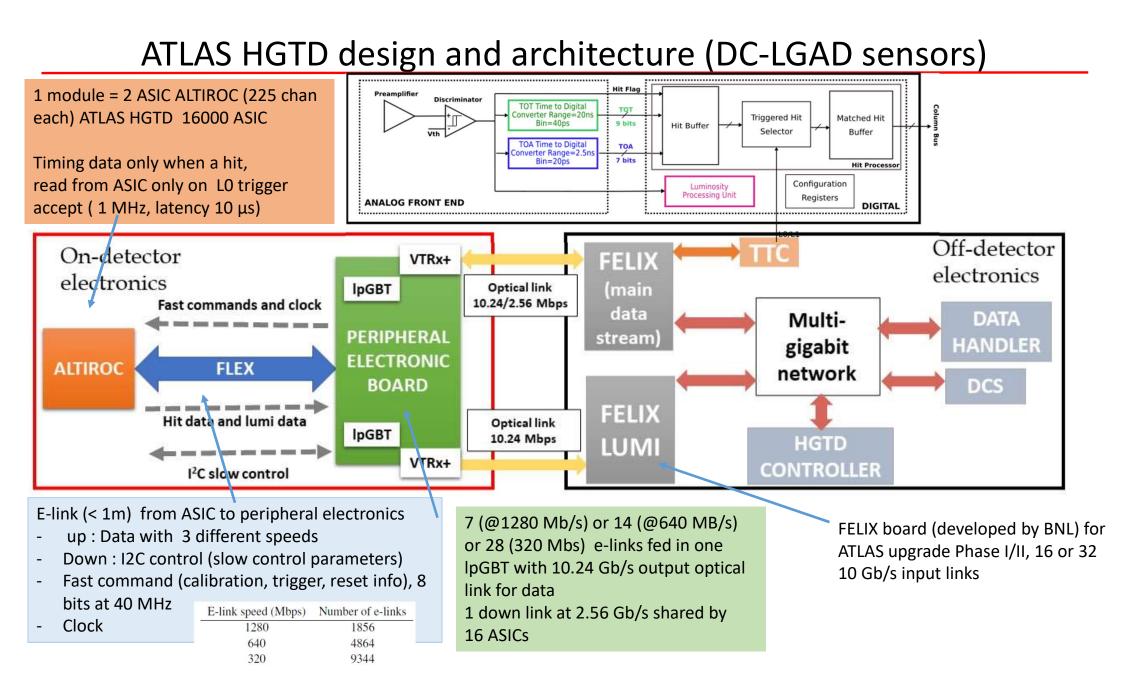

- 1) The ATLAS readout system for timing detector (HGTD) using DC LGAD

- 2) Key numbers / extrapolation for Roman Pots at EIC

ATLAS ASIC occupancy from a few per mil to 10 % depending on radius

|                                                 | Command   | Bit neld | Description                 |

|-------------------------------------------------|-----------|----------|-----------------------------|

| ATLAS average event size from 150 to 250 kBytes | IDLE      | 10101100 | IDLE frame                  |

| C ,                                             | TRIGGER   | 10110010 | L0 or L1 trigger            |

|                                                 | BCR       | 10011001 | Bunch Counter Reset         |

| ATLAS Data format :                             | TRIGBCR   | 01101001 | Trigger and BCR             |

|                                                 | CAL       | 11010100 | Calibration Pulse           |

|                                                 | GBRST     | 11001010 | Global Reset                |

| 8 bits fast commands (@ 40 MHz)                 | SYNCLUMI  | 01100110 | Synchronize luminosity stre |

|                                                 | SETTRIGID | 01010011 | Set Trigger ID              |

|                                                 | TRIGID    | 01xxxx01 | Trigger ID                  |

#### Data format : 24 bits word with 8b10b encoding.

| 23 22 | 21    | 1.03  | 16 15    |       | 7   | 6     | 1 0 |          |                         |

|-------|-------|-------|----------|-------|-----|-------|-----|----------|-------------------------|

| Туре  | E     | rors  |          | BCID  |     | L0/L1 | PB  | Header   |                         |

| 23    | 20    | 19    | 16 15 14 |       | 7   | 6     | 0   |          | 16 bits of timing       |

| C     | OL    | ROW   | CRC      | TOT   |     | TOA   |     | Hit word | information / per pixel |

| 23    |       |       | 16 15    |       | 8 7 |       | 0   |          | mormation, per pixer    |

|       | bx111 | 10000 |          | #hits |     | CRC8  |     | Trailer  |                         |

Slow control parameters through I2C 960 with 8 bits registers :

- 4 per pixels  $\rightarrow$  900 registers

- 60 for global slow control

| Command   | Bit field | Description                   |

|-----------|-----------|-------------------------------|

| IDLE      | 10101100  | IDLE frame                    |

| TRIGGER   | 10110010  | L0 or L1 trigger              |

| BCR       | 10011001  | Bunch Counter Reset           |

| TRIGBCR   | 01101001  | Trigger and BCR               |

| CAL       | 11010100  | Calibration Pulse             |

| GBRST     | 11001010  | Global Reset                  |

| SYNCLUMI  | 01100110  | Synchronize luminosity stream |

| SETTRIGID | 01010011  | Set Trigger ID                |

| TRIGID    | 01xxxx01  | Trigger ID                    |

|           |           |                               |

Table 2: Fast commands

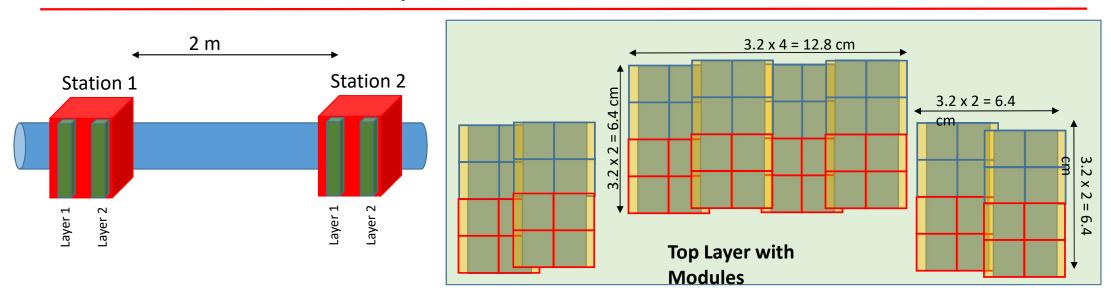

### Roman pots detector

#### Baseline for detector

- Two stations with two layers and 0.5x0.5 mm2 pixels of AC-LGAD (charge sharing)

- In each layer : 32 quad modules per layers, 1 module is 4 ASICs  $\rightarrow$  128 ASIC per layer

- Total : 128 Modules / 512 ASICs (524 288 Channels)

- ASIC size : 1.6 x 1.8 cm<sup>2</sup> with 1024 channels (32x32)

## **Extrapolation to EIC Roman Pots readout**

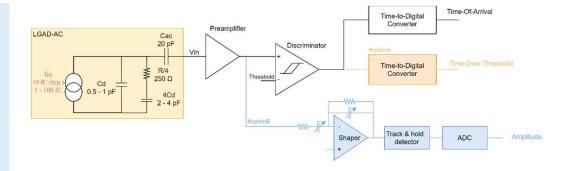

Two architectures for the Front End under study :

- ATLAS HGTD like (option A) with TOA + TOT.

As needed to read neighbour pixels of the hit one discri threshold might not low enough and deteriorate position resolution.

- ASC measurements instead of TOT measurement but need to control power dissipation. Gated ADC and logic to read the 8 neighbours

Proto expected to be submitted end 2021/early 2022

#### **Trigger-less acquisition**

Expected vey low occupancy : < 30 hits/pixel/s (assume threshold at >5 sigma of noise)

(not including the neighbours, so a factor of  $\times$ 9 should be accounted for in the readout, especially when using ADC

If 32 bits data for a hit

$\rightarrow$

$\rightarrow$  data rate is 30x32\*1024=~1 Mbits/s per ASIC or 9 Mbits/s with neighbours

128 Mbits/s per layer or 1152 Mbits/s (Still to validated by simulation)

$\rightarrow$  Total detector data rate 512 Mbits /s 4608 Mbits/s

Slow control information : similar numbers of parameters as ATLAS

Data transmission from ASIC to DAQ

- No radiation hardness needed in EIC and low ASIC rate with respect to ATLAS : using IpGBT is not well suited

- Commercial concentrator or custom FPGA board ? One board per layer would have do deal with 128 ASICs and < 200 Mbytes/s of data</li>