# Readout of CyMBaL tracker for Athena@EIC

Damien Neyret, Irakli Mandjavidze on behalf of Saclay group

> Athena DAQ WG meeting Sep 30, 2021

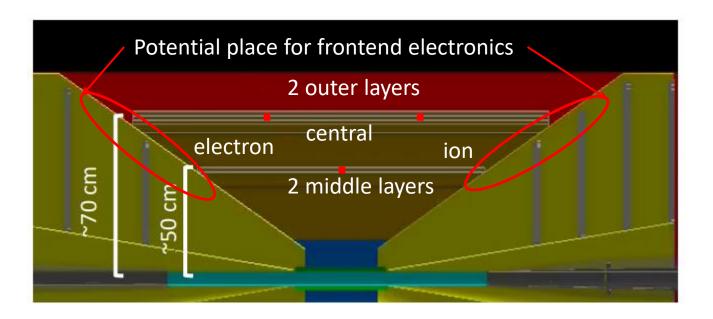

### CyMBaL (CYlindrical Micromegas BArrel Layers) tracker for Athena@EIC

#### • 4 layers

- $\rightarrow$  2 middle and 2 outer

- $\rightarrow$  2D strip readout

- Z + C strips per layer

- $\rightarrow$  Middle layers built in 2 modules along Z (beam) axis: electron side and ion side

- $\rightarrow$  Outer layers built in 3 modules along Z (beam) axis: electron side, central and ion side

- On-going study on how to connect central modules to electronics (flex cables?)

- Number of channels

- $\rightarrow$  1.45 mm pitch: 66 000 strips

- 28K Z-strips & 39K C-strips

- Assume as a baseline

- May vary though

#### • Environment

- $\rightarrow$  Scarce space for electronics

- Can nevertheless be placed on both sides

- $\rightarrow$  Magnetic field

- $\rightarrow$  Material budget restrictions

- Impact on cooling

- $\rightarrow$  Radiation?

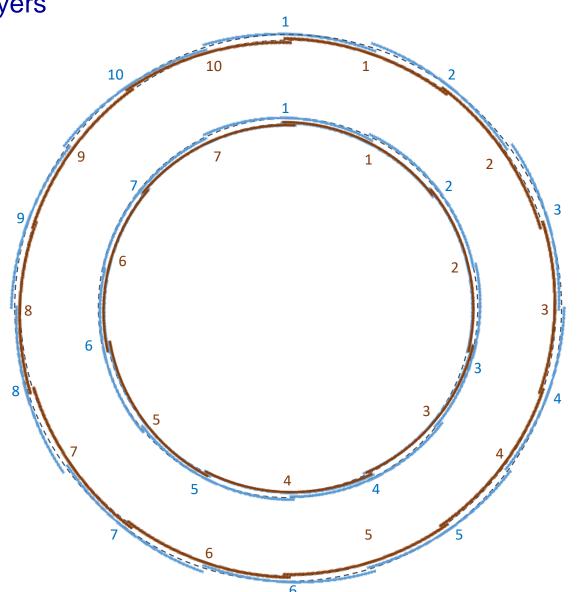

### CyMBaL tracker for Athena@EIC

- Same base detector to assemble middle and outer layers

- $\rightarrow$  Curved according to layer radius

- $\rightarrow$  Active area: ~650 mm length x ~465 mm width

- 1.45 mm pitch

- 448 "C" strips + 320 "Z" strips

- Two middle layers

- $\rightarrow$  2 x 7 base detectors each

- $\rightarrow$  Radial distance 15 mm

- Two outer layers

- $\rightarrow$  3 x 10 base detectors each

- $\rightarrow$  Radial distance 15 mm

- Avoid dead zones

- $\rightarrow$  Tilted detectors ensuring overlap

damien.nayret@cea.fr irakli.mandjavidze@cea.fr

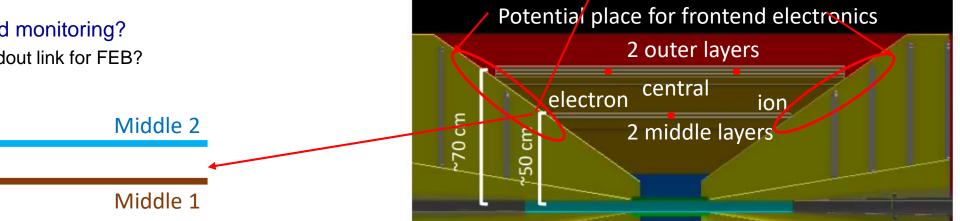

### Space for CyMBaL module electronics

### • Place FEBs in the conical space between barrel and end-cup

Middle 2

FEB

- $\rightarrow$  Fixed on structure maintaining CyMBaL tracker

- Not shown

- $\rightarrow$  Probably will be crowded by other equipment and services

#### $\rightarrow$ Proper to CyMBaL

- Readout link: data, clock, synchronization

- LV, HV, gas

- Cooling?

- Slow control and monitoring?

- Through readout link for FEB?

FEB

FEB

447 mm

224 Mm

FEB.

Widdle J

‡- FEB length given for illustration only

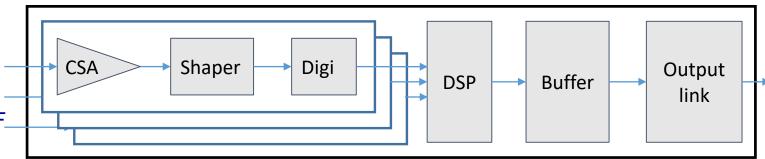

### CyMBaL tracker frontend

- FEBs based on multi-channel MPGD ASICs

- $\rightarrow$  Compatible with streaming readout

- $\rightarrow$  Typical characteristics

- Gain: 10 down to 4 mV/fC

- Peaking time: 75 to 300 ns

- Detector capacitance: up to 400 pF.

- 10-12 bit ADC and/or 10-bit TDC

- $\rightarrow$  On-chip zero suppression

- Possibly with common mode noise subtraction

- Sampling ZS: signal shape around ToT

- Peak finding ZS: amplitude, time and ToT

- Existing ASICs

- $\rightarrow$  32-channel Sampa: sampling

- $\rightarrow$  64-channel VMM3a: peak finding

- Next generation ASIC

- $\rightarrow$  On-going common initiative between Brazilian institutes (Sampa) and Irfu (AGET, Dream)

- Most probably a 64-channel sampling ASIC with common mode correction

- See for example: <u>https://indico.cern.ch/event/1040996/contributions/4402636/</u>

### CyMBaL tracker frontend (cont.)

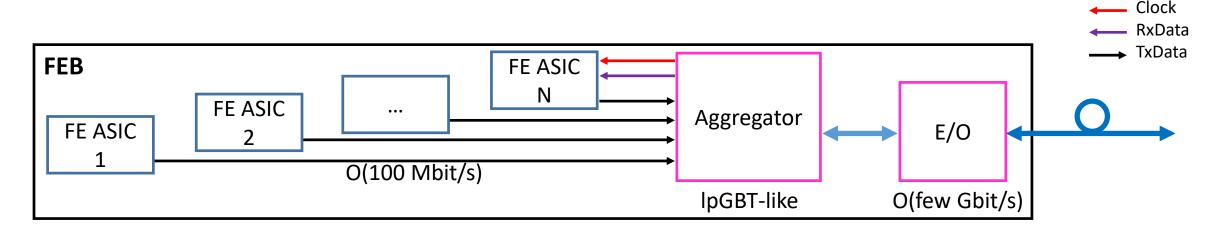

#### • LHC-like frontend organization?

- $\rightarrow$  A bi-directional link for clock, synchronization (run control), data, slow control

- $\rightarrow$  Assumes existence of IpGBT-like aggregator ASIC or requires a new development

- Point to point connections between frontend ASICs and an aggregator ASIC

- Downstream path is only partially shown

It is not clear if there will be a central (Athena, EIC) group responsible for aggregation / frontend link

### CyMBaL tracker frontend data rate: sampling readout

- Sampling ASIC with 12-bit sample per channel

- Signal shape ZS

- $\rightarrow$  500 ns readout window when signal is above threshold

### • 32-channel ASIC (e.g. Sampa) and 256-channel FEB (e.g. sPhenix FEE for TPC)

| Chan<br>kHz | nel rate  | Sampling<br>MSPS | Number of samples | 32-chanel ASIC<br>Mbit/s | 256-chanel FEB<br>Gbit/s | Remarks                                  |  |

|-------------|-----------|------------------|-------------------|--------------------------|--------------------------|------------------------------------------|--|

| 2           | (physics) |                  |                   | 19                       | 0.16                     | 5.40 Chit/s specestics link univertified |  |

| 10          | (safe)    | 20               | 10                | 92                       | 0.75                     | 5-10 Gbit/s aggregation link unjustified |  |

| 50          | (Clas12)  |                  |                   | 460                      | 3.7                      | 5-10 Gbit/s aggregation link justified   |  |

#### • New development: 64-channel ASIC and 512 FEB

| Chan<br>kHz | nel rate   | Sampling<br>MSPS | Number of samples |  |

|-------------|------------|------------------|-------------------|--|

| 2 (physics) |            |                  |                   |  |

| 10          | (safe)     | 50               | 25                |  |

| 50          | (Clas12)   |                  |                   |  |

|             | 30/09/2021 |                  |                   |  |

| 64-chanel ASIC<br>Mbit/s | 512-chanel FEB<br>Gbit/s |  |

|--------------------------|--------------------------|--|

| 46                       | 0.4                      |  |

| 230                      | 1.9                      |  |

| 1 150                    | 9.5                      |  |

| Remarks         |                            |

|-----------------|----------------------------|

| 5-10 Gbit/s ag  | gregation link unjustified |

| 5 Gbit/s aggre  | gation link is enough      |

| 20 Gbit/s aggre | egation link needed        |

### CyMBaL tracker frontend data rate: peak-finding readout

- Peak-finding ASIC

- ZS with time-amplitude readout

- $\rightarrow$  Assume 12-bit timing, 8-bit ToT and 12-bit amplitude

- 64-channel ASIC (e.g. VMM3a) and 512-channel FEB (e.g. Atlas NSW FEM8)

$\rightarrow$  Or a new development

| Channel rate<br>kHz |           | 64-chanel ASIC<br>Mbit/s | 512-chanel FEB<br>Gbit/s | Remarks                                  |

|---------------------|-----------|--------------------------|--------------------------|------------------------------------------|

| 2                   | (physics) | 5                        | 0.04                     | 5 10 Chit/a correction link univertified |

| 10                  | (safe)    | 25                       | 0.2                      | 5-10 Gbit/s aggregation link unjustified |

| 50                  | (Clas12)  | 125                      | 1                        | 2 Gbit/s aggregation link is enough      |

#### Good knowledge of channel occupancies (physics, background, noise) is important

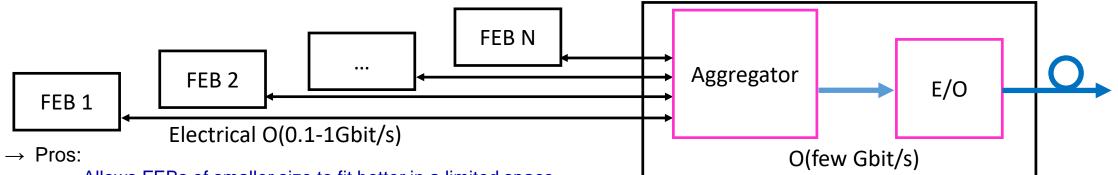

### A question on aggregation: local concentrator card

- High speed FE-BE connections assume enough aggregated bandwidth to justify multi-Gbit/s links

- $\rightarrow$  5-10 Gbit/s or higher

- $\rightarrow\,$  Especially if the use of IpGBT for EIC is envisaged

- Is a local concentrator card needed?

- $\rightarrow$  Upstream: only data aggregation, no data treatment

- $\rightarrow\,$  Downstream: clock, synchronization, slow control

Aggregator unit in close vicinity to FEBs

- Allows FEBs of smaller size to fit better in a limited space

- e.g.256-channel or even 128-channel FEBs rather than 512-channel FEBs

- Potentially lower power consumption

- Could be used by several sub-detectors

- $\rightarrow$  Cons:

- More boards to produce and maintain

- More complex communication protocol between FEBs and aggregator unit

If there is an interest, should there be a central group to define/design the aggregator?

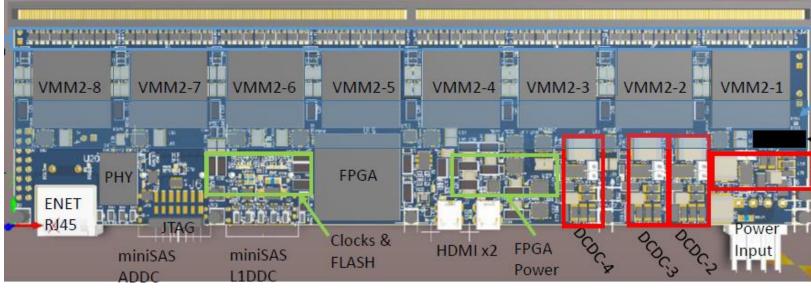

### CyMBaL tracker readout: 64-channel ASIC and 512-channel FEB

- Assume integration of 8 64-channel VMM3a or next generation 50 MSPS chips

- System with 66K channels

- $\rightarrow$  1 056 ASICs

- $\rightarrow$  132 FEBs

- $\rightarrow$  With a backend link per FEB: 5 32-link Felix equivalents

- Assume 10 kHz channel occupancy, total data bandwidth produced by frontends

- $\rightarrow$  Signal shape readout: ~250 Gbit/s

- $\rightarrow$  Time-amplitude readout: ~30 Gbit/s

8 VMM3a size chips can fit to 220 mm long FEB Compatible with example on page 4

Assuming 8 double-row connectors: 0.8 mm pitch

30/09/2021

Illustration: Atlas FEM8 prototype with 8 VMM3a: 215 x ~60

damien.nayret@cea.fr irakli.mandjavidze@cea.fr

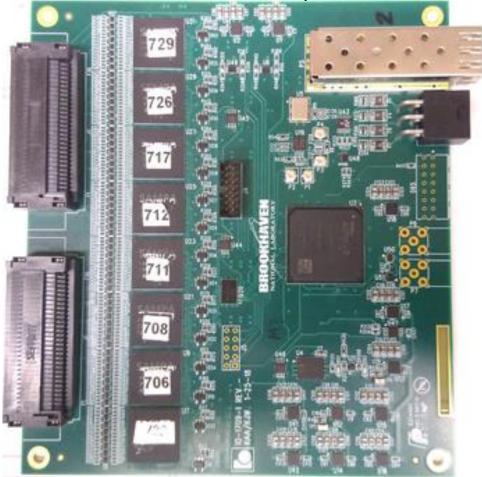

## CyMBaL tracker readout: 32-channel ASIC and 256-channel FEB

- Assume integration of 8 32-channel Sampa or next generation 50 MSPS chips

- System with 66K channels

- $\rightarrow$  2 112 ASICs

- $\rightarrow$  264 FEBs

- $\rightarrow$  With a backend link per FEB: 9 32-link Felix equivalents

- Assume 10 kHz channel occupancy, total data bandwidth produced by frontends

- $\rightarrow$  Sampa @ 20 MSPS: ~100 Gbit/s

- $\rightarrow$  New ASIC @ 50 MSPS: ~250 Gbit/s

8 Sampa size chips can fit to 150 mm long FEB (Max size allowed to fit all 264 FEBs on tracker periphery)

Assuming the use of 8 double-row connectors: 0.8 mm pitch

#### Illustration: sPhenix TPC FEE with 8 Sampas: 140 x 140

# CyMBaL tracker costing

- Assume 66K-channel system

- Assume 64-channel detector cables, 64-channel ASIC and 512-channel FEB

- $\rightarrow$  A FE-BE link per FEB

- $\rightarrow$  Cooling is not taken into account

| ltem            | Quantity | Unit price<br>\$ | Total price<br>k\$ |

|-----------------|----------|------------------|--------------------|

| Short FE cables | 816      | 50               | 40.8               |

| Long FE cables  | 240      | 100              | 24                 |

| ASIC            | 1 056    | 50               | 58.8               |

| FEB             | 132      | 1 000            | 132                |

| FE-BE link      | 132      | 100              | 13.2               |

| Backend         | 6        | 7 000            | 42                 |

| BE servers      | 6        | 7 000            | 42                 |

| LV              | 1        | 7 000            | 7                  |

#### • Total: \$355k: \$5.5/channel

- $\rightarrow$  Very rough estimation, expect more \$8/channel

- $\rightarrow$  More likely \$10/channel if 32-channel cables, 32-channel ASICs and 256-channel FEBs

### Open questions on common services

- The frontend backend communication links

- $\rightarrow$  If IpGBT is considered, it has to be associated with an optical transceiver

- VTRX+ with one 2.5 Gbit/s down-link and four 10 (5) Gbit/s up-links

- Part of the Versatile Link+ elaborated by CERN

- Will the Versatile Link+ from CERN available for EIC?

- IpGBT and VTRX+ devices, and very importantly support

- Is the use of VTRX+ justified?

- Bandwidth, radiation

- $\rightarrow$  Can a commercial optical transceiver be used with IpGBT?

- Protocol and radiation

- Atlas RPC collaboration considers replacement of VTRX+ by a commercial SFP+ optical transceiver

- → A possible candidate: Avago AFBR-709SMZ Compatible Module SFP+ 10GBASE-SR 850nm 300m DOM LC MMF from FS

- 10 Gbit/s with FEC5

- Radiation levels need to be understood

- $\rightarrow$  TID, neutrons and SEE (latch-up, SEU)

- $\rightarrow$  At what extent commercial components can be used

- Magnetic field

- $\rightarrow$  Qualified power regulators

#### Will there be a central group(s) taking care of these questions?

## Summary

- Not yet a complete knowledge of Micromegas cylindrical barrel tracker environment

- $\rightarrow$  Construction, occupancy, space, radiation

- $\rightarrow$  Figures below to be taken with caution

- Assuming 66K channel tracker as a baseline

- $\rightarrow$  @ 10 kHz channel hit rate front-end link bandwidth at least factor 5 above expected rates from physics

- Signal shape readout at 50 MSPS: ~250 Gbit/s

- Time-amplitude readout: ~30 Gbit/s

- Further data reduction could / must be done either in FEP (if any) or in the on-line filtering farm

- Assuming 64-channel MPGD ASIC and 512-channel FEB

- $\rightarrow$  1 056 ASICs

- $\rightarrow$  132 FEBs

- $\rightarrow$  6 Felix equivalents with 32-links

- Open questions on central support for

- $\rightarrow$  Common FE-BE link

- $\rightarrow$  FE aggregation design of a common aggregator unit

- $\rightarrow$  Precision clock distribution validation metrics

- $\rightarrow$  Magnetic field and radiation compatible components