## Sensor Design Reports and EIC Large Area Ideas

31/01/21

## Sensor Design Reports

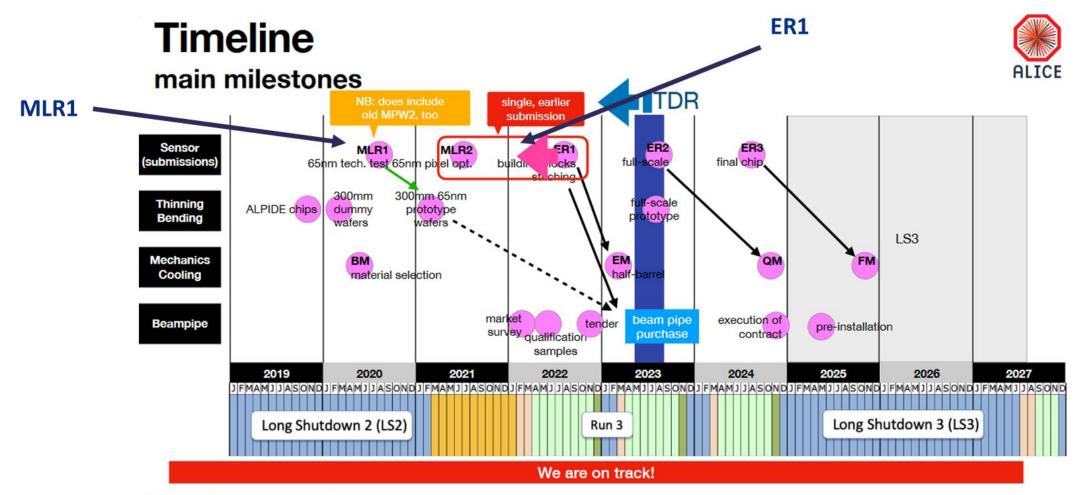

## **Timeline**

BM: breadboard module, EM: engineering module, QM: qualification module, FM: final module

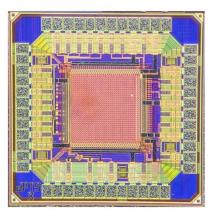

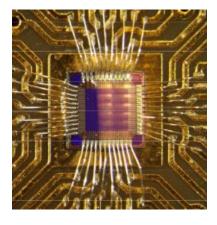

## **MLR1 Overview - Chips**

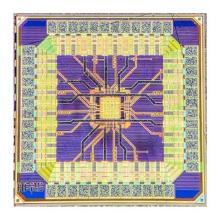

APTS (CERN)

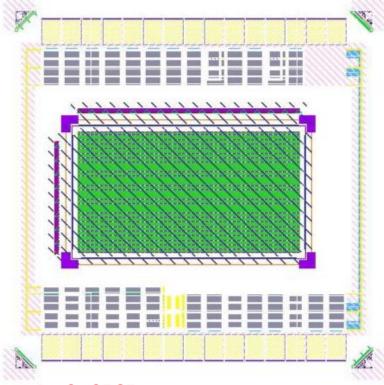

CE65 (IPHC)

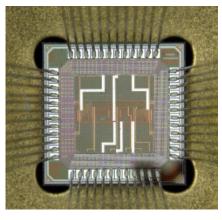

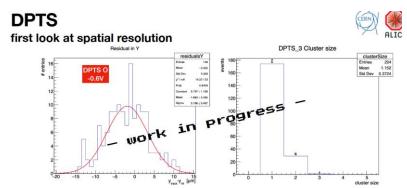

**DPTS (CERN)**

Bandgap (NIKHEF)

RO (CPPM)

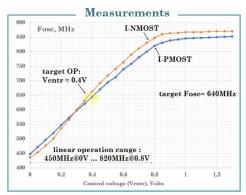

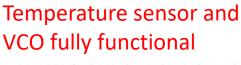

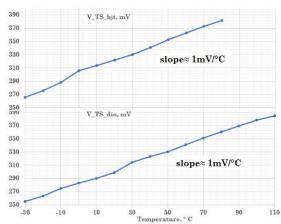

VCO (NIKHEF)

Pixels (DESY)

CML (RAL)

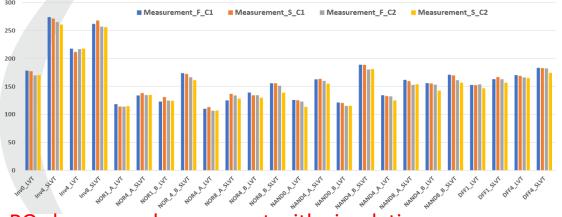

## **MLR1 Overview - Testing**

- These are residuals, i.e. some 3µm need to be substracted quadratically still

- resulting O(4 μm)

## DPTS and APTS both in beam test

RO shows good agreement with simulation. Irradiation planned.

CML driver fully functional. More advanced test system planned.

- Also many, many more.

Transistor test

structures, pixels, etc,

etc...

- https://indico.cern.ch/eve nt/1091910/

## **ER1 Design Activity**

See most recent ITS3 WP2 plenary for more detail (https://indi co.cern.ch/ event/1117 024/contrib utions/4691 459/attach ments/2380 633/406)

Chips for ER1: still to be updated and mapped into floor-plan

| Design            | Purpose                                                                 | Institute                          | # of test sites | Comments                                                 | 1   |

|-------------------|-------------------------------------------------------------------------|------------------------------------|-----------------|----------------------------------------------------------|-----|

| MOSS              | stitched sensor prototype develop stitching know-how, more conservative | INFN, IPHC, NIKHEF,                | -               | 1D stitching                                             |     |

|                   | Focus on technology options, power distribution, signal routing, yield  | CERN                               |                 | Matrix as simple as possible                             |     |

| MOST              | Stitched sensor prototype, develop stitching know-how, more aggressive  | NIKHEF, IPHC,<br>Heidelberg, CERN, |                 | Many parts in common with MOSS                           |     |

|                   | Study yield with high density layout parts and fine power segmentaton   |                                    | -               |                                                          |     |

|                   | Low power and transmission of timing information over long distance     | INFN                               |                 |                                                          |     |

| H2M               | Hybrid to Monolithic                                                    | DESY and CERN                      | 2               |                                                          |     |

|                   | Investigate MAPS and architectures in non-stitched sensor               |                                    |                 |                                                          |     |

| CE65++            | Pixel optimization vehicle                                              | IPHC                               | tbd             |                                                          |     |

|                   | Focus on optimizing pixels and front-end                                |                                    |                 |                                                          |     |

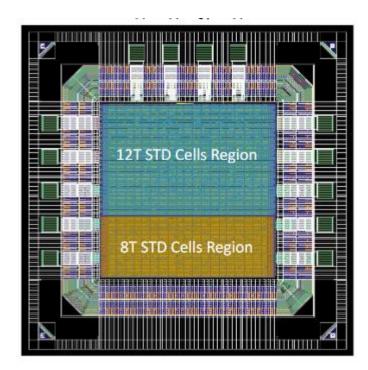

| SEU chips         | Prototype with memories and flops                                       | INFN Bari                          | 2               |                                                          |     |

|                   | Measure SEE cross-sections (SEL, SEU)                                   |                                    |                 |                                                          |     |

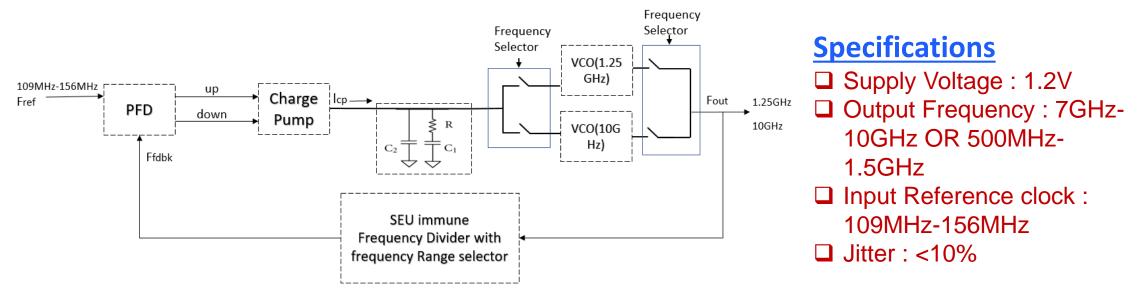

| PLL NIKHEF        | First step in high speed transmitter                                    | NIKHEF                             | 1               | High speed transmission                                  |     |

| Dillebuffer       | First stor in high speed to speed the                                   | DAL                                |                 | High accord to consider                                  |     |

| PLL+buffer        | First step in high speed transmitter                                    | RAL                                | 1               | righ speed transmission                                  | 1   |

| Pixel test DESY   | Pixel sensor and front end prototype                                    | DESY                               | 1               | λ                                                        | ٠,  |

| Pixel test SLAC   | Pixel matrix prototype                                                  | SLAC                               | 1               | finer in                                                 | SUL |

| APTS              | Analog pixel test structure                                             | IPHC and CERN                      | thd             | aren.                                                    |     |

| APIS              | Analog pixel test structure                                             | IPHC and CERN                      | tba             | - pe wee                                                 |     |

| DPTS              | Digital pixel test structure                                            | CERN                               | tbd             | 10, 00,                                                  |     |

| TTS1-5            | Transistor test structures                                              | CERN                               | 10              | ced o                                                    |     |

|                   |                                                                         |                                    |                 | High speed transmission  To be refined  Based on measure |     |

| ADC prototype     | Desired function                                                        | not covered                        |                 | generated from DAC ?                                     |     |

| Supply regulation |                                                                         | not covered                        |                 | Interest from several corners                            |     |

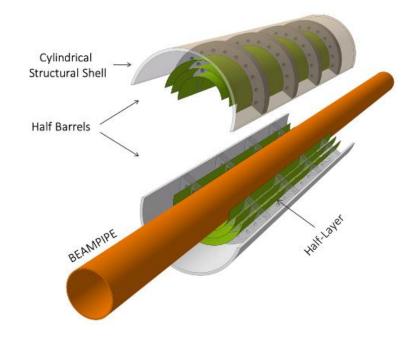

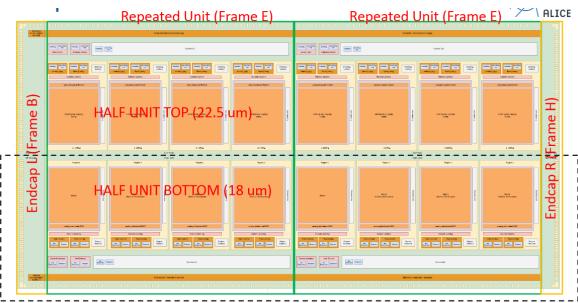

## ER1 Design Activity – MOSS and MOST

#### **Primary Goals**

Learn Stitching to make a particle detector

Interconnect power and signals on wafer scale design

Learn about yield and DFM

Study power, leakage, spread, noise, speed

- Investigate yield when local density is preserved

- Global power domains over full chip (Digital/Analog)

- · higher granularity in power gating in case of a defect of

- analog (rows of 4 pixels)

- · digital (half columns)

- PWELL tied to ground

- reverse sensor biasing achieved by higher power supply

- Immediate transfer of hit data to the periphery (bottom endcap, 4 CML outputs)

- event-driven asynchronous readout (no strobing) over long distance

- serial binary address transmission for this implementation

## **ER1 Design Activity – Other Chips**

INFN: SEU test chip

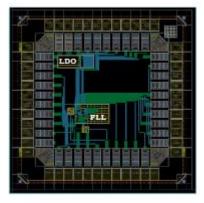

NIKHEF: LDO, PLL for serialiser

## ER1 Design Activity – "EIC" Groups

#### RAL

- Design of PLL with dual frequency operation: 10GHz or 1.25GHz.

- Frequency selection switch

- Range of output frequencies are possible by varying the input reference frequency.

#### LBNL/Brookhaven

- NDAs signed, PDK available

- Discussing best way to contribute

- Effort complicated by Continuing Resolution

# Large Area Sensor – First Thoughts

## Introduction

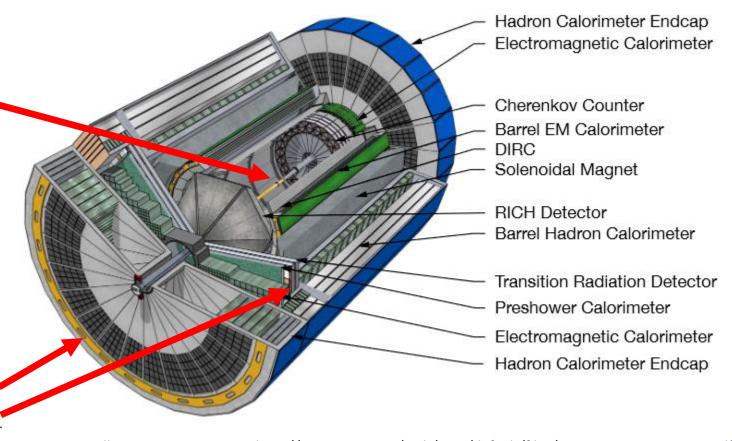

EIC will require 2 sensors:

Vertex chip: Likely to be identical to the ALICE ITS3<sup>4</sup> detector

Stave and disc chip: A large silicon area needs to be covered and the yield of the wafer-scale chip is likely to be too low for this. Therefore a chip functionally similar to the vertex device, but with a different layout, will be needed.

Goal of this presentation is to discuss technical and organisational paths towards this

## **Vertex Chip**

- "Top-level" idea for the vertex chip is fairly simple (even if technically complex!)

- ITS3 chip likely to be suitable. Ideal would be to use this. Development already underway, several EIC groups engaged in working with ITS3.

- Different barrel arrangement may be needed.

- Remaining issues to resolve:

- Agreement for the supply of this device

- Agreement on required EIC financial contribution to ALICE

- Mechanical arrangement

## Stave/Disc Chip

- "Top-level" plan is more complex than for the vertex chip.

- 3 main issues are:

- How to achieve the required yield?

- What technical configuration do we want for this chip?

- What design path will we follow?

- Several options in following slides. And also must not forget the option that yield is good and wafer scale chip could be used for both!

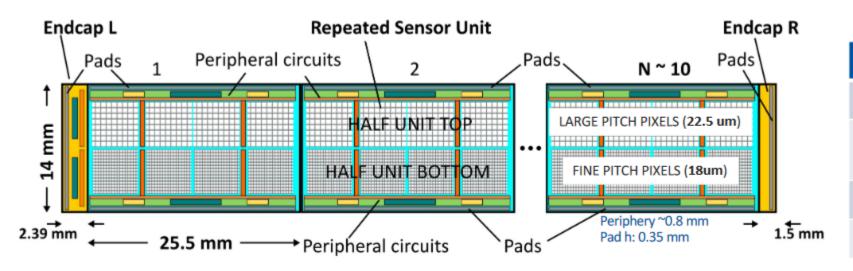

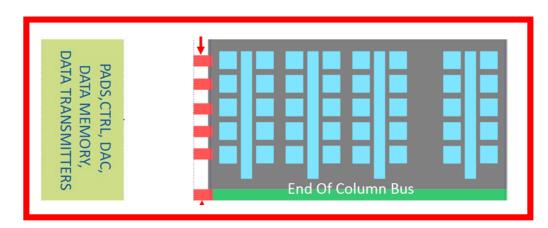

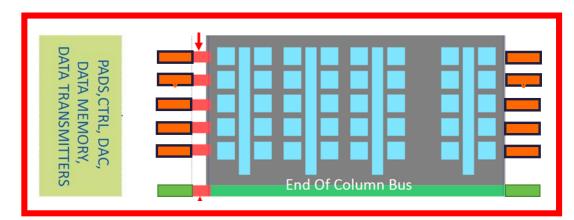

## Stave/Disc Chip - Option A

- Simplest option is to just adjust the stitching plan for our requirements

- Result would be small chips like this

- This leaves a dead area and construction would have to be something like this

- Same as vertex chip plus...

- Technical feasibility

- Agreement with ITS3 to support this

- Timeline and cost

- Mechanical arrangement

- **Physics Implications**

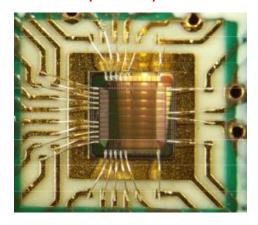

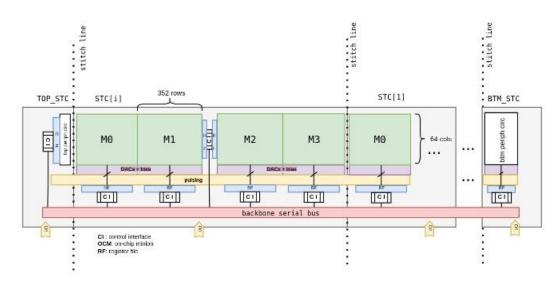

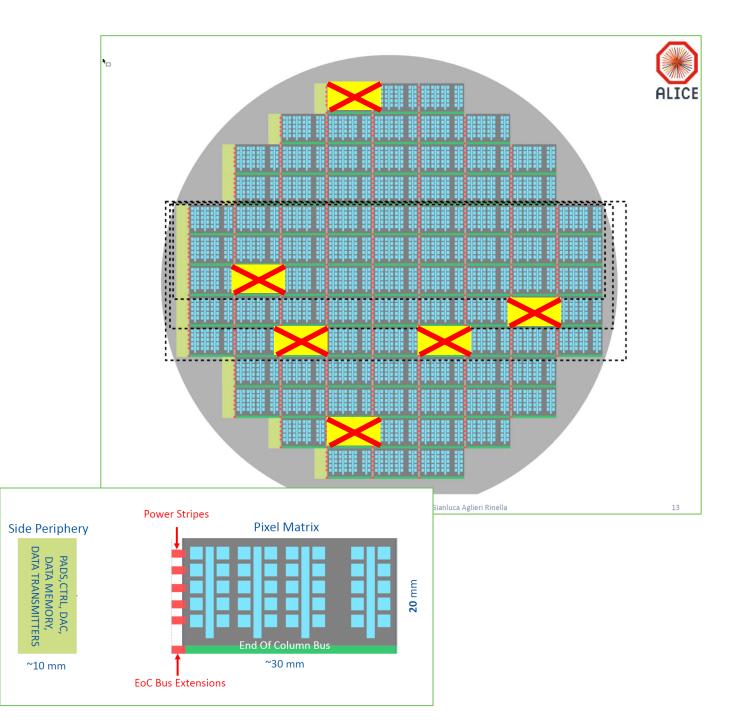

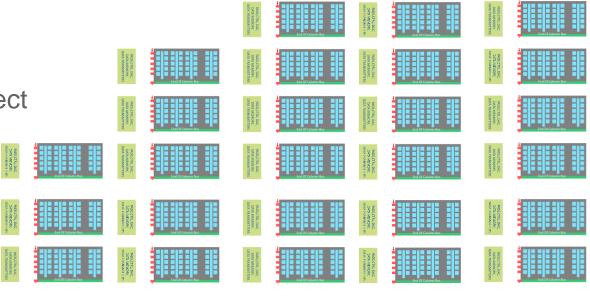

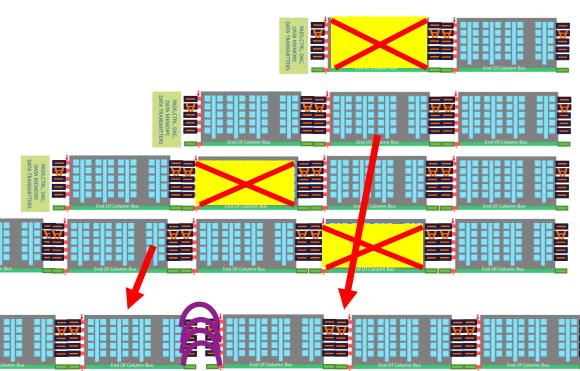

## Stave/Disc Chip - Option B

- Adjust design to produce a separate "periphery" and "pixel" block

- Pixel blocks could transmit data through from others to reach periphery blocks. All could be wire bonded together.

- Reticle and wafer would look like this

- Idea would then be to assemble wire-bonded staves like this with limited dead area

- Yield could be improved by wafer probing to select only good pixel blocks for staves

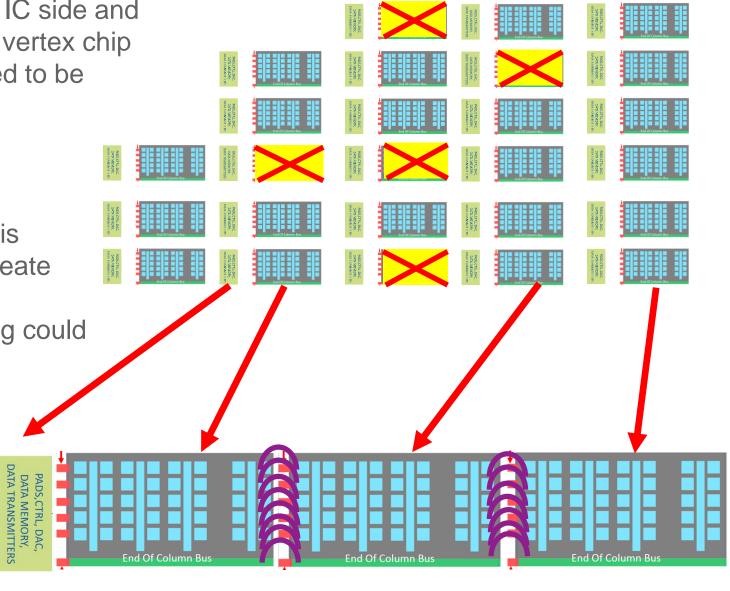

## Stave/Disc Chip - Option B

- This would require design work on the IC side and access to the design databases of the vertex chip

- Wire bond pads and drivers would need to be added in the pixel blocks

- Remaining issues to resolve:

- Agreement with ITS3 to support this

- Define blocks we would have to create

- Determine foundry access

- Mechanical arrangement. How long could staves be? Still some dead area?

- Physics Implications

- Timeline

- Cost

## Stave/Disc Chip - Option C

- Similar to option B, but make the connections on the wafer between "pixel" stitching blocks

- Makes greater use of the stitching technology and reduces wire bonding

- Probing and dicing is more complex

- Would still need to add bond pads for those chips that need them, and for probing

- Remaining issues to resolve:

- Same as option B

- How to detect power-ground shorts?

- More complex dicing needed

## Stave/Disc Chip - Option D

- Do not base stave/disc device on vertex chip. Produce a completely separate design.

- Requires no ITS3 data, but vastly increased design effort and silicon cost.

- Remaining issues to resolve:

- Define specification

- Determine foundry access for production

- Mechanical arrangement. How long could staves be? Still some dead area?

- Timeline, cost and physics implications