### Getting involved in the ITS3 MLR1 testing campaign

#### Giacomo Contin Università di Trieste and INFN Sezione di Trieste EIC Silicon Consortium meeting – Jan 27<sup>th</sup> 2022

## How to get involved in the ITS3 MLR1 testing

- Requirements to get involved in the MLR1 and future ITS3 chips;

- A longer commitment to ITS3 beyond the testing phase is preferable

- Training is not possible upon request, joining in person an experienced group is preferables

- Local supervision at the Institute: students/unexperienced researchers have to be locally supervised, since no supervision from the ITS3 team is available

- Constant support from CERN team / experienced teams is not guaranteed

- ... please let us know if these requirement sound reasonable for your participation

- Suggested path to actively join the activities:

- 1. Inform/negotiate with Alex Kluge and Magnus Mager at the institutional level

- 2. Inform Miko Suljic and Sergey Senhiukov at the technical level

- Join ITS3 WP3 e-group to access <a href="https://twiki.cern.ch/twiki/bin/viewauth/ALICE/ITS3WP3">https://twiki.cern.ch/twiki/bin/viewauth/ALICE/ITS3WP3</a> (requires ALICE membership)

- Express interest / request test system or access to data

- 3. Start learning independently from points 1) and 2) outcome

- See how in the next slides

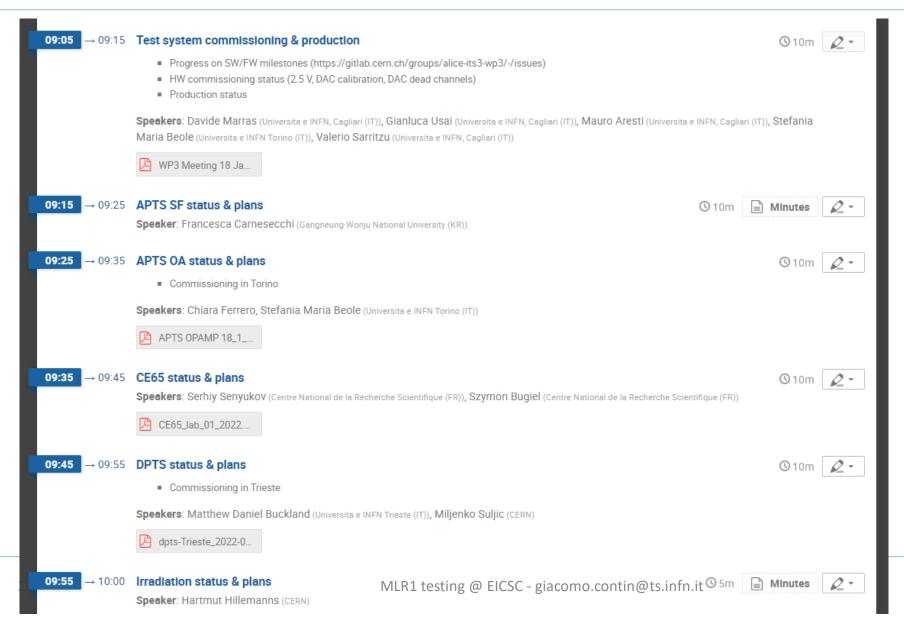

# MLR1 testing /1: test system and chip testing

#### Active groups:

# Test system design/production

- Cagliari

- Torino

- Strasbourg IPHC

- Trieste

- CERN

#### Chip tests:

- CERN

- Torino

- Strasbourg IPHC

- Trieste

# MLR1 testing /2 : beam test data analysis

#### Data available from:

- DESY September 2021 MLR1, Carbon foam, W-ALPIDE

- NPI September 2021 DPTS SEU cross-section

- NPI October 2021 DPTS irradiation & SEU cross-section

- PS October 2021 MLR1

- SPS November 2021 MLR1

- DESY December 2021 MLR1

- NPI December 2021 DPTS irradiation & SEU cross-section

#### Active groups in beam test data analysis:

- GSI

- NIKHEF

- Both these groups joined ITS3 recently

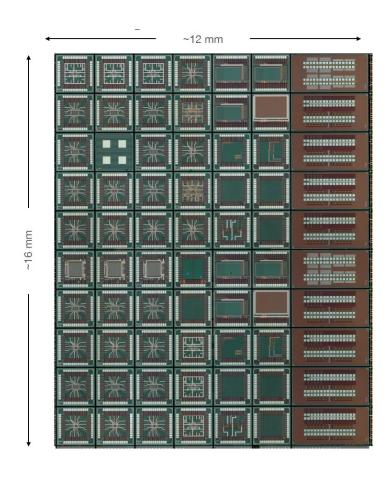

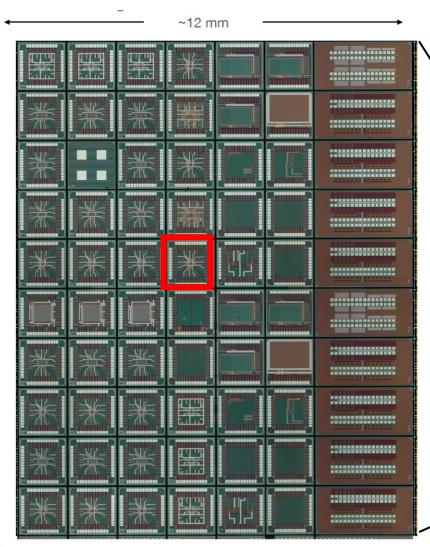

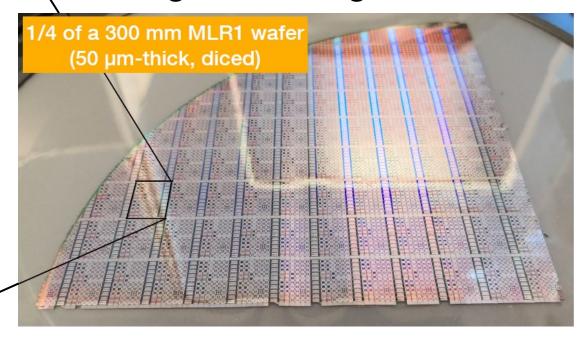

### MLR1 reticle: 60 chips (+ 10 transistor test structures)

- Pixel test structures

- Pixel matrices

- Radiation test structures

- Analogue building blocks

### APTS, CE65, DPTS

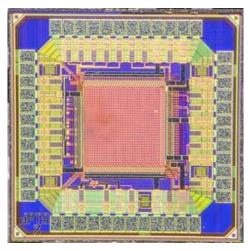

#### **APTS**

- Most "simple" chip

- 4x4 pixel matrix

- 10, 15, 20, 25 μm pitches

- Different pixel and amplifier architectures

- Direct analogue readout of all 16 pixels

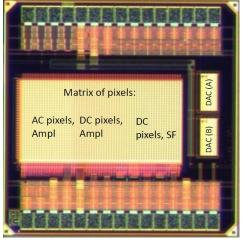

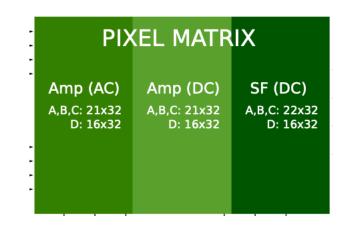

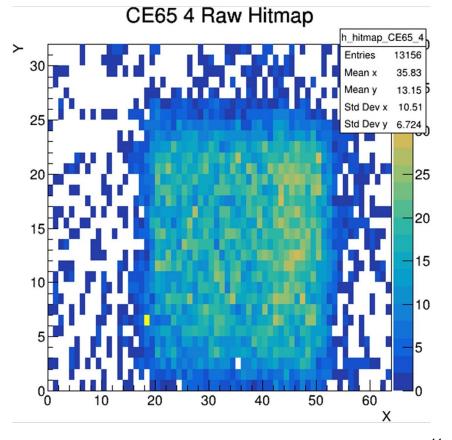

**CE65**

- "Large" area chip with analogue rolling shutter readout

- 64x32 pixel matrix

- 15 μm pitch

- 3 pixel architectures

- 2 currents DACs on same die

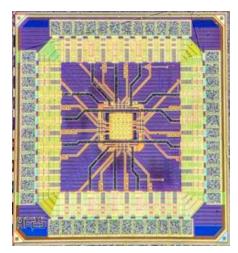

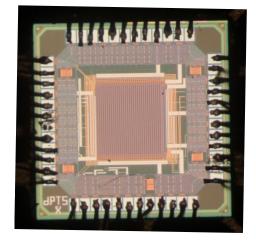

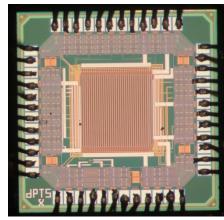

**DPTS**

- Most "complicated" chip

- 32x32 pixel matrix

- 15 μm pitch

- Asynchronous digital readout

# Chip variant phase space

| #  | Pitch<br>(um) | Buffer | Coupling | Process | #  | Pitch<br>(um) | Buffer | Coupling | Process |

|----|---------------|--------|----------|---------|----|---------------|--------|----------|---------|

| 1  | 10            | SF     | DC       | std     | 19 | 10            | SF+amp | DC       | std     |

| 2  | 10            | SF     | DC       | mod     | 20 | 10            | SF+amp | DC       | mod     |

| 3  | 10            | SF     | DC       | gap     | 21 | 10            | SF+amp | DC       | gap     |

| 4  | 15            | SF     | DC       | std     | 22 | 20            | SF+amp | DC       | std     |

| 5  | 15            | SF     | DC       | mod     | 23 | 20            | SF+amp | DC       | mod     |

|    |               |        |          |         | 24 | 20            | SF+amp | DC       | gap     |

| 6  | 15            | SF     | DC       | gap     | 25 | 10            | SF+amp | AC       | std     |

| 7  | 20            | SF     | DC       | std     | 26 | 10            | SF+amp | AC       | mod     |

| 8  | 20            | SF     | DC       | mod     | 27 | 10            | SF+amp | AC       | gap     |

| 9  | 20            | SF     | DC       | gap     | 28 | 20            | SF+amp | AC       | std     |

| 10 | 25            | SF     | DC       | std     | 29 | 20            | SF+amp | AC       | mod     |

| 11 | 25            | SF     | DC       | mod     | 30 | 20            | SF+amp | AC       | gap     |

| 12 | 25            | SF     | DC       | gap     | 31 | 10            | OPAMP  | DC       | std     |

| 13 | 10            | SF     | AC       | std     | 32 | 10            | OPAMP  | DC       | mod     |

| 14 | 10            | SF     | AC       | mod     | 33 | 10            | OPAMP  | DC       | gap     |

|    |               |        |          |         | 34 | 10            | OPAMP  | AC       | std     |

| 15 | 10            | SF     | AC       | gap     | 35 | 10            | OPAMP  | AC       | mod     |

| 16 | 20            | SF     | AC       | std     | 36 | 10            | OPAMP  | AC       | gap     |

| 17 | 20            | SF     | AC       | mod     | 37 | 10            | SF mux | DC       | gap     |

| 18 | 20            | SF     | AC       | gap     | 38 | 20            | SF mux | DC       | gap     |

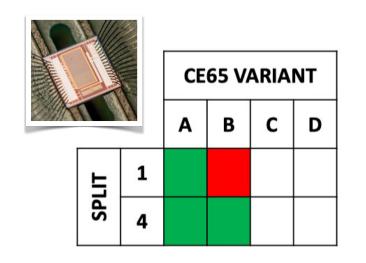

### **CE65**

| # | Pitch<br>(um) | Buffer [coupling]           | Process |

|---|---------------|-----------------------------|---------|

| Α | 15            | Amp [AC], Amp [DC], SF [DC] | std     |

| В | 15            | Amp [AC], Amp [DC], SF [DC] | gap     |

| С | 15            | Amp [AC], Amp [DC], SF [DC] | Mod     |

| D | 25            | Amp [AC], Amp [DC], SF [DC] | std     |

#### **DPTS**

| # | Pitch<br>(um) | Variant                                 |

|---|---------------|-----------------------------------------|

| 1 | 15            | Base                                    |

| 2 | 15            | Column cross connect                    |

| 3 | 15            | column cross connect, shorted DVSS AVSS |

$\times$  4 splits

MLR1 testing @ EICSC - giacomo.contin@ts.infn.it

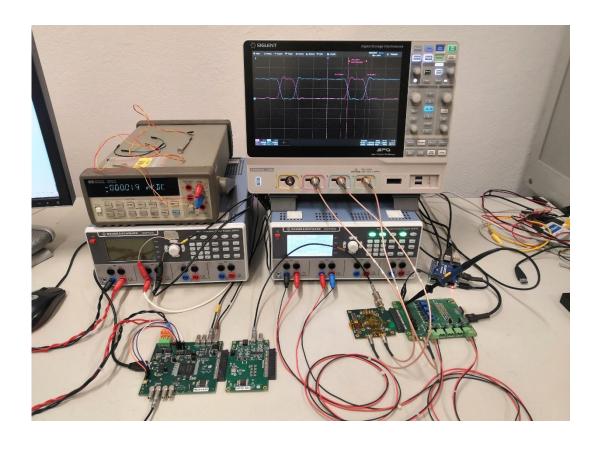

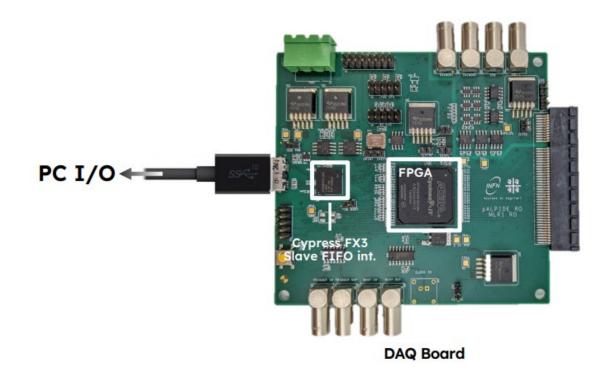

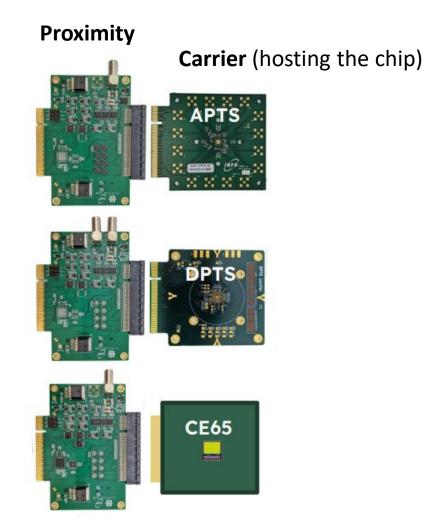

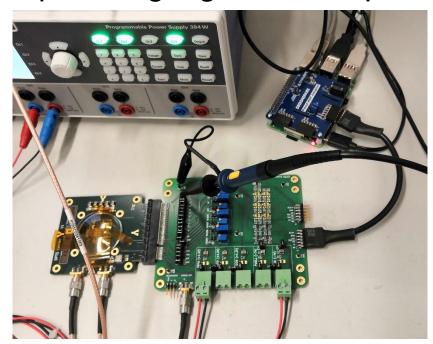

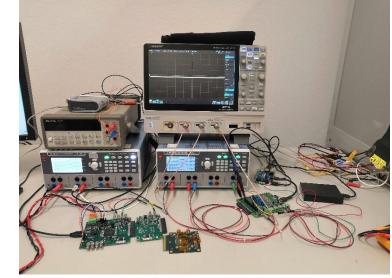

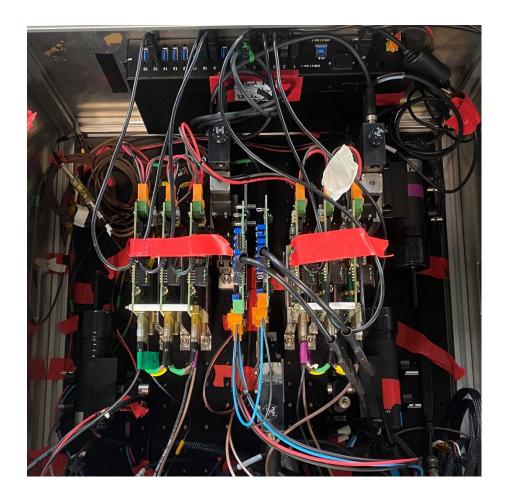

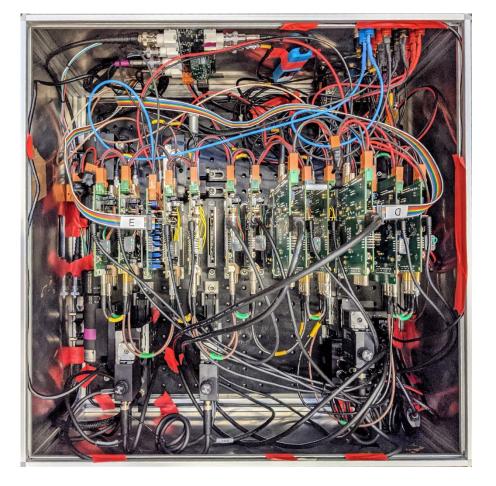

### Common test system: DAQ + Proximity + Carrier

### **MLR1 Test System**

#### MLR1 DAQ board

### 20 DAQ + 20 Proximity cards delivered 17.08.

Commissioning ongoing at INFN Cagliari (FW/SW/all variants), CERN (APTS/DPTS), IPHC (CE65)

#### **DPTS Proximity Card**

#### CE65 Proximity Card

#### APTS SF Proximity Card

#### **APTS OA Proximity Card**

## Test system availability

#### Second Batch Production Status

| Hardware        | APTS-OA                                 | APTS-SF                                           | CE65                                | DPTS                                |

|-----------------|-----------------------------------------|---------------------------------------------------|-------------------------------------|-------------------------------------|

| DAQ Boards      |                                         | 30x, PCBs at FE                                   | DD for mounting                     |                                     |

| Proximity Cards | No 2nd batch                            | 20x PCBs at FEDD for mounting Due 2nd half of Feb | 5x<br>PCBs ready to be sent to FEDD | 5x<br>PCBs ready to be sent to FEDD |

| Carrier Cards   | 60x<br>PCBs due 1st week of Feb (CIRLY) | 250x<br>Due 11 Feb                                | No 2nd batch                        | No 2nd batch                        |

- After 'second batch' production:

- Boards will be just enough for groups currently involved + spares

- In the first phase, only ITS3 groups will access the boards

- Trieste, Liverpool, Daresbury, probably LBL, will be able to obtain some

- If spares stay available / when a new production is completed:

- Distribution to other EIC SC groups

- Decision to be taken at the ITS3 project level

### In the meantime... how to join testing campaign

- Agree on a training period with a group already working on one of the chip

- Join the experienced group for a few weeks to work with them

- Tests are still in the development/debugging phase → very convenient for learning!

- Trainee is preferably an experienced postdoc/researcher

- Trainee can also be a student, provided that there is an experienced supervisor at the home institute

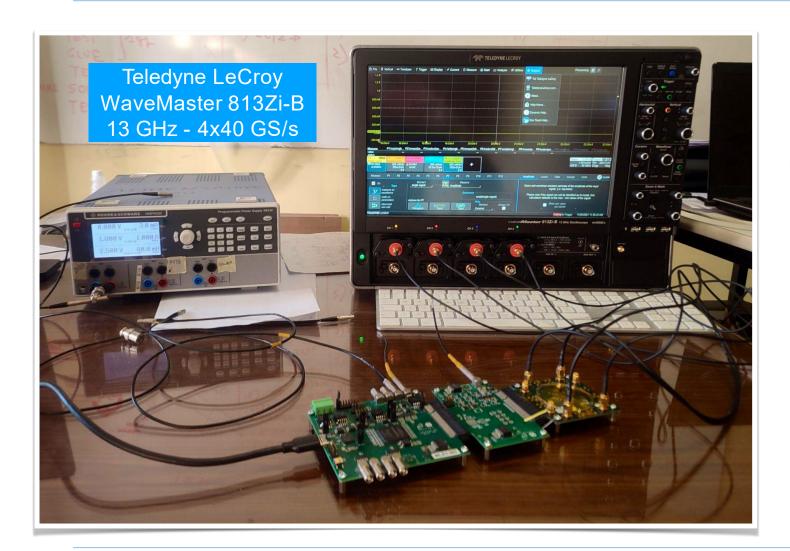

- In the meantime, procure the necessary equipment for testing at the home institute:

- PC / Raspberry Pi

- ITS3 test system (subject to availability see previous slide)

- Electronics laboratory capabilities

- Radioactive sources / laser system

- Oscilloscope with BW>1GHz (only for some tests)

- Wire bonding facility (optional)

- Alternative option: temporar relocate member(s) at host institute

### MLR1 Task List: APTS SourceFollower

| APTS SF characterisation | Lab measurements  |                          | -     | -        | Sensor characterisation in the laboratory.                                               |

|--------------------------|-------------------|--------------------------|-------|----------|------------------------------------------------------------------------------------------|

|                          |                   | Software                 | ?     | ?        | Develop software for signal extraction and clusterisation.                               |

|                          |                   | Noise                    | ?     | ?        | Study the noise of the test system, sensor, RTS.                                         |

|                          |                   | Calibrate                | ?     | ?        | Calibrate conversion and pulsing capacitances (55-Fe).                                   |

|                          |                   | Charge collection        | ?     | ?        | Study the response to 55-Fe X-rays. X different variants X different biases.             |

|                          |                   | Temperature dependence   | ?     | ?        | Characterise sensor response as function of temperature.                                 |

|                          |                   | Separating PWELL and SUB | ?     | ?        | Study the behaviour with separate PWELL and SUB.                                         |

|                          | Testbeam analysis |                          | -     | -        | Analyse the testbeam data.                                                               |

|                          |                   | EUDAQ converter          | Mauro | Nov 2021 | Write, test and verify APTS converter.                                                   |

|                          |                   | Charge collection        | ?     | ?        | Study charge collection MPV and charge sharing. X different variants X different biases. |

|                          |                   | Efficiency               | ?     | ?        | Efficiency vs biasing parameters / threshold for multiple chips.                         |

|                          |                   | Spatial resolution       | ?     | ?        | Spatial resolution vs biasing parameters / threshold for multiple chips.                 |

|                          |                   |                          |       |          |                                                                                          |

# MLR1 Task List: APTS OpAmp

| APTS OA characterisation | Lab measurements  |                   | - | - | Sensor characterisation in the laboratory.                                   |

|--------------------------|-------------------|-------------------|---|---|------------------------------------------------------------------------------|

|                          |                   | Software          | ? | ? | Develop software for signal extraction and clusterisation.                   |

|                          |                   | Noise             | ? | ? | Study the noise of the test system, sensor, RTS.                             |

|                          |                   | Pulsing           | ? | ? | Study response to pulsing.                                                   |

|                          |                   | Calibrate         | ? | ? | Calibrate conversion and pulsing capacitances (55-Fe).                       |

|                          |                   | Charge collection | ? | ? | Study the response to 55-Fe X-rays. X different variants X different biases. |

|                          |                   | Laser response    | ? | ? | Characterise all aspects of the sensor response to laser beam.               |

|                          | Testbeam analysis |                   | - | - | Analyse the testbeam data.                                                   |

|                          |                   | EUDAQ SW          | ? | ? | Write, test and verify Producer and Converter.                               |

|                          |                   | Efficiency        | ? | ? | Efficiency vs biasing parameters / threshold for multiple chips.             |

|                          |                   | Time resolution   | ? | ? | Study time response to MIP beam.                                             |

# MLR1 Task List: DPTS

| DDTO                     |                                        |                            |         |      |                                                                                                                                                    |

|--------------------------|----------------------------------------|----------------------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| DPTS<br>characterisation | Commission DAQ board based test system |                            | Trieste | 2021 | Commission the MLR1 DAQ board + DPTS Proximity for use with DPTS.                                                                                  |

|                          | Lab measurements                       |                            | -       | -    | Sensor characterisation in the laboratory.                                                                                                         |

|                          |                                        | Response vs front-end bias | ?       | ?    | Threshold, noise, Fake Hit Rate, TOT, Rise time as a function of all biasing parameters. Subset of pixels, multiple chips (variants, irradiation). |

|                          |                                        | Noise                      | ?       | ?    | Understand noise sources and behaviour.                                                                                                            |

|                          |                                        | Dead pixels                | ?       | ?    | Study pixels unresponsive to pulsing and external stimuli.                                                                                         |

|                          |                                        | 55-Fe                      | ?       | ?    | Study the response to 55-Fe X-rays and try to use it to calibrate the pulsing capacitance/threshold.                                               |

|                          |                                        | Temperature dependence     | ?       | ?    | Characterise sensor response as function of temperature.                                                                                           |

|                          |                                        | Separating PWELL and SUB   | ?       | ?    | Study the behaviour with separate PWELL and SUB.                                                                                                   |

|                          |                                        | Monitor pixel output       | ?       | ?    | Characterise AOUT pulse as function biasing parameters.                                                                                            |

|                          |                                        | Laser response             | ?       | ?    | Characterise all aspects of the sensor response to laser beam.                                                                                     |

|                          | Testbeam analysis                      |                            | -       | -    | Analyse the testbeam data.                                                                                                                         |

|                          |                                        | Efficiency                 | ?       | ?    | Efficiency vs biasing parameters / threshold for multiple chips.                                                                                   |

|                          |                                        | Spatial resolution         | ?       | ?    | Spatial resolution vs biasing parameters / threshold for multiple chips.                                                                           |

|                          |                                        | Time resolution            | ?       | ?    | Study time response to MIP beam.                                                                                                                   |

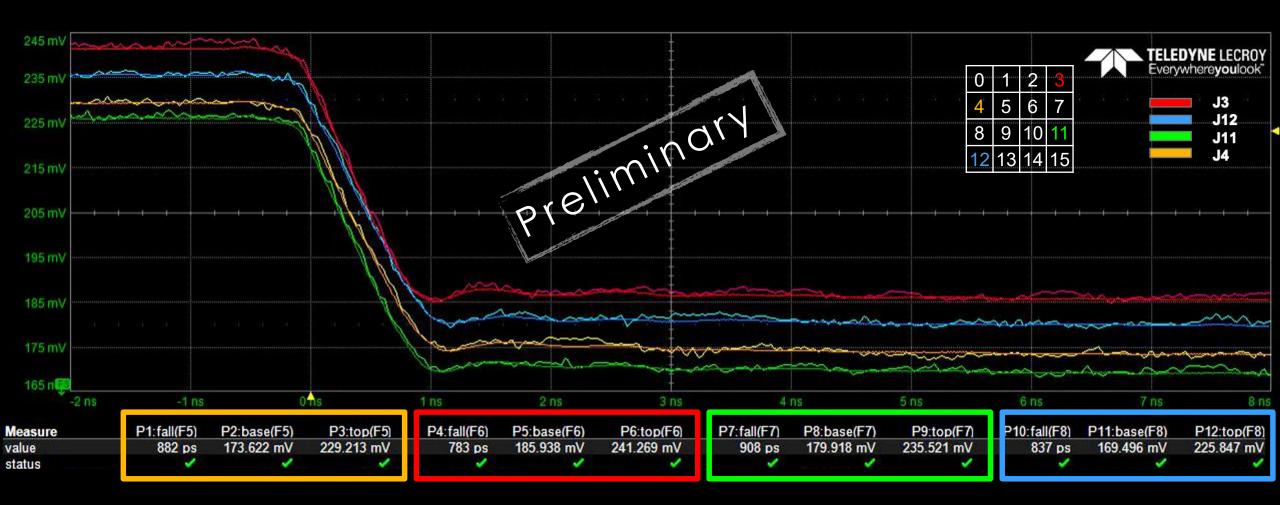

### APTS OA: commissioning started in Torino

#### **10 AO10 sensors in Torino:**

- 4x from split 1

- 6x from split 4

Other flavours to be bonded

# APTS OA: first response

Single and mean signals from pixels 3, 4, 11 & 12 at Vsub = Vpwell = 0V, VH = 1200 mV, others nominal

# CE65: 55Fe lab characterisation

- operational

- no signs of life

- not tested

#### **CE65 Variants:**

- A: pitch = 15 um diode - simple n well

- B: pitch = 15 um diode – deep n with gaps

- C: pitch = 15 um diode – blanket deep n

- D: pitch = 25 um diode – simple n well

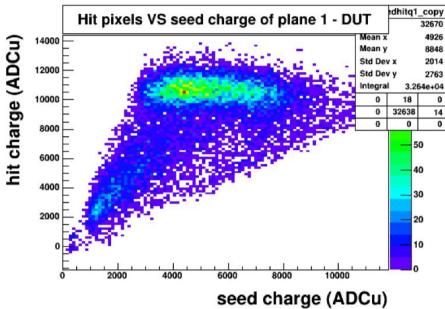

### CE65: Vbb influence, variant A, DC amp, split 4

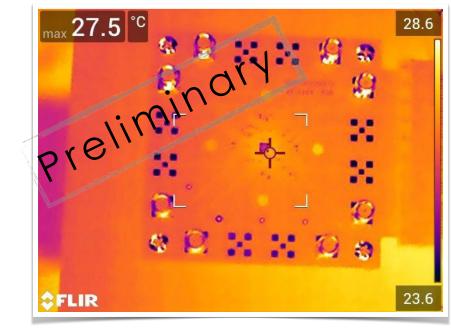

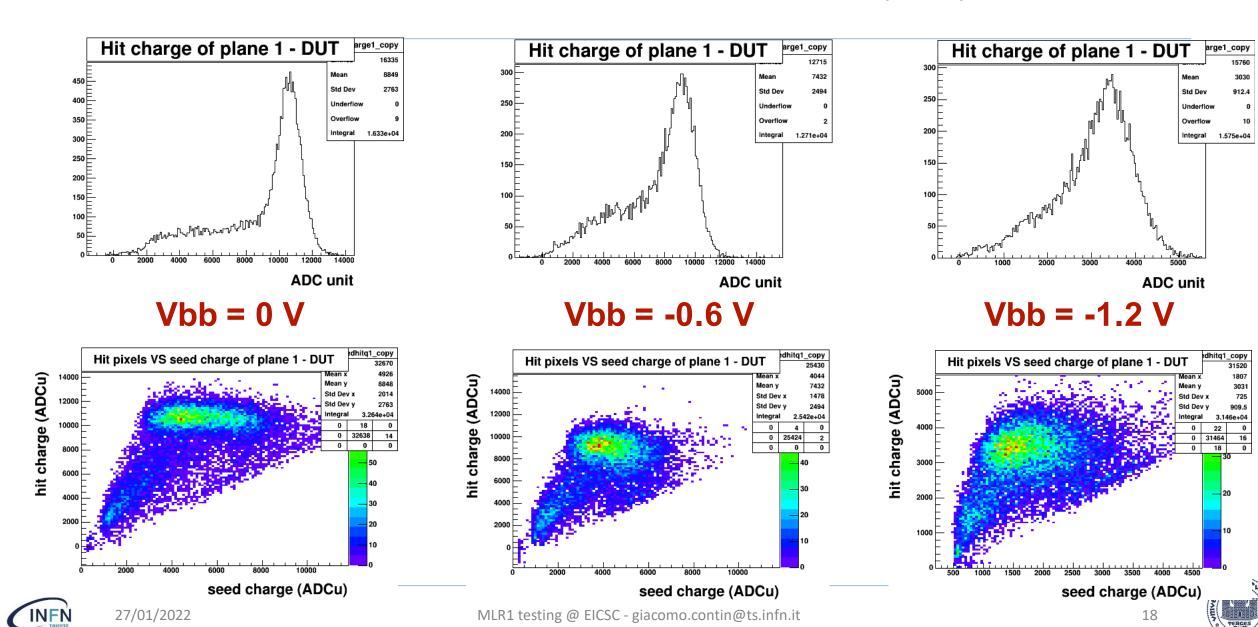

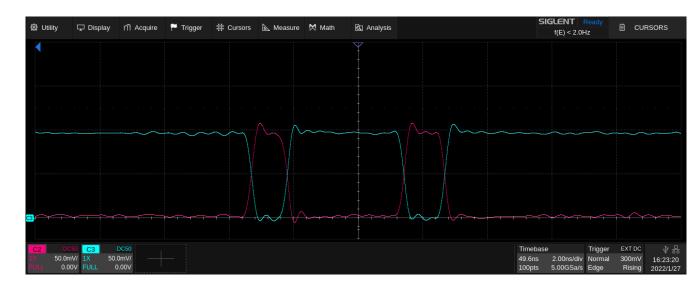

### DPTS: Jitter measurement

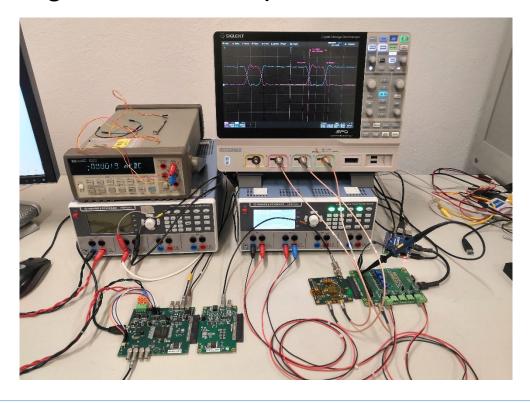

# Practical example of new participation

- Postdoc sent to CERN for 2 weeks to work with ITS3 experts

- Previous experience with ALPIDE testing and electronics

- Full hands-on sessions to catch up with DPTS system and tests

- Guided hardware debugging

- Independent script/procedure development / hardware improvement

- In the meantime at the home institute:

- Existing equipment for ALPIDE testing and general laboratory capabilities

- Purchased large bandwith oscilloscope

- Set up PC/Raspberry PI, power supplies and connections as needed

- In contact with CERN to verify setup replica

- The postdoc is back at the home Institute:

- Working with supervisors, training supervisors and students

- Custom DPTS test system brought back from CERN with 1 working chip

- ~10 DPTS chips + carriers: to be wire bonded locally

- Received an official DPTS test system, to be troubleshooted and integrated w/ software/firmware

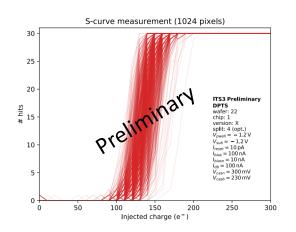

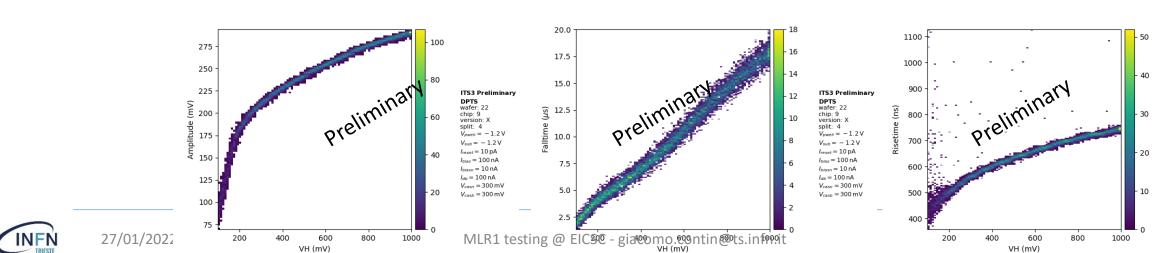

### Current tasks back at the Home institute

- Reproducing DPTS threshold scans with local system

- Replicating custom DPTS test system

- Implementing software classes for Siglent oscilloscope

- Optimizing algorithm/scripts

### Current tasks back at the Home institute

Calibration: Threshold scans

VH (mV)

ITS3 Preliminary DPTS wafer: 22

chip: 9

$I_{blas} = 100 \, \text{nA}$

$I_{db} = 100 \, \text{nA}$

VH (mV)

$V_{casn} = 300 \,\mathrm{mV}$

Developing measurement procedure/code: Analog output Vs pulse height

### Current tasks back at the Home institute

- Commissioning the DPTS on carrier wire-bonding

- Adjust force and positioning

- Wire-bond different flavors/versions for full scan of parameters

- Commissioning official DPTS DAQ-based system

- In collaboration with firmware/software developers

- Comparison with custom DPTS test system behavior

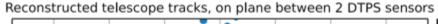

# Beam test campaigns for MLR1 chips

DESY September 2021: DPTS

CERN PS Oct/Nov 2021: APTS, DPTS, CE65

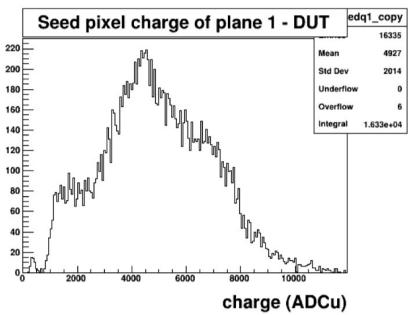

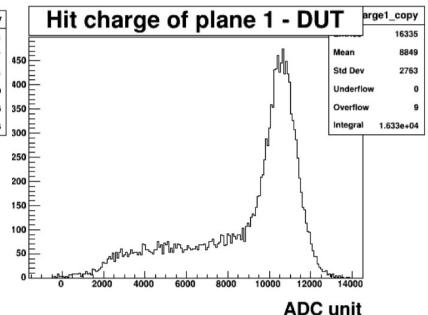

### Preliminary results from beam test data analysis

#### Sneak peak from DESY testbeam

# Participation in beam test data analysis

- Very welcome (at the moment understaffed)

- Does not require test system / lab equipment

- Can be done from remote

- Does require deep training

- EUDAQ telescope framework

- Beam test data format

- Chip data format and interpretation

- Participation in beam test data taking is also welcome, if followed/preceded by data analysis / chip testing in laboratory

# EIC SC Institute participation summary

| Institute                      | Contact<br>person  | Also ALICE<br>ITS3 | Requested<br>a Test<br>system | Has a<br>test<br>system | Active Tasks                             |

|--------------------------------|--------------------|--------------------|-------------------------------|-------------------------|------------------------------------------|

| Birmingham                     | Laura Gonella      | no                 | yes                           |                         |                                          |

| RAL                            | Fergus Wilson      | no                 | yes                           |                         |                                          |

| Liverpool                      | Marielle Chartier  | yes                | yes                           |                         |                                          |

| Lancaster                      | Harald Fox         | no                 | yes                           |                         |                                          |

| Brunel                         | Liliana Teodorescu | no                 |                               |                         |                                          |

| Daresbury                      | Marcello Borri     | yes                | yes                           |                         |                                          |

| University of Chicago Illinois | Zhenyu Ye          | no                 |                               |                         |                                          |

| CAPADS Prague                  | Lukáš Tomášek      | no                 | yes                           |                         |                                          |

| ORNL                           | Jo Schambach       | no                 |                               |                         |                                          |

| LBNL/UC                        | Barbara Jacak      | yes                | yes                           |                         |                                          |

| JLAB                           | Brian Eng          | no                 | yes                           |                         |                                          |

| INFN Trieste                   | Giacomo Contin     | yes                | n.a.                          | yes                     | DPTS, APTS, Bent ALPIDE characterization |

### Conclusions

- First step: discussing with ITS3 leaders the insitute participation

- Effective contribution to testing can start immediately

- Training with experts at host institution (CERN or other groups)

- Laboratory facility and test system set up at the home institute

- Independent work with local supervision

- About 2 months preparation before starting independent work

- Effective contribution to data analysis can start immediately

- Training with experts to be agreed

- Can be done remotely, but a period 'face-to-face' is more effective