ORNL is managed by UT-Battelle, LLC for the US Department of Energy

### eRD104 Overall Plan

Services Reduction intent is to investigate methods to significantly reduce the services load for an EIC MAPS based tracking detector. This can be broken down into the largest components:

#### Powering (Birmingham, RAL)

- Investigate the use of DC-DC converter-based architectures to significantly reduce the number of wires needed to power the detector. This will require that we introduce radiation tolerant DC-DC converters into the detector structure in proximity to the disc/stave connection points.

- Investigate the use of serial powering architectures with the same effect. This will require that we introduce regulation at the (stitched) sensor level either on die or as a hybrid arrangement.

- Assess detector design goals and apply the best overall optimization of available technologies studied under R&D to the final

implementation of the detector (tracking and others who are interested in working on this)

#### Data (ORNL, BNL)

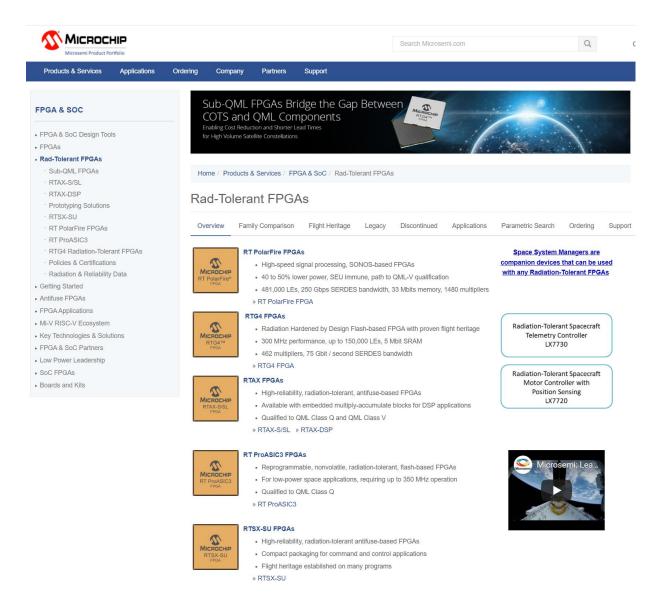

Investigate the use of data aggregation on detector using radiation tolerant FPGAs to receive multiple data streams from sensor blocks (over twinax) and multiplex and transmit the data out via high-speed fiber ribbon connections to RDO boards. This will require functionality in the MUX boards to steer control and configuration and additional power for the MUX boards in detector. Again, the final R&D goal is to develop an optimized viable system for minimizing the services loads due to signal transmission.

### 2022 Work Plan and Schedule

|    | 1 | Task _   | Task Name                                           | Duration , | on _ Start  | Finish      | Predecessors _ | Resource Na |   | Septembe | er  | November |   |   | January |     | March |     | May      | May |                  | July |     | September |   | er            |

|----|---|----------|-----------------------------------------------------|------------|-------------|-------------|----------------|-------------|---|----------|-----|----------|---|---|---------|-----|-------|-----|----------|-----|------------------|------|-----|-----------|---|---------------|

|    | 0 | Mode     |                                                     |            |             | · ·         |                |             | M | В        | E M | В        | E | M | В       | E M | В     | E N | 1 B      | E   | M                | В    | E   | M         | В | E M           |

| 37 |   | =        | Gather serial powering data                         | 40 days    | Fri 1/7/22  | Thu 3/3/22  |                |             |   |          |     |          |   |   |         |     |       |     |          |     |                  |      |     |           |   |               |

| 38 |   | <b>3</b> | design and analyze DC-DC<br>converter architectures | 40 days    | Fri 3/4/22  | Thu 4/28/22 | 36             |             |   |          |     |          |   |   |         |     |       |     |          |     |                  |      |     |           |   |               |

| 39 |   | 3        | design and analyse serial<br>powering architectures | 40 days    | Fri 3/4/22  | Thu 4/28/22 | 36             |             |   |          |     |          |   |   |         |     |       |     | _        |     |                  |      |     |           |   |               |

| 40 |   | 3        | cost/benefit analysis of serial<br>and DC-DC        | 40 days    | Fri 4/29/22 | Thu 6/23/22 | 38             |             |   |          |     |          |   |   |         |     |       |     |          |     | _                |      |     |           |   |               |

| 41 |   | =        | report on serial powering                           | 30 days    | Fri 4/29/22 | Thu 6/9/22  | 39             |             |   |          |     |          |   |   |         |     |       |     |          | *   | ¢ <del>6/9</del> |      | _   |           |   | 1             |

| 42 |   | =        | report on DC-DC powering                            | 30 days    | Fri 6/24/22 | Thu 8/4/22  | 40             |             |   |          |     |          |   |   |         |     |       |     |          |     |                  |      | *∳- | 8/4       |   | 1             |

| 43 |   | 3        | FY22 assessment report on<br>powering options       | 40 days    | Fri 8/5/22  | Thu 9/29/22 | 41,42          |             |   |          |     |          |   |   |         |     |       |     |          |     |                  |      |     |           | * | 9/29          |

| 44 |   | 8        | gather data rate and speed<br>data                  | 40 days    | Fri 1/7/22  | Thu 3/3/22  |                |             |   |          |     |          |   |   |         |     |       |     |          |     |                  |      |     |           |   |               |

| 45 |   | =        | rad tolerant FPGA survey                            | 20 days    | Fri 1/7/22  | Thu 2/3/22  |                |             |   |          |     |          |   |   |         | •   | -l    |     |          |     |                  |      |     |           |   |               |

| 46 |   | 3        | architecture survey                                 | 35 days    | Fri 3/4/22  | Thu 4/21/22 | 44,45          |             |   |          |     |          |   |   |         |     | *     |     | h        |     |                  |      |     |           |   |               |

| 47 |   | 3        | conceptual design(s)                                | 35 days    | Fri 4/22/22 | Thu 6/9/22  | 46             |             |   |          |     |          |   |   |         |     |       |     | <u> </u> |     | ի                |      |     |           |   |               |

| 48 |   | =        | cost benefit analysis                               | 40 days    | Fri 6/10/22 | Thu 8/4/22  | 47             |             |   |          |     |          |   |   |         |     |       |     |          |     | <u> </u>         |      |     |           |   |               |

| 49 |   | =        | report on MUX options                               | 10 days    | Fri 8/5/22  | Thu 8/18/22 | 48             |             |   |          |     |          |   |   |         |     |       |     |          |     |                  |      | Ľ   |           |   | ı I           |

| 50 |   | =        | erd104 FY22 report                                  | 1 day?     | Fri 9/30/22 | Fri 9/30/22 | 49,43          |             |   |          |     |          |   |   |         |     |       |     |          |     |                  |      |     |           | • | <b>♦</b> 9/30 |

# Starting Point: Current ALICE ITS-2 / sPHENIX MVTX

### Radiation Tolerant FPGAs

e.g.:

# High-Speed Interconnects

#### Data connection is taken "off board," simplifying board layout and enhancing signal integrity from IC to faceplate

- Up to 28 Gbps per channel via optical cable for greater reach

- Industry leading miniature footprint allows for higher density close to the data source

- Simple to use system with easy insertion/removal and trace routing, no through-holes, and a surface mount connector system

- Supports data center, HPC and FPGA protocols, including 10/40/100 GbE Ethernet. InfiniBand™, Fibre Channel and Aurora

| 14            | x4  | 25 | x4  |

|---------------|-----|----|-----|

| G b p s       | x12 |    | x12 |

| 16<br>G b p s | x12 | 28 | ×4  |

| ECUO WIDTH                                                                                        | DATA RATE                                                      | CABLE LENGTH                           | 0 HEAT SINK 1                                                                                                                          | FIBER TYPE                                                                                                                               | END 2 OPTIONS*                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -B04 = 4 Tx + 4  -T12 = 12 Tx  -R12 = 12 Rx  -Y12 = 12 Tx + 12  -U12 = 12 Chann AOC (Unidirection | per lane  -16 = 16.1 Gbps per lane (N/A -B04)  -25 = 25.7 Gbps | _"XXX" = Overall Length in Centimeters | -1= Flat -2 = Pin-fin (-14 & -16 only) -3 = Flat with groove -4 = PCle* Pin-fin (-14 & -16 only) -5 = 1.75 cm tall Pin-fin (-804 only) | -4 = Aqua loose tube with Boot -5 = Jacketed ribbon with boot -6 = Jacketed ribbon -7 = Black loose tube with boot -8 = Black loose tube | -Y12 requires -2X end option (Leave blank for -U12)  12 Fibers -01 = MTP <sup>®</sup> Male -02 = MTP <sup>®</sup> Female -07 = MXC <sup>®</sup> Internal Plug -0E = MPO Plus <sup>®</sup> , Male, bayone  24 Fibers -21 = MTP <sup>®</sup> Male -22 = MTP <sup>®</sup> Female -27 = MXC <sup>®</sup> Internal Plug |

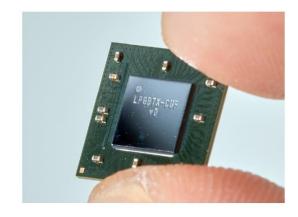

## Rad-Hard Optical Interconnect: "IpGBT"

#### More than a "Communications ASIC"

- Capable of

- 5.12 or 10.24 Gbps (for uplinks)

- 2.56 Gbps (for downlinks)

- Enables the implementation of RadTol links

- DAQ

- Trigger (constant and deterministic latency)

- Experiment control [slow control]

- Implements Control and Monitoring Functions

- Three I2C Masters

- 16 bit General Purpose I/O port

- Output reset pin

- 10 bit ADC (8 multiplexed inputs)

- 8 bit voltage DAC

- 8 bit current DAC

- Temperature sensor

- Designed for radiation hardness

- Total Ionizing Dose (TID): 200 Mrad

- Extensive SEU protection (TMR, FEC)

Pin count: 289 (17 x 17)

Pitch: 0.5 mm

Size: 9 mm x 9 mm x 1.25 mm

M. Firlej, et al., "An lpGBT sub-system for environmental monitoring and control of experiments" (Fri @ 09:50)

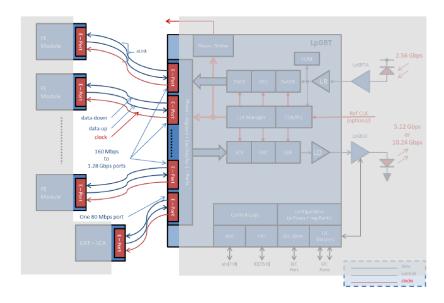

# IpGBT Capabilities

#### Communicates with

- The counting room

- Optical fibre links

- The FE modules / ASICs

- Electrical links (eLinks)

- The Number and Bandwidth of eLinks is programmable

- For Down eLinks

- Bandwidth: 80/160/320 Mbps

- Count: 16/8/4

- For Up eLinks

| Input eLinks (uplink)   |      |      |     |       |     |     |     |       |      |       |     |      |  |  |

|-------------------------|------|------|-----|-------|-----|-----|-----|-------|------|-------|-----|------|--|--|

| uplink bandwidth [Gbps] | 5.12 |      |     |       |     |     |     | 10.24 |      |       |     |      |  |  |

| FEC coding              |      | FEC5 |     | FEC12 |     |     |     | FEC5  |      | FEC12 |     |      |  |  |

| Bandwidth [Mbps]        | 160  | 320  | 640 | 160   | 320 | 640 | 320 | 640   | 1280 | 320   | 640 | 1280 |  |  |

| Maximum number          | 28   | 14   | 7   | 24    | 12  | 6   | 28  | 14    | 7    | 24    | 12  | 6    |  |  |

### Outlook

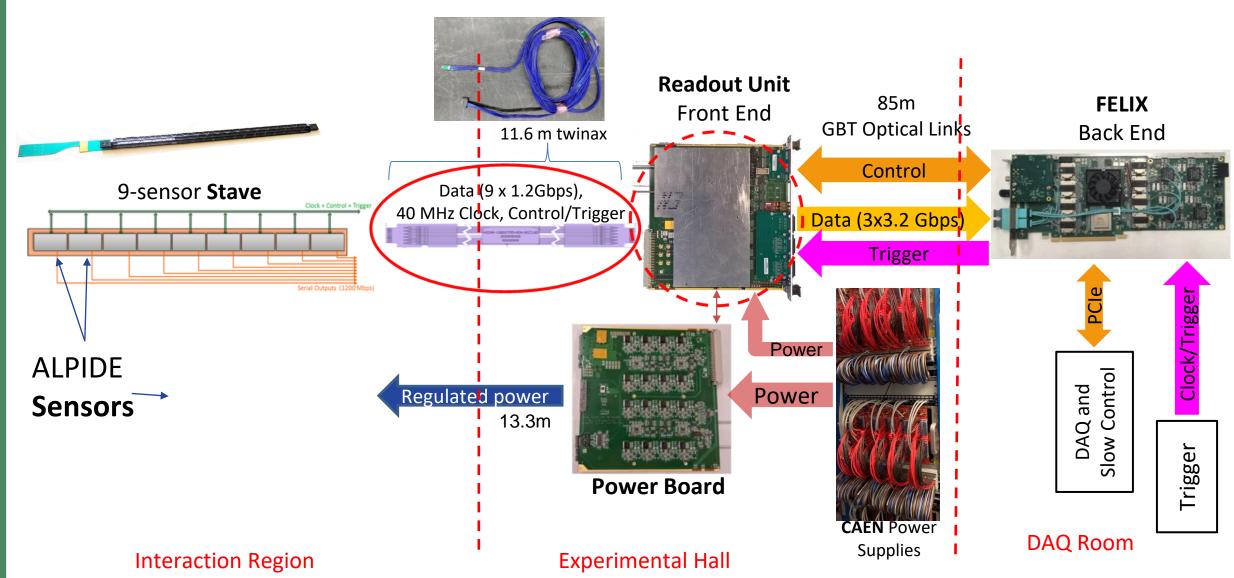

- ORNL has a setup similar to the MVTX setup shown in the earlier slide, including the FELIX board and a stave with 9 ALPIDEs, that could serve as a testbed for a MUX board prototype

- Initial work on this eRD is mostly intellectual and can proceed in the absence of funding

- Funding was mostly requested to pay for consultation with engineers at ORNL and BNL

- Initial work after a conceptual design would be focused on evaluation of the concept with evaluation boards of the various components chosen