# MPGD tracker frontend alternatives

Irakli Mandjavidze

Irfu, CEA Saclay Gif-sur-Yvette, 91191 France

> Internal 07/Jun/2022

- Some alternatives for frontend organization

- Twinax copper cables

- On-detector VFE and off-detector DAQ interface connectivity

- Summary

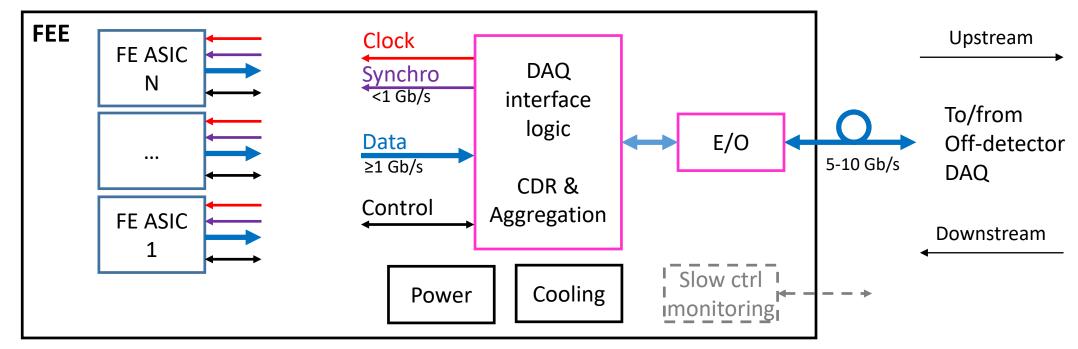

### Frontend electronics

- Detector-family specific frontend chips

- Common FE-DAQ interface

- $\rightarrow$  A bi-directional optical link for clock, synchronization (run control), data, configuration

- Also for slow-control and monitoring, at least partially

- Connectivity between the ASICs and DAQ interface?

- $\rightarrow$  Few organizational alternatives listed

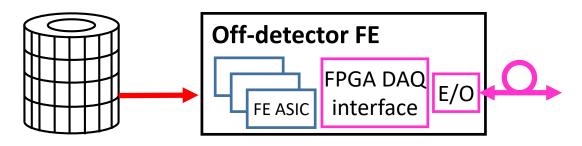

### Frontend organization

**Crowded detector vicinity**

Experimental area with lesser constraints

**Counting room**

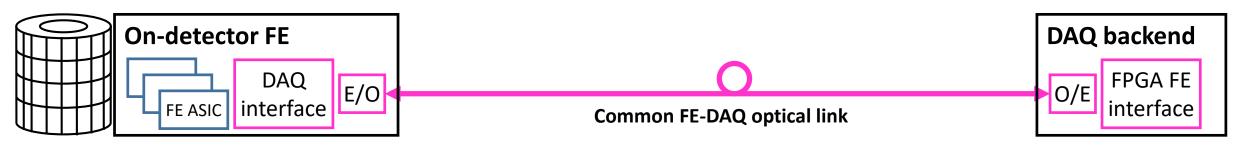

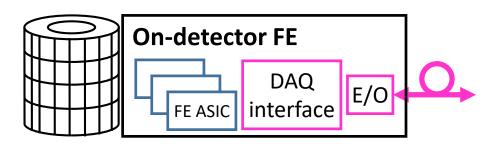

#### • LHC Phase-2 style with low-power DAQ interface (GBT/VTRX $\rightarrow$ lpGBT / VTRX+ and GBT-SCA)

- $\rightarrow$  Pros:

- Optimal for S/N

- High integration potential

- Number of channels per DAQ link

- Single type of frontend to be developed and maintained

- $\rightarrow$  Cons:

- Might be penalizing if implemented with COTS components (FPGA / transceiver)

- Power (see backup), space, cooling, SEU

- $\rightarrow$  To be understood:

- Is the commercial component based model acceptable follow closely eRD104

- For more details see: https://indico.jlab.org/event/519/contributions/9563/attachments/7748/10855/220518\_SroX\_FrontEnd\_IM.pdf

### Frontend organization

Crowded detector vicinity

Experimental area with lesser constraints

**Counting room**

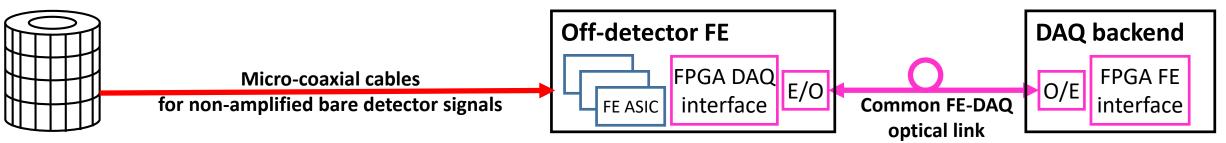

Clas12 MVT-style with passive micro-coaxial detector cables

- $\rightarrow$  Pros:

- Optimal for power/cooling, SEU

- Single type of frontend to be developed and maintained

- $\rightarrow$  Cons:

- Noise due to cable capacitance (50-60 pF/m) + pickup noise

- Clas12: 40 pF/m Hitachi lightweight cables not anymore in production

- High number of cables

- Non negligible cable cost

- $\rightarrow$  To be understood:

- Viability of the solution given the distance between the detector and FE electronics

- For an example see: https://www.sciencedirect.com/science/article/pii/S0168900220300280

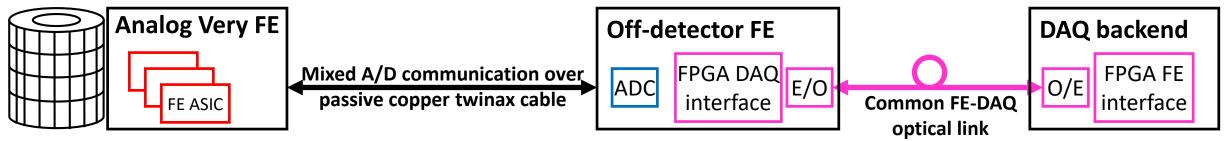

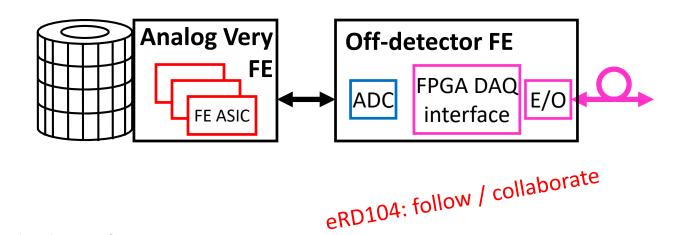

# Frontend organization: analog very frontend

Crowded detector vicinity

Lesser constraints experimental area

**Counting room**

• Minimal on-detector analog very frontend electronics with remote off-detector DAQ interface

- $\rightarrow$  Pros:

- Optimal power/cooling and SEU

- Near optimal for S/N

- Simplest ASIC

- Simplest in downstream communication (*i.e.* I2C, test pulse)

- $\rightarrow$  Cons:

- Two species of frontends to be developed and maintained

- Large number of bulky copper cables

- $\rightarrow$  To be understood:

- Acceptable copper cable length for O(300 MHz) bandwidth analog signals

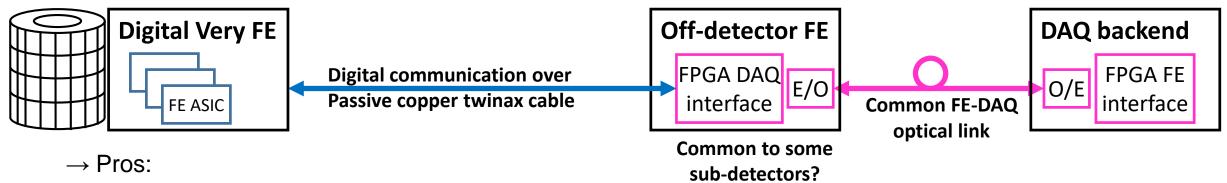

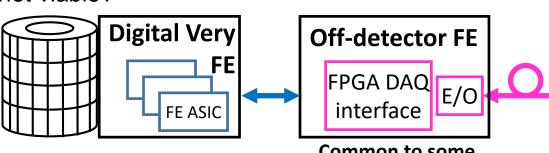

# Frontend organization: digital very frontend

Crowded detector vicinity

Lesser constraints experimental area

**Counting room**

• Minimal on-detector digital very frontend electronics with remote off-detector DAQ interface

- Optimal for S/N and SEU

- Near optimal for power/cooling

- $\rightarrow$  Cons:

- Two species of frontends to be developed and maintained

- Copper cables are more bulky than optical cables

- $\rightarrow$  To be understood:

- Acceptable copper cable length for O(1 Gbit/s) communication speeds

- Number of needed twinax lanes for downstream and upstream communications

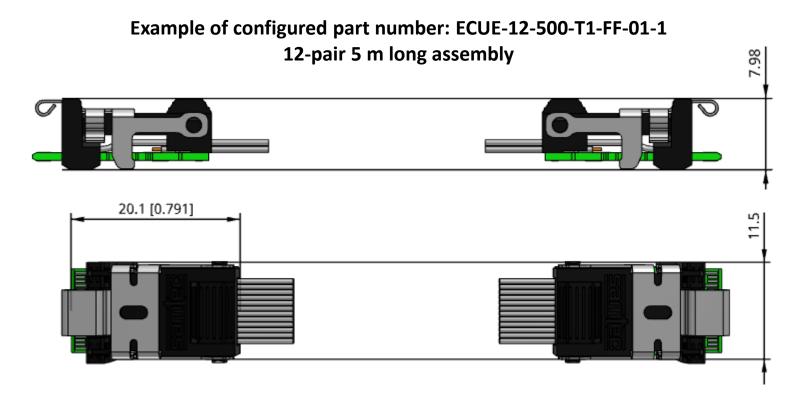

### Twinax copper cable example: Samtec FireFly

- <u>https://www.samtec.com/products/ecue</u>

- https://suddendocs.samtec.com/catalog\_english/ecue.pdf

- Configurable assembly

- $\rightarrow$  8 or 12 pairs

- $\rightarrow$  up to 10 m

- Impressive signal integrity figures

- $\rightarrow$  Qualified for 10-50 Gbit/s speeds

- Max length for O(1 Gbit/s) speed?

- $\rightarrow$  Example in backup

- Rigidity, weight?

- Flammability?

- Cost?

- $\rightarrow$  Contact Samtec technical service

- $\rightarrow$  R&D on data transmission and on clock / synchronous command distribution?

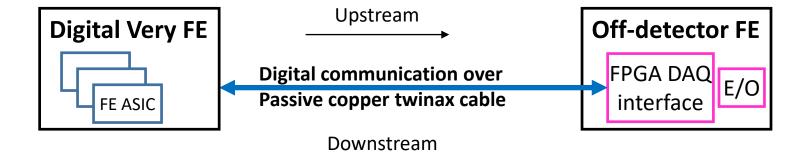

# Very frontend and DAQ interface connectivity

#### Downstream

- $\rightarrow$  Clock

- Unique if on-chip clock generation

- PLL or divider

- Fan-out to all ASICs

- See backup

- Hopefully used for I2C too

- $\rightarrow$  Synchronous commands

- Fan-out to all ASICs

- See backup

- $\rightarrow$  Slow control

- I2C SDA chain

- + I2C SCL if a common clock cannot be used

- $\rightarrow$  Trigger if not a part of synchronous commands

- Multi-drop to all ASICs

- $\rightarrow$  Test pulse

- Multi-drop to all ASICs

- Upstream

- $\rightarrow$  Acquisition data

- Point-to-point

- N ASICs x M output links per ASIC

- $\rightarrow$  Slow control

- If I2C SDA line cannot be bi-directional

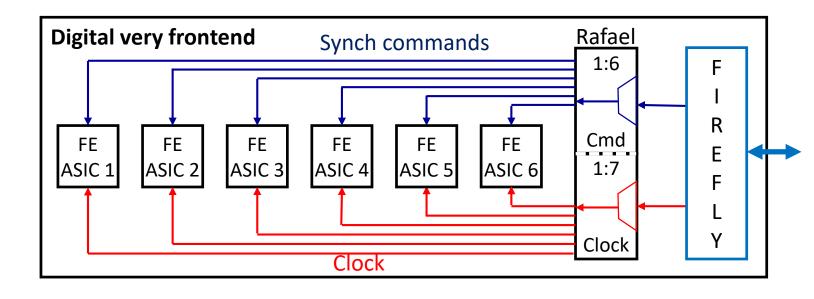

- Optimistic 512-channel FE example

- $\rightarrow$  8 64-channel FE ASIC with

- 1 Gbit/s output link

- Unique system clock used for I2C as well

- Synchronous command encoding trigger

- $\rightarrow$  Common on-onboard test pulse logic

- $\rightarrow$  Bi-directional I2C SDA

- $\rightarrow$  Single 12-pair FireFly interface

- 3 downstream lines:

- Clock, command, Test

- 8 upstream lines

- 8 data links

- 1 bi-directional I2C SDA line

# Summary

### • Fully integrated on-detector frontend can be penalizing

- $\rightarrow$  Power / cooling

- $\rightarrow$  Material budget

- $\rightarrow$  Space

- $\rightarrow \text{SEU}$

- Fully integrated off-detector frontend

- $\rightarrow$  Will most probably penalize S/N

- Bare non-amplified detector signals

- High input capacitance due to long (>3m?) cables

- Noise pickup

- $\rightarrow$  May result in low integration level

- Large number of detector cables to route-out

- Split analog frontend may penalize

- $\rightarrow$  S/N

- Analog transmission over long cables

- $\rightarrow$  Integration

- Large number of detector cables to route-out

# Summary

#### Split digital frontend

- $\rightarrow$  Optimal alternative if fully integrated on-detector FE is not viable?

- S/N

- Power / cooling; SEU; material budget

- $\rightarrow$  Intermediate level of connectivity integration

- Cable count

- Lower than split-analog or integrated off-detector frontend

- Higher than integrated on-detector frontend

- FE ASICs with a smaller digital interface are preferable

- Single clock for acquisition, communication and I2C

- Single high speed upstream link

- Trigger being one of the synchronous commands

- $\rightarrow$  May require companion commercial or ad-hoc ASICs for digital very frontend

- Clock / sync command distribution ASIC

- See backup

- Bi-directional I2C buffer

- $\rightarrow$  The off-detector frontend might be a common development among some of sub-detectors

→ A quick R&D to evaluate copper twinax cable performance for considered communication speeds?

■ Achievable length for acceptable signal integrity; rigidity; weight; encumbrance; flammability

Split FE alternative 7/Jun/2022

Common to some sub-detectors?

eR010A. Follow I collaborate

### Backup

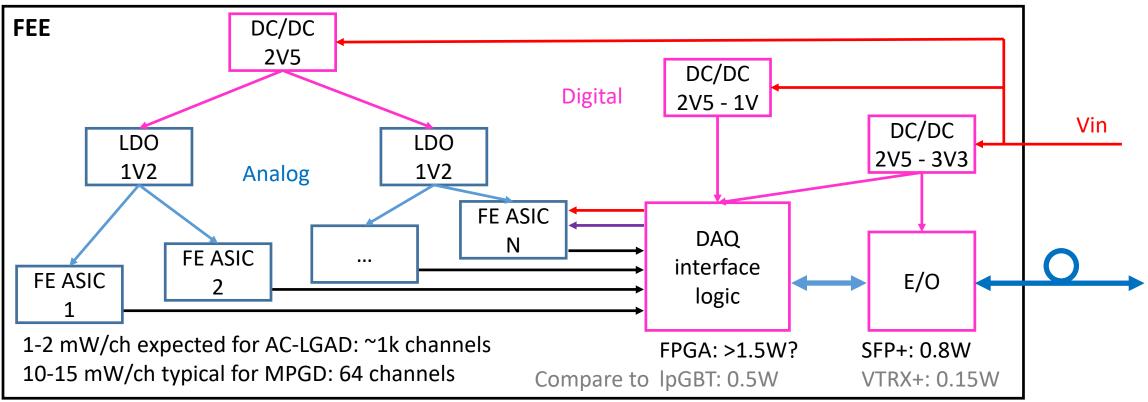

## Power: is an FPGA-based integrated on-detector FE viable

- 1.5 T magnetic field requires efficient power regulation

- $\rightarrow$  High efficiency DC/DC converter for digital power

- $\rightarrow$  LDO regulators for analog circuitry

- $\rightarrow$  Frontend board with MPGD ASICs: 4-8 W + DAQ logic and E/O power

- 4 8 ASICs per frontend; ~1 W per ASIC

- $\rightarrow$  Frontend board with AC-LGAD ASICs: ~3 W + DAQ logic and E/O power

- 2 ASICs per frontend; ~1.5 W per ASIC

# Clock and fast command distribution example

- Rafael Radiation-hArd Fan-out Asic for Experiments at LHC developed at Irfu, CEA Saclay

- $\rightarrow$  3 inputs and 13 outputs

- $\rightarrow$  CLPS signaling

- CM voltage: 0.6 V

- Differential swing: 200-400 mV

- Programmable drive and emphasis

- $\rightarrow$  Single buffer: any input to 13 outputs

- $\rightarrow$  Double buffer

- Input 1 to 6 outputs

- Input 2 to 7 outputs

- $\rightarrow$  Up to 400 MHz and beyond

- $\rightarrow$  Low additive jitter of < 2 ps

- $\rightarrow$  LHC-level TID, neutron, SEU

- $\rightarrow$  130 nm technology

- $\rightarrow$  Possibility to embed a PLL

- If no jitter cleaner PLL in ASICs

- Commercial counterparts

- → IDT 8P34S2108: https://www.renesas.com/eu/en/document/dst/8p34s2108-datasheet

- $\rightarrow$  TI CDCLVD1216: http://www.ti.com/lit/ds/symlink/cdclvd1216.pdf

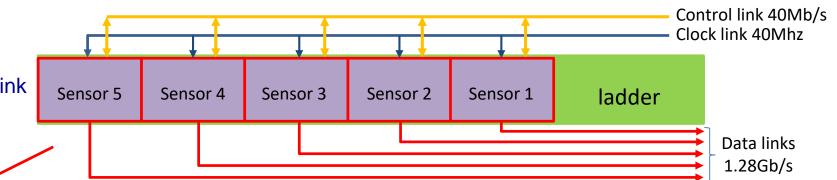

# Twinax copper cable performance example: Alice MFT

Muon Forward Tracker: ladders with a variable number of ALPIDE silicon sensors

- Pixel = 29 x 27 µm<sup>2</sup>

- ZS, triggered or continuous

- 1.28 Gbit/s upstream data link

- Pre-emphasis capability

- 40 MHz clock

- 40 Mb/s control

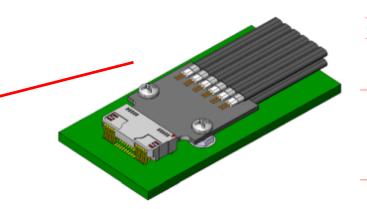

Samtec 12-ribbon FireFly twinax cables with low profile connectors

- $\rightarrow$  Signal integrity studies

- Up to 8m of cable and 9 connectors in the path

- Reliable communication with BER better than 10<sup>-14</sup>

- Adjust pre-emphasis

Split FE alternative 7/Jun/2022