# eRD24: Silicon Sensors with High Position and Timing Resolution for Roman Pots at the EIC

#### **Project members**

E.C. Aschenauer (BNL), A.Tricoli (BNL), A. Jentsch (BNL), S. Fazio (U. Calabria, Rende, Italy), A. Kiselev (BNL), G. Giacomini (BNL), Cinzia da Via (Manchester/SBU), M. Benoit (BNL), A. Seiden (UCSC), H. Sadrozinski (UCSC), B. Schumm (UCSC), R. Dupré (IJCLAb, Orsay, FR), D. Marchand (IJCLAb, Orsay, FR), C. Munoz Camacho (IJCLAb, Orsay, FR), L. Serin (IJCLAb, Orsay, FR), C. de La Taille (Omega, Palaiseau, FR), M. Morenas (Omega, Palaiseau, FR)

#### Expertise

- EIC physics, simulations, and detectors.

- Sensor technology and development (LGADs) from LHC.

- Readout electronics (ASIC) from LHC.

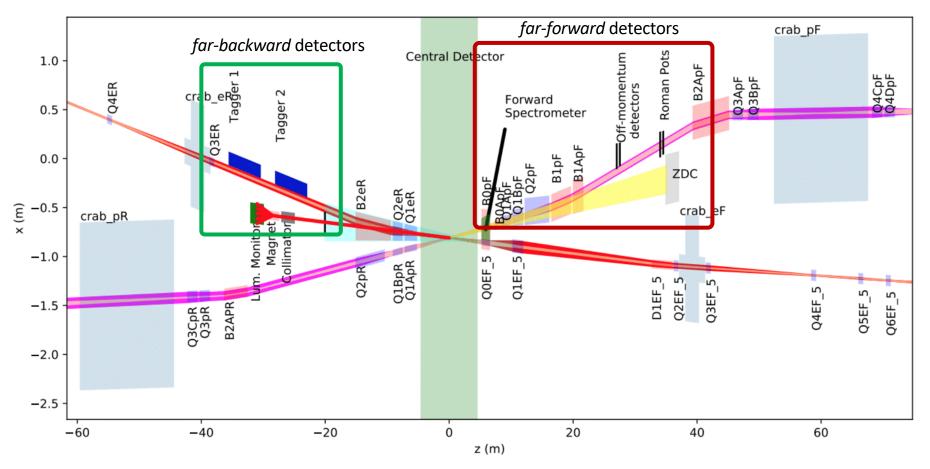

#### **EIC Interaction Region Layout**

- Central detector spans -4.5 to 5 meters and is machine-component free (except for beam pipe).

- Hadron-going and electron-going directions after central detector fully instrumented.

- Hadron and electron beam cross with an angle of 25 mrad.

## FF Hadron-Going Direction & Acceptance

| ı                       | Detector                             | Acceptance                                                               | Notes                                                            |  |  |  |  |

|-------------------------|--------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| 1                       | Zero-Degree Calorimeter (ZDC)        | $\theta$ < 5.5 mrad ( $\eta$ > 6)                                        | About 4.0 mrad at $\phi \sim \pi$                                |  |  |  |  |

|                         | Roman Pots (2 stations)              |                                                                          | $0.65 < \frac{p_{z,nucleon}}{p_{z,beam}} < 1.0$ *10 $\sigma$ cut |  |  |  |  |

|                         | Off-Momentum Detectors (OMD)         | $0.0 < \theta < 5.0 \text{ mrad } (\eta > 6)$                            | Roughly $0.3 < \frac{p_{z,nucleon}}{p_{z,beam}} < 0.6$           |  |  |  |  |

| B2pf dipole             | B0 Sensors (4 layers, evenly spaced) | $5.5 < \theta < 20.0 \text{ mrad}$<br>$(4.6 < \eta < 5.9)$               | In flux: depends on pipe and electron quad.                      |  |  |  |  |

| ZI                      | DC                                   | "nucleon mo                                                              | "nucleon momentum fraction" = $\frac{p_{z,nucleon}}{p_{z,beam}}$ |  |  |  |  |

|                         |                                      |                                                                          | Fraction of momentum for nucleon compared to beam.               |  |  |  |  |

| Roman p<br>(inside pi   |                                      | B1apf dipole                                                             |                                                                  |  |  |  |  |

|                         |                                      | B1pf dipole                                                              |                                                                  |  |  |  |  |

| EicRoot – GEANT4<br>VMC | Off-Momentum Detectors               | Q1bpf quadrupole                                                         |                                                                  |  |  |  |  |

|                         |                                      | Hadron beam Q2pf quadrupole Q1apf quadrupole coming from IP B0apf dipole |                                                                  |  |  |  |  |

|                         |                                      |                                                                          | licon Detector e magnet bore)  B0pf dipole                       |  |  |  |  |

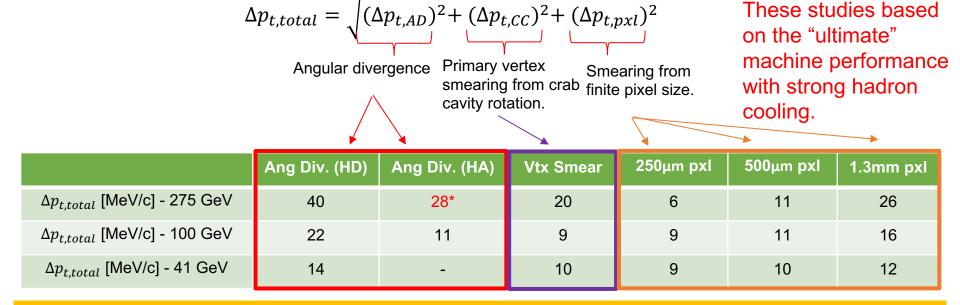

#### Reminder: Requirements

• The various contributions add in quadrature (this was checked empirically, measuring each effect independently).

- Beam angular divergence

- Beam property, can't correct for it sets the lower bound of smearing.

- · Vertex smearing from crab rotation

- Correctable with precise timing (~35ps).

- ~70ps timing: effective bunch length is  $2cm \rightarrow 0.25mm$  vertex smearing (~7 MeV/c).

- Finite pixel size on sensor

- 500µm seems like the best compromise between potential cost and smearing

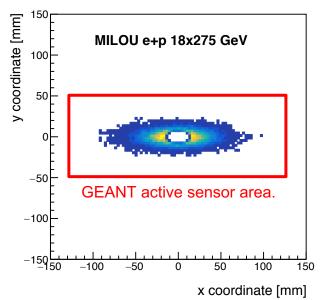

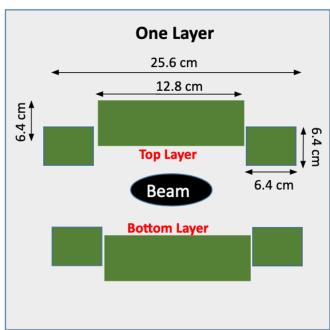

## Reinforcement of needed active area

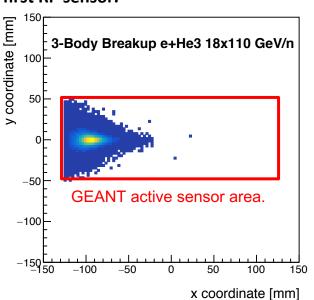

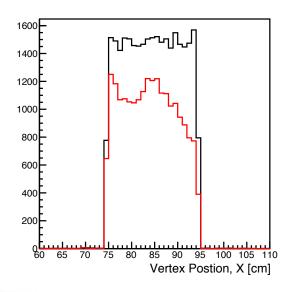

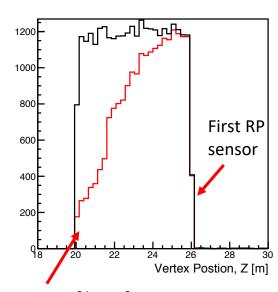

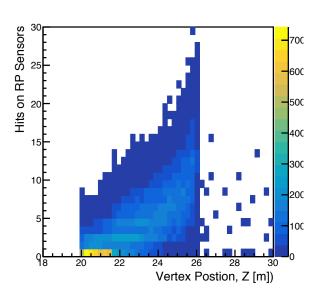

- DVCS studies as a function of beam energy showed that a needed active area of ~ 25cm x 10cm was needed to provide full coverage at medium and low energy.

- Recent studies with e+He3 collisions show that this large active area is needed to tag the two spectator protons, reinforcing the requirement.

#### Protons incident on first RP sensor.

## Recap of Physics and Specs

#### Physics Goals of Roman Pots

- Tag protons and light nuclei close to the beam from coherent processes, protons from nuclear breakup, etc.

- Crucial for exclusive and diffractive physics.

#### Essential requirements gleaned from simulations

- Large active area (~25cm x 10cm)

- Time resolution 30-50ps

- 500μm x 500μm pixels

- Edgeless (inactive edges ~< 150μm)</li>

- AC-LGAD technology of choice to meet these requirements.

## Open questions from last report and new study

- What kinds of rates can we expect on the AC-LGAD sensors in the Roman Pots?

- How does this translate to occupancies?

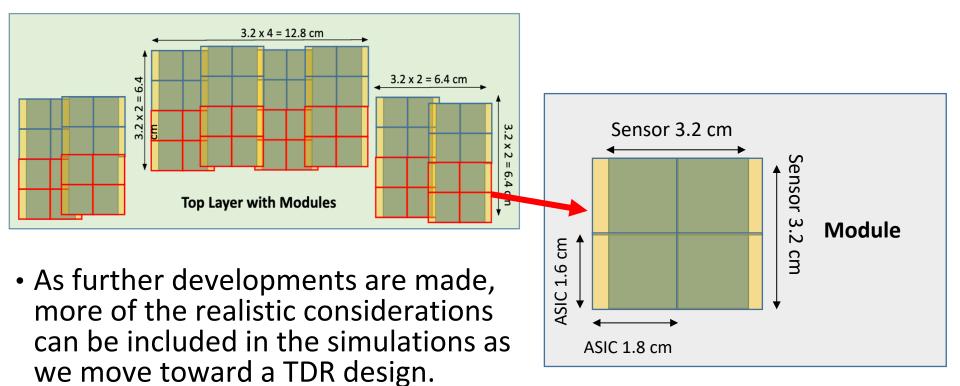

- What is the ideal design for a single sensor + ASIC?

- How does this affect the layout for the full detector subsystem?

- Estimate the chip area needed for an EIC optimized version of the ALTIROC as this may drive the minimum pixel size.

- Estimate ASIC power dissipation.

- Understand accelerator clock's inherent jitter and transmission from the accelerator control room to experiment (in progress).

## Backgrounds from beam+gas

- Collisions of beam hadrons with gas molecules in the beam pipe are a source of background for the Roman Pots.

- Vacuum will be  $\sim 10^{-9}$  mbar in the drift region near the Roman Pots.

- With the beam parameters in the CDR, collision rate will be  $^{\sim}$  500kHz, while the beam gas rate (assuming H<sub>2</sub> is dominant gas) is  $^{\sim}$  5kHz.

End position of b1apf

Only appreciable beam+gas events come from the drift area after the last dipole before the Roman Pots.

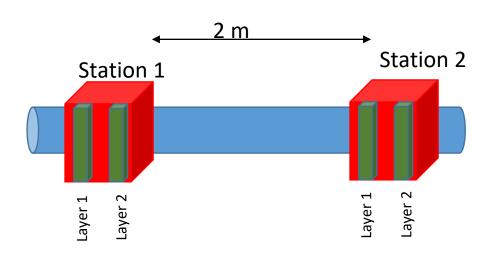

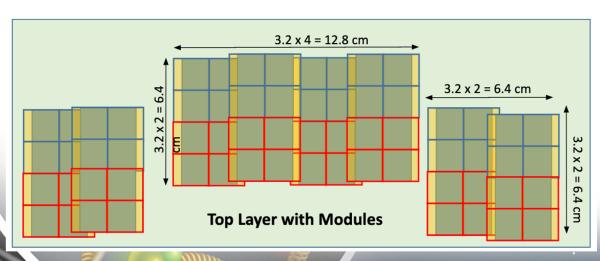

### New Strawman Layout

• Updated strawman layout with current design for LGAD sensor + ASIC.

## New Strawman Layout

Updated strawman layout with current design for LGAD sensor + ASIC.

| ASIC size               | ASIC Pixel pitch | # Ch.<br>per ASIC | # ASICs<br>per module | Sensor area             | # Mod.<br>per layer | Total #<br>ASICs | Total #<br>Ch. | Total<br>Si Area      |

|-------------------------|------------------|-------------------|-----------------------|-------------------------|---------------------|------------------|----------------|-----------------------|

| 1.6x1.8 cm <sup>2</sup> | 500 μm           | 32x32             | 4                     | 3.2x3.2 cm <sup>2</sup> | 32                  | 512              | 524,288        | 1,311 cm <sup>2</sup> |

#### New sensor production at BNL

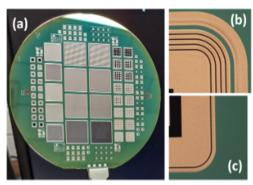

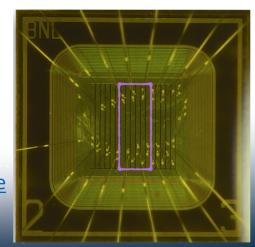

Figure 5: (a) picture of a 4" silicon wafer with the new layout. (b) corner of a device, showing the new termination, (c) slim termination featured in a subset of devices.

- Study of ultimate spatial resolution:

- Strips with variable pitches and geometry (e.g. zig-zag, hexagonal, crosses)

- Produced to test dependence of signal sharing (space resolution) on geometry tested at test-beams.

- Different geometrical patterns optimized for spatial resolution could allow for larger overall pixel size, and therefore less total pixels per sensor -> leads to reduced number of channels and power consumption, and less cooling!

- New wafer production made at BNL

- Same substrate as previous productions

(4" diameter, 50 µm thick p-type epitaxial layer)

- Process modified to correct flaws from preceding productions and those arisen from intensive tests

- Many devices, with areas up to 1.4 cm x 1.4 cm, with a modified termination structure, including slim edges test structures.

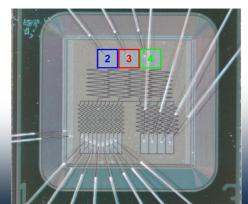

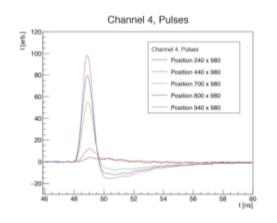

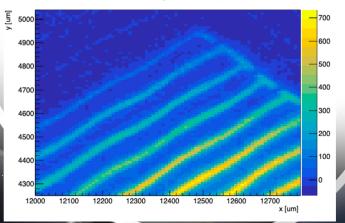

## **Sensor Testing**

• Extensive testing in laboratories at BNL, UCSC (beta-particles, lasers scans), test-beams (FNAL)

- IR laser scans from the back of the sensor.

- Pulses close to a **pad with size 200 μm, pitch = 500 μm**

- ⇒ Signal height is a function of distance from readout pad

- underneath the pixel metal is constant,

10% on next neighbor.

- Signal from 4 pixels can be used to improve space resolution.

- Size of pixel metal to be minimized to reduce capacitive pick-up between pixels and maximize information from signal sharing

- <u>Test-beam at FNAL with 120 GeV protons shows that AC-LGADs meet</u> requirements

- 30-35 ps time resolution

- < 15 μm space resolution with strip sensor: 100 μm pitch, 20 μm gap</p>

- ~100% particle detection efficiency

- See:

https://indico.fnal.gov/event/46746/contributions/210254/attachments/141193/177718/Apresyan 4D-trackers.pdf

## ASIC development

- Strategy to modify ASIC (ALTIROC, TSMC 130 nm) used in ATLAS timing detector (HGTD) and make it compatible to Roman Pot specs

- Extensive discussions between electronics experts at IJCLab/OMEGA, and sensors and EIC machine experts

- Main modifications have been identified to reduce pixel pitch from 1.3 mm to 500 μm

- Low occupancy and triggerless EIC readout simplifies ASIC design, e.g. no need for SRAM

- > Starting point is same front-end concept (preamplifier, discriminator and two TDC for Time of Arrival and Time Over Threshold)

- > Replacing TDC with ADC and sampling pulses is under consideration to improve information of signal sharing

ASIC power dissipation of a 32x32 channel ASIC

Per pixel power dissipation of 3 mW (assuming 10% occupancy - very conservative!, as expected occupancy <<01%)

3.072 W per chip, including the peripheral electronics

1.067 W/cm² power density

total power dissipation in the whole detector of 1.573kW (Strawman layout)

For comparison ALTIROC for HGTD: 1.2 W/chip (300 mW/cm2) and 19.3kW total power dissipation

Optimization: thanks to lower AC-LGAD capacitance, transistor size in the

preamp can be reduced.

- The design of a 4x4 channels prototype will start at OMEGA in spring 2021 with an expected submission end 2021 (funds secured for prototype run).

- On-going discussion with EIC accelerator experts:

250 fs is estimate EIC clock jitter RMS.

Long term drift of the clock will need to be assessed, but can be compensated.

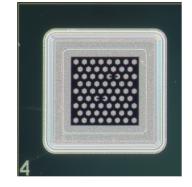

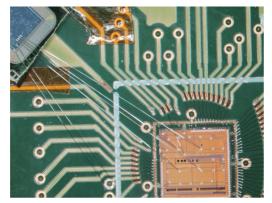

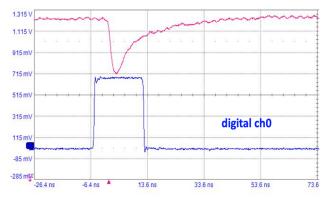

## First Tests of AC-LGAD Compatibility with ALTIROC

- Assembly: ALTIROC0 v1 prototype (4 channels) + strip AC-LGAD with pitch 100 μm, and inter-strip gap of 20 μm.

- ALTIROCO chip: analog readout after the preamplifier, 2 TDCs (Time-Of-Arrival and Time-Over-Threshold) and threshold discriminator. Time jitter smaller than 20 ps for input charge larger than 5 fC

- ALTIROC1 + AC-LGAD already assembled for studying the Constant Fraction Discriminator. To be studied next period.

- Signal from beta-particles from 90Sr source.

- Clear signal with negative and positive polarity.

- Fast (~5 ns) signal compatible with published results for (DC-)LGAD sensors read-out via ALTIROCO [JINST 15 P07007 (2020)]

Normalized charge collection [A.U.]

- Laser Scan Colors: integral charge of the signal peak from the ALTIROC analog output generated by IR laser on sensor.

- Results compatible with those with beta-particles ('waves' due to board vibrations - to be fixed).

These results show that the off-the-shelf ALTIROC can read the signals from the AC-LGAD!

Modifications needed to optimize (in progress).

#### Costs

| Item                                                                     | Cost [k\$] |  |  |

|--------------------------------------------------------------------------|------------|--|--|

| Sensors                                                                  | 260        |  |  |

| ASICs                                                                    | 280        |  |  |

| Peripheral Electronic Boards (IpGBT, VTRX, DC-DC conv., PCB, connectors) | 25         |  |  |

| LV and HV systems                                                        | 45         |  |  |

| Cables (LV,HV,DCS), Electrical connectors                                | 70         |  |  |

| Fibers, Optical connectors                                               | 20         |  |  |

| Module Assembly (incl. hybridisation, flexes, assembly)                  | 90         |  |  |

| Cooling system                                                           | 70         |  |  |

| Mechanics (on-det cooling plate, suport plate cooling, hermetic vessel)  | 30         |  |  |

| тот                                                                      | 890        |  |  |

| TOT*1.33                                                                 | 1,200      |  |  |

The direct cost for the Roman Pots detector (excluding labor as well as R&D and preproduction cost) is estimated to be \$1.2M, based on experience building the ATLAS timing detector.

The total cost includes a 1.33 factor that accounts for an underestimation of the Strawman detector layout cost, based on the experience of cost underestimation for the ATLAS timing detector in the LOI with respect to the TDR.

#### International LGAD Consortium

- We have also established a Consortium of 14 international institutes and 33 scientists with interests in the LGAD technology for EIC detectors.

- See Expression of Interest on "Fast timing silicon detectors for EIC detectors", (<a href="https://indico.bnl.gov/event/8552/contributions/43183/attachments/31235/49294/EIC.EoI\_LGAD\_consortium.pdf">https://indico.bnl.gov/event/8552/contributions/43183/attachments/31235/49294/EIC.EoI\_LGAD\_consortium.pdf</a>)

- Two meetings have already taken place and future discussions on dedicated topics are planned in the coming weeks and months, see indico folder of the agendas https://indico.bnl.gov/category/323/

#### Expression of Interest (EOI): Fast timing silicon detectors for EIC detectors

Artur Apresyan<sup>d</sup>, Whitney Armstrong<sup>a</sup>, Elke-Caroline Aschenauer<sup>b</sup>, Mathieu Benoit<sup>b</sup>, Carlos Munoz Camacho<sup>f</sup>, Janusz J. Chwastowski<sup>e</sup>, Olga Evdokimov<sup>m</sup>, Salvatore Fazio<sup>b</sup>, Frank Geurts<sup>j</sup>, Gabriele Giacomini<sup>b</sup>, Sylvester Joosten<sup>a</sup>, Alexander Kiselev<sup>b</sup>, Wei Li (contact)<sup>j</sup>, Xuan Li<sup>g</sup>, Constantin Loizides<sup>i</sup>, Jessica Metcalfe<sup>a</sup>, Zein-Eddine Meziani<sup>a</sup>, Rachid Nouicer<sup>b</sup>, Christophe Royon<sup>n</sup>, Hartmut Sadrozinski<sup>l</sup>, Bruce Schumm<sup>l</sup>, Abe Seiden<sup>l</sup>, Laurent Serin<sup>f</sup>, Rafał Staszewski<sup>e</sup>, Stefania Stucci<sup>b</sup>, Jacek Świerblewski<sup>e</sup>, Christophe de la Taille<sup>c</sup>, Daniel Tapia Takaki<sup>n</sup>, Alessandro Tricoli (contact)<sup>b</sup>, Maciej Trzebiński<sup>e</sup>, Cinzia Da Via<sup>k</sup>, Bolesław Wysłouch<sup>h</sup>, and Zhenyu Ye<sup>m</sup>

- · Argonne National Lab (ANL)

- Brookhaven National Lab (BNL)

- Organisation de Micro-Électronique Générale Avancée (OMEGA), Ecole Polytechnique

- · Fermi National Lab (FNAL)

- Institute of Nuclear Physics Polish Academy of Sciences (IFJ PAN)

- Laboratoire de Physique des 2 Infinis Irène Joliot Curie (IJCLAB)

- · Los Alamos National Lab (LANL)

- · Massachusetts Institute of Technology (MIT)

- · Oak Ridge National Lab (ORNL)

- · Rice University (Rice)

- Stonybrook University (Stonybrook)

- · University of California, Santa Cruz (UCSC)

- University of Illinois, Chicago (UIC)

- · University of Kansas (KU)

### Specific plans for next period

#### Simulation Goals

- Implement new layout of sensors into GEANT simulations and assess impact.

- Extend study to include the Off-Momentum Detectors. Acceptances are already understood from YR, but further study needed (e.g. layout, backgrounds, etc.).

#### Sensor development

- Analyze test beam data and continue lab tests to optimize fabrication parameters, comparison with TCAD simulations

- Fabrication of sensors with varied doping of the resistive n-type layer to assess its impact on signal sharing

- Implementation of large area prototype with design and layout towards the Roman Pots specifications (e.g. 500 μm pitch pixels, slim edges)

#### ASIC development

- Continue testing of ALTIROC + AC-LGAD to assess collection properties in greater detail, signal sharing between channels, dependence of time-over-threshold (TOT) on input signal charge.

- Intensify the discussion EIC accelerator experts on clock jitter, transmission, etc.

- Complete the redesign of the ALTIROC chip to meet the specifications of the Roman Pots of EIC (production expected beginning 2022)

- Study alternative, low-power ASIC technologies, and perform market survey of SiGe technology.

Radiation testing of SiGe technologies.

## Summary

- Simulation studies provide insight into both needed performance and expected challenges in implementation.

- Required layout, number of channels, backgrounds, timing, etc. implemented into GEANT simulations.

- All of the requirements from the physics simulations are on-track to be met by the AC-LGAD.

- With COVID hopefully ramping down, a return to normal operations in the laboratory and further access to test-beams for full prototype implementation will drastically improve this workflow.

- We are working towards building a large area sensors that meets all specs at the same time (time resolution, pixelation, edge size).

- ASIC development ongoing, and initial tests of compatibility with AC-LGAD promising.

- Work towards a first RP-compatible ALTIROC prototype.

- Further studies needed to minimize power dissipation.

- Discussions with accelerator experts to assess impact of clock, etc. ongoing.

- The LGAD Consortium for EIC will provide a framework to work collaboratively and share expertise for different detector applications

- e.g. we will benefit from expertise on cooling, mechanics, off-detector electronics.

- Expand effort to develop a more detailed detector architecture building from the Strawman layout.

- The 1st estimate of costs based on Strawman layout and ATLAS experience will become more accurate as designs becomes more detailed.

## Back Up

## ASIC development

- Strategy to modify ASIC (ALTIROC, CMS TSMC 130 nm) used in ATLAS timing detector (HGTD) and make it compatible to Roman Pot specs

- Extensive discussions between electronics experts at IJCLab/OMEGA, and sensors and EIC machine experts

- Main modifications have been identified to reduce pixel pitch from 1.3 mm to 500 um

- Low occupancy and triggerless EIC readout simplifies ASIC design, e.g. no need for SRAM

- Starting point is same front-and concept (preamplifier, discriminator and two TDC for Time of Arrival and Time Over Threshold)

- Replacing TDC with ADC and sampling pulses is under consideration to improve information of signal sharing

ASIC power dissipation of a 32x32 channel ASIC

Per pixel power dissipation of 3 mW (assuming 10% occupancy - very conservative!, as expected occupancy <<01%)

3.072 W per chip, including the peripheral electronics

1.067 W/cm² power density total power dissipation in the whole detector of 1.573kW (Strawman layout)

❖ For comparison ALTIROC for HGTD: 1.2 W/chip (300 mW/cm²) and 19.3kW total power dissipation

Optimization: thanks to lower AC-LGAD capacitance, transistor size in the preamp can be

reduced.

- The design of a 4x4 channels prototype will start at OMEGA in spring 2021 with an expected submission end 2021 (funds secured for prototype run).

Parallel effort by UCSC team together with Anadyne Inc. to develop an ASIC with 500 um pitch and power (<500 μW) using SiGe bipolar technology for speed and low power.

- On-going discussion with EIC accelerator experts:

250 fs is estimate EIC clock jitter RMS.

Long term drift of the clock will need to be assessed, but can be compensated.