# 8/18/2022 EPIC DAQ WG Agenda

- 1. Discussion to clarify timing system design

- 2. Updated EPIC detector readout summary

- Mini-updates from detector representatives

- Far Forward & Far Backward

- Si Tracking

- MPGD Tracking

- Calorimeters

- PID-TOF

- PID-Cherenkov

- 3. GD/I request for DAQ input to the FF/FB discussions next Monday

- 4. AOB

Requirements we have been discussing:

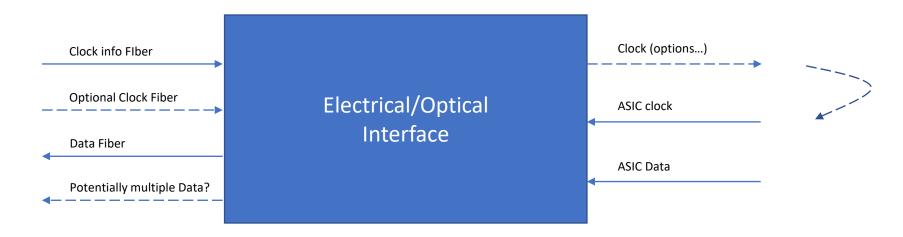

- General scheme for timing interface to Electrical/Optical boards will be home-grown FPGA based using COTS components

- Two versions:

- Hi Res:

- Dedicated clock fiber

- Phase stability relative to EIC BX <5ps (Both while operating and between power cycles)

- Jitter < ? (how is this impacted by phase requirements?)

- Low Res:

- Reconstructed clock from data in fiber

- Phase stability < 100ps?

- Jitter < ?

- Both systems

- Accept information protocol (ie. sPHENIX, or jlab) for busy/trigger/bunch identification/bunch characteristics. ~100 bits / BX.

- Handle flow control commands

- Handle configuration (JTAG & i2c)

- >10Gb/s per fiber (Discussed 40Gb/s...)

- We will NOT require that the ASIC/FEE use a BX derived clock for digitization

- We will specify headers for the data packets, but are agnostic regarding internal data packets format

- The data packets must provide sufficient information to reconstruct times relative the BX. Do we need to specify in the header some kind of scheme for tracking the relative phases & frequencies or leave that to specific detectors?

Issues to clarify:

- 1. EIC timing system  $\rightarrow$  DAM boards: Are the following assumptions correct?

- Interface to as yet unspecified EIC system

- Interface to DAQ Control in quasi-real time O(seconds)

- Run control

- Sensing of issues, single bit upsets, need to manage flow control, recovery etc...

- Tree of boards splitting EIC BX to O(100) DAM boards

- I assume location is DAQ room, and multiple technologies exist including copper so that the <5ps phase is not problematic

- 2. How should we be specifying requirements for the phase? It seems that the detectors are happy with 10-20ps resolution however I/we have been lax about distinguishing between resolution between specific components and full system resolution.

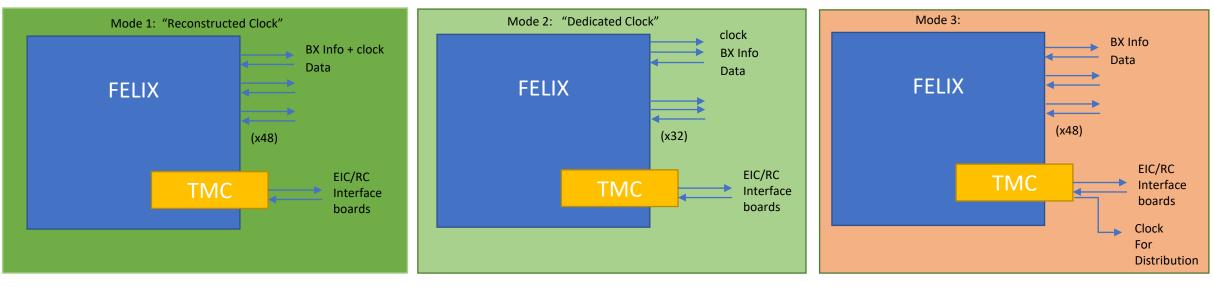

I'm trying to map my understanding of the FELIX features to our discussions of the Timing protocol:

- 3. FELIX board TMC (Timing Mezzanine Cards) features:

- 1. In general, is the expectation that the TMC has a separate fiber to the detector interface boards or use one of the 48 link pairs, or some combination?

- 2. When we discuss using a dedicated clock fiber, does the answer change?

- 3. Specific FELIX features:

- 1. Provides reference clocks for fiber transceivers (This is TMC  $\rightarrow$  DAM, correct?)

- 2. DAM sends busy info to timing system... But I'm not clear on what this means. Is this DAM  $\rightarrow$  TMC card, or DAM  $\rightarrow$  Fiber to detectors, or both?

- 3. Handling of the timing system info bits. Is this TMC card  $\rightarrow$  DAM  $\rightarrow$  fiber

4. Requirements for Electrical Optical Interface assuming FEE/ASIC clock is independent of BX clock, so

If the clocks are fully independent we'd need to measure phase, drift etc. Can we confidently leave this to FEE designers or do we need to specify, and if so how?

#### EPIC Detector Scale and Technology Summary:

| Detector System                                                                                                                                                                                   | Channels                                                                                                                          | Fiber pair                                                         | Data Volume                                                           | DAM Boards    | Readout Technology                                                                                     | Notes                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Si Tracking:<br>3 vertex layers,<br>3 sagitta layers,<br>4 backward disks,<br>5 forward disks                                                                                                     | 7 m^2<br>32B pixels<br>5,200 MAPS sensors                                                                                         | 300                                                                | 5Gb/sec                                                               | 6-8           | MAPS:<br>Several flavors:<br>curved its-3 sensors for vertex<br>Its-2 staves / w its-3<br>improvements |                                                                                                                                                                                       |

| MPGD tracking:<br>3 layers                                                                                                                                                                        | 100k                                                                                                                              | 200                                                                | <10Gb/sec                                                             | 4-5           | 64 channel SALSA ASIC                                                                                  | Assume 512 Channel (8 ASIC)/FEE                                                                                                                                                       |

| Calorimeters:<br>Forward: LFHCAL<br>pECAL<br>HCAL inset<br>Barrel: HCAL<br>ECAL<br>Imaging<br>Backward: ECAL                                                                                      | 60k<br>25k<br>8k<br>3k (25k?)<br>8k<br>50M pixels<br>25k                                                                          | 950<br>400<br>125<br>50(400)<br>125<br>(note)<br>400<br>2050(2400) | 15Gb/sec                                                              | 50            | SiPM using HGCROC &/or FPGA bases boards with FLASH ADC                                                | For imaging, if present:<br>"2 level data aggregation inside detector, 1 data link per<br>stave" ?staves?                                                                             |

| Far Forward:<br>B0: 3 MAPS layers<br>1 or 2 AC-LGAD layer<br>2 Roman Pots<br>2 Off Momentum<br>ZDC: Crystal Calorimeter<br>32 Silicon pad layer<br>4 silicon pixel layers<br>2 boxes scintillator | 3x20cmx20cm (300M pixel)<br>300k or 600k<br>1M (4 x 135k layers each)<br>650k (4 x 80k layers each)<br>400<br>11520<br>160k<br>72 | 6<br>30<br>64<br>42<br>10<br>10<br>10<br>2                         | 1Gb/sec                                                               | 5             | MAPS<br>AC-LGAG / EICROC<br>AC-LGAD / EICROC<br>AC-LGAD / EICROC<br>APD<br>HGCROC as per ALICE FoCal-E | 600 <sup>^</sup> cm layers (1 or 2 layers)<br>13 x 26cm layers<br>9.6 x 22.4cm layers<br>There are alternatives for AC-LGAD using MAPS and low<br>channel count DC-LGAD timing layers |

| Far Backward:<br>Low Q Tagger 1<br>Low Q Tagger 2<br>2 Calorimeters                                                                                                                               | 1.3M<br>480k<br>700                                                                                                               | 80<br>32<br>1                                                      | 100Gb/sec<br>(1 Gb/sec to tape)                                       | 4             | AC-LGAD / EICROC<br>AC-LGAD / EICROC<br>SIPM? PMT? MCPMT?                                              | 40cmx40cmx500um<br>30cmx20cmx500um                                                                                                                                                    |

| PID-TOF                                                                                                                                                                                           | 3M-50M                                                                                                                            | 240-500                                                            | 6Gb/sec                                                               | 6-12          | EICROC / AC-LGAD                                                                                       | Channel / Fiber counts depend on sensor geometry.<br>Considering pitches of:<br>.5mm x 1cm, .5mm x .3cm, .5mm x .5mm                                                                  |

| PID-Cherenkov:<br>dRICH<br>pfRICH (if selected)<br>mRICH (if selected)                                                                                                                            | 300k<br>225k<br>???                                                                                                               | 200<br>150<br>288                                                  | 1830Gb/s<br>(<20Gbps to tape)<br>1380Gb/s<br>(<15Gb/s to tape)<br>??? | 20<br>14<br>5 | SiPM / ALCOR<br>SiPM / ALCOR                                                                           | Worse case after radiation. Includes 30% timing<br>window. Requires further data volume reduction<br>(software trigger, or AI/ML)                                                     |

| DIRC                                                                                                                                                                                              | 74k                                                                                                                               | 288                                                                | 11Gb/sec                                                              | 6             | HDSoC64                                                                                                | 12 boxes x 24 sensor x 4 asic x 64 ch                                                                                                                                                 |

#### Summary of Channel Counts

| Detector<br>Group |      | Cha        | nnels    | Fibers | DAM  | Data   | Data                         |                             |

|-------------------|------|------------|----------|--------|------|--------|------------------------------|-----------------------------|

|                   | MAPS | AC/DC-LGAD | SiPM/PMT | MPGD   |      |        | Volume<br>Estimate<br>(Gb/s) | Volume<br>To Tape<br>(Gb/s) |

| Tracking          | 32B  |            |          | 100k   | 500  | 335013 | 15                           | 15                          |

| Calorimeters      | 50M  |            | 150k     |        | 2050 | 50     | 15                           | 15                          |

| Far Forward       | 300M | 2.3M       | 500      |        | 174  | 5      | 1                            | 1                           |

| Far Backward      |      | 1.8M       | 700      |        | 113  | 4      | 100                          | 2                           |

| PID               |      | 3M-50M     | 600k     |        | 638  | 40     | 3220                         | 45                          |

| TOTAL             | 32B  | 7.1M-54M   | 750k     | 100k   | 3475 | 112    | 3350                         | 78                          |

# 8/18/2022 EPIC DAQ WG Agenda

- 1. Discussion to clarify timing system design

- 2. Updated EPIC detector readout summary

- Mini-updates from detector representatives

- Far Forward & Far Backward

- Si Tracking

- MPGD Tracking

- Calorimeters

- PID-TOF

- PID-Cherenkov

- 3. GD/I request for DAQ input to the FF/FB discussions next Monday

- 4. AOB