# A 3ps Cryogenic Time-to-Digital Converter for Time-Correlated Single Photon Counting

Adam Quinn

11/29/2022

**CPAD 2022**

## **Better TDC Precision Looks Like...**

Image Credit NASA [1]

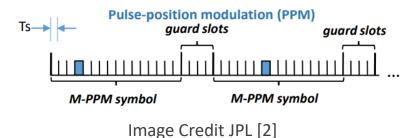

... higher bit-rates in DSOC.

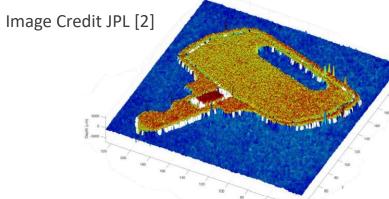

... ultra-high resolution range-finding. (1 ps  $\approx$  0.3 mm)

# Why (This) TDC?

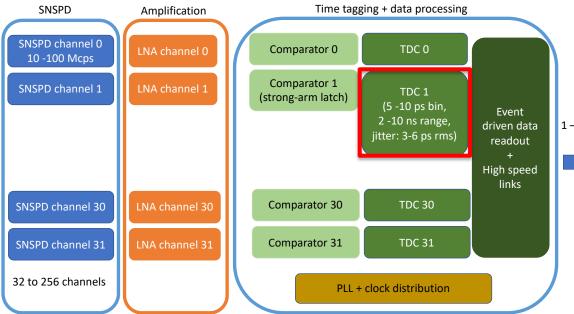

**The Challenge:** High-bandwidth time-correlated single photon counting in a cryogenic environment.

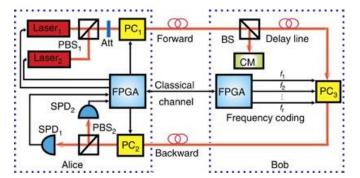

A Quantum Secure Direct Communications System (Hu [10])

1 – 10 Gcps

## **Proposed Application:**

SNSPD-based space-toground quantum communications terminal for the ISS

DOE NASA RFI 86 FR6315 [4]

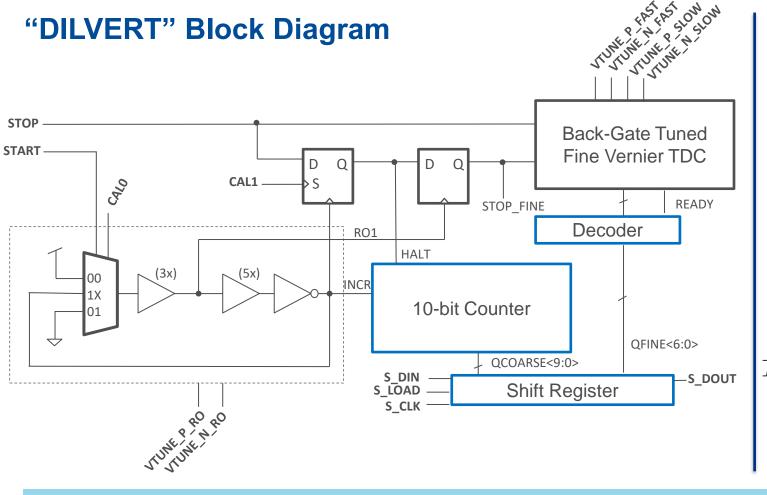

#### **Total Pins: 22**

- 6 analog inputs

- 7 digital inputs

- 3 digital outputs

- 6 power pins

#### Not Shown:

- \* RO1, HALT, INCR, and STOP FINE are mux'd to two digital outputs with the select done by 4 shift register bits.

- \* RESET pin

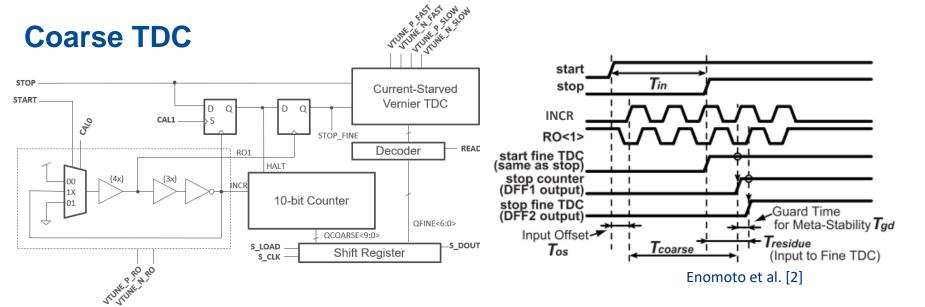

Enomoto et al. [2]

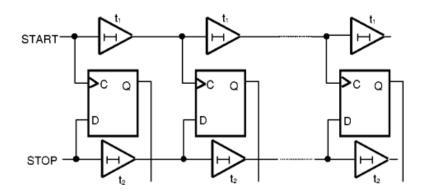

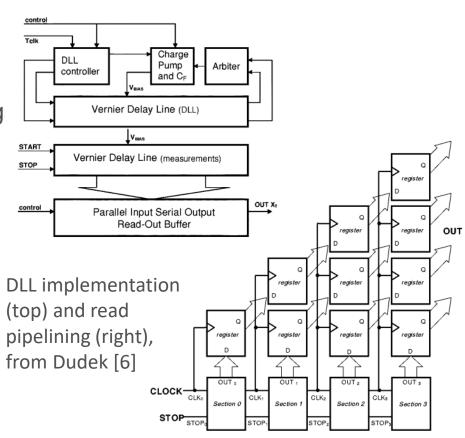

### Fine Vernier TDC

Illustration from Dudek [1] (in our TDC, latches are used instead of DFFs)

- t<sub>1</sub> and t<sub>2</sub> are tuned to be very close to each other.

- 1 LSB =  $t_{R(fine)} = (t_2 t_1)$

- STOP is always faster than START.

- If START arrives first at stage n, Q[n]=1

- Result is thermometer-coded: "How many LSBs does it take for STOP to catch up to START?"

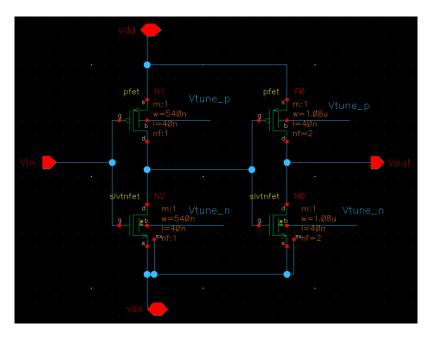

# **Delay Tuning with Back-Gate Bias**

Fine TDC Delay Stage

- Fine TDC delay cells and RO delay cells are same architecture (different sizing)

- Speed is tuned by FDSOI back-gate biasing

- Low complexity

- Small footprint

- No noise contribution from bias circuits

- 6 separate tuning voltages:

- Fine TDC fast chain, slow chain, and coarse TDC ring oscillator

- Tune NMOS and PMOS separately.

- Both 0~2V w.r.t VSS

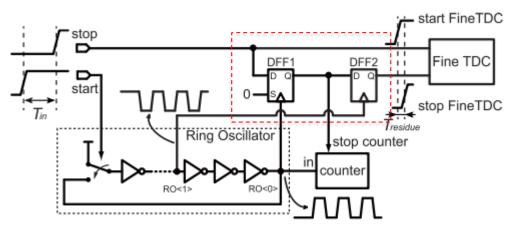

START starts the ring oscillator. The counter counts up until STOP, and the residue is encoded by the fine TDC:

$$T_{in} = T_{OS} + T_{coarse} + T_{gd} - T_{residue}$$

$$= (T_{OS} + T_{gd}) + N_{coarse}(t_{R(coarse)}) - N_{fine}(t_{R(fine)})$$

# **Coarse-to-Fine Coupling with DFFs**

Enomoto, et al. [2]

• Traditional TDCs couple with a multiplexer  $\rightarrow$  unwanted  $T_{D\rightarrow Q}$ , possibly different for different inputs.  $\odot$

- In our design, DFF1 is triggered on the first coarse TDC increment after STOP arrives. (With constant offset T<sub>clk→Q</sub>)

- The remainder  $(t_{incr} t_{STOP})$  is digitized by the fine TDC.

- Why have DFF2? STOP and RO<0> are asynchronous, so we need to suppress any metastability in DFF1's output before the fine TDC.

- DFF2 is triggered slightly after DFF1  $(T_{incr} + T_{gd})$ . We assume DFF1's output has settled within  $T_{ad}$ .

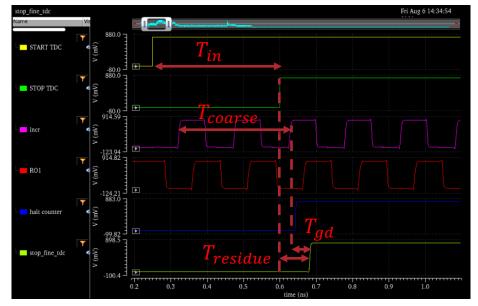

## **Example Measurement**

From Three Point Calibration, we have:

$$t_{R(fine)} = -2.6375 \text{ ps}$$

$t_{R(coarse)} = 152.75 \text{ ps}$

$T_{OS} + T_{ad} = -173.62 \text{ ps}$

For this measurement,  $Q_{fine} = 33$  and  $Q_{coarse} = 4$ , so:  $T_{in} = T_{OS} + T_{coarse} + T_{gd} - T_{residue}$   $\approx 350.343 \text{ ps}$

(Actual  $T_{in}$  was 350 ps, within 1 LSB of the measured value.)

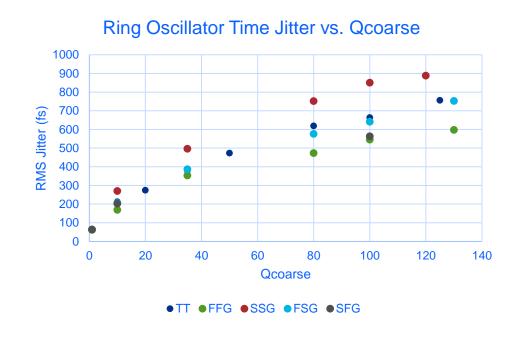

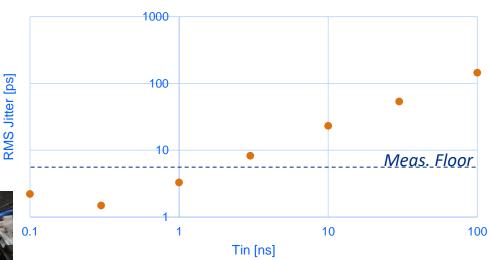

# Simulation Results: TDC Jitter vs $T_{in}$

$$\sigma_{jitt} = \sigma_{tp} \times \sqrt{N_{stage} \times 2} \times \sqrt{Q_{coarse}}$$

$$= \kappa_{jitt} \sqrt{Q_{coarse}}$$

Assuming that maximum allowable jitter is approximately ½ LSB:

| Corner:                   | TT          | FF   | SS   | FS   | SF   |

|---------------------------|-------------|------|------|------|------|

| κ <sub>jitt</sub> [fs]    | 66.18       | 55.9 | 80.7 | 65.0 | 61.7 |

| $\sigma_{jitt(max)}$ [fs] | 1.3         | 1.0  | 1.8  | 1.4  | 1.2  |

| $Q_{coarse(max)}$         | 385         | 320  | 497  | 463  | 378  |

| Dynamic<br>Range [ns]     | <u>55.4</u> | 40.2 | 83.7 | 68.5 | 53.1 |

## State of the Art

|                  | Chen '17 | Sesta '18                          | Enomoto<br>'19                          | Palaniappan<br>'19                 | Khaki '21         | Lee '21  | DILVERT<br>(sim) '21               |

|------------------|----------|------------------------------------|-----------------------------------------|------------------------------------|-------------------|----------|------------------------------------|

| Architecture     | ΔΣ TDC   | Counter +<br>Vernier Delay<br>Line | Counter +<br>Pulse-Shrink<br>Delay Line | Cap Boost<br>Vernier Delay<br>Line | ΔΣ TDC<br>w/ GSRO | SAR TDC  | Counter +<br>Vernier Delay<br>Line |

| Process          | 65nm     | 0.35 μm                            | 0.18 μm                                 | 180 nm                             | 40nm<br>FPGA      | 130nm    | 22nm SOI                           |

| Resolution       | 0.48 ps  | 7 ps                               | 2.0 ps                                  | 1.74 ps                            | 0.18 ps           | 6.6 ps   | 2.7 ps                             |

| Dynamic<br>Range | -        | 80 ns                              | 120 ns                                  | 0.112 ns                           | 4.5 ns            | 1.7 ns * | 55.4 ns                            |

| Power            | 3 mW     | -                                  | 18 mW                                   | 0.217 mW                           | 9.24 mW           | 0.504 mW | 0.5 mW                             |

| Rate             | -        | 20 MS/s *                          | 3.3 MS/s                                | 50 MS/s                            | 1600 MS/s         | 10 MS/s  | 100 MS/s                           |

| FoM              | -        | -                                  | 3.33                                    | 0.30                               | 2.71              | 0.51     | 41.04                              |

$FoM = \frac{[Dynamic Range in ns]}{[Power in mW][Resolution in ps]}$

\* = calculated from available data

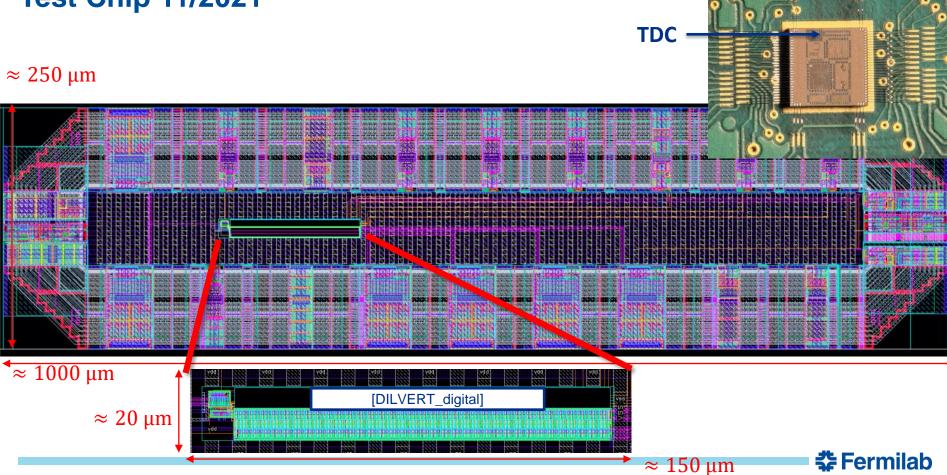

# **Test Chip 11/2021**

## **Preliminary Test Results (Room Temperature)**

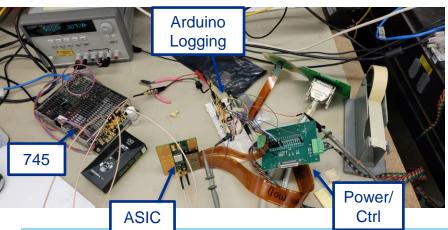

- Two pulses generated with Berkley Nucleonics 745-OEM (~ 5 ps rms jitter)

- RO runs slower and with more excess jitter than expected at room temperature.

- Cryo testing in progress.

#### **Warm Simulation:**

| tR(coarse) | 220.2 ps |

|------------|----------|

| tR(fine)   | -6.0 ps  |

| tOS        | 486.3 ps |

#### **Measurement:**

| tR(coarse) | 524.4 ps  |

|------------|-----------|

| tR(fine)   | -8.1 ps   |

| tOS        | -463.1 ps |

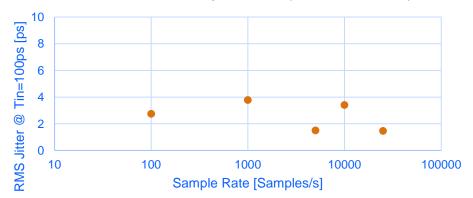

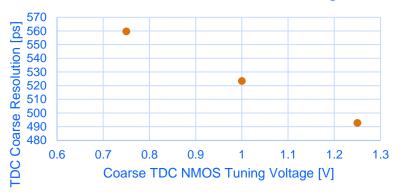

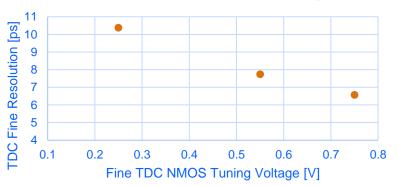

# Performance vs Tuning Voltage & Sample Rate (Room Temperature)

- Demonstrated 25 kS/s, limited by readout chain.

- TDC Tuning slope: ≈134 ps/V (coarse)

≈7.6 ps/V (fine)

#### RMS Jitter vs Sample Rate (100 ~ 25 kS/s)

#### **TDC Coarse Resolution vs Tuning**

#### TDC Fine Resolution vs Tuning

### What's Next?

- Continue test chip characterization

- Multi-Channel Prototype: Power Saving in Ring Osc. / Clock Distribution

- Full-Channel Integration (SNSPDs, Comparators, etc.)

- Replica TDC for Delay-Locking

- High-Speed Read Pipelining

- Skewed Inverter Topologies

## **Thanks to Contributors**

## **Fermilab ASIC Department:**

D. Braga, F. Fahim, L. Dal Monte, P. Rubinov, P. Klabbers

### References

- [1] Harbaugh, J. (2017, May 22). *Deep Space Optical Communications (DSOC)*. NASA. Retrieved October 3, 2021, from https://www.nasa.gov/mission\_pages/tdm/dsoc/index.html.

- [2] Jet Propulsion Laboratory, California Institute of Technology. (2018). Superconducting Nanowire Single Photon Detectors For Deep Space Optical Communication.

- [3] Ho, R., Mai, K., & Horowitz, M. (2001). The future of wires. Proc. IEEE, 89, 490-504.

- [4] Fermi National Accelerator Laboratory. (2021). *Joint DOE-NASA development of custom readout electronics for Superconducting Nanowire Single Photon Detector* (p. 1).

- [5] SLAC National Accelerator Laboratory. *TDC development for future detectors: Initial technology evaluation*. U.S. Department of Energy Office of Science.

- [6] P. Dudek, S. Szczepanski and J. V. Hatfield, "A high-resolution CMOS time-to-digital converter utilizing a Vernier delay line," in *IEEE Journal of Solid-State Circuits*, vol. 35, no. 2, pp. 240-247, Feb. 2000, doi: 10.1109/4.823449.

- [7] R. Enomoto, T. Iizuka, T. Koga, T. Nakura and K. Asada, "A 16-bit 2.0-ps Resolution Two-Step TDC in 0.18- μm CMOS Utilizing Pulse-Shrinking Fine Stage With Built-In Coarse Gain Calibration," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 27, no. 1, pp. 11-19, Jan. 2019, doi: 10.1109/TVLSI.2018.2867505.

- [8] B. V. Bockel, P. Leroux and J. Prinzie, "Tradeoffs in Time-to-Digital Converter Architectures for Harsh Radiation Environments," in *IEEE Transactions on Instrumentation and Measurement*, vol. 70, pp. 1-10, 2021, Art no. 2005710, doi: 10.1109/TIM.2021.3100355.

- [9] Global Foundries. 22FDX Design Kit and Technology Training Book. TTM-000022 Revision 9.

- [10] Hu, Jianyong & Yu, Bo & Jing, Ming-Yong & Xiao, Liantuan & Jia, Suotang & Qin, Guo-Qing & Long, Gui. (2016). Experimental quantum secure direct communication with single photons. Light: Science & Applications. 5. e16144. 10.1038/lsa.2016.144.