# Precision timing ASIC (ETROC) development for LGAD-based detector for CMS upgrade, and future prospect and challenges

Ted Liu (Fermilab),

Dec 1st, 2022, CPAD meeting

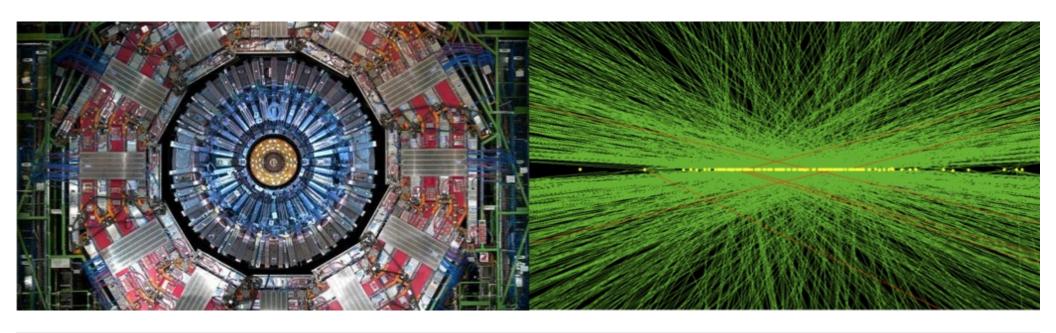

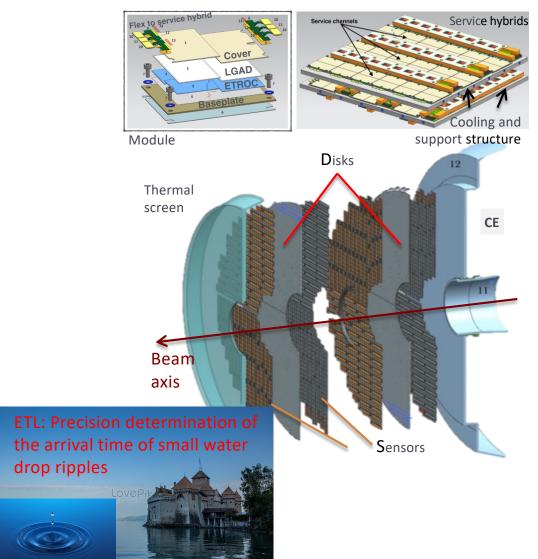

# ETL precision timing challenges

- Low Gain Avalanche Detectors (LGADs)

- Basic unit:

- 2x2 cm<sup>2</sup> LGAD bump-bonded to ETROC ASIC mounted on two sides of cooling plates

- Two layers/disks per endcap (~2 hits per track)

- 1.6 <  $|\eta|$  < 3.0, surface ~14 m<sup>2</sup>; ~9 M channels

- Nominal fluence:  $1.7x10^{15} n_{ea}/cm^2$  (@ 3000 fb<sup>-1</sup>)

- LGAD gain modest: 10-30

- LGAD Landau contribution: ~ 30ps

- Front-end contribution should be kept < 40ps

- < 50ps per hit, or 35ps per track (with 2 hits)</p>

- Extract precision timing from

Small LGAD signal (typical 10-20 fC)

With low power: < 4mW/channel on average</p>

#### **Challenges:**

Low power and fast/precision timing, Precision clock distribution, Minimizing readout digital activities

## Design considerations for precision timing detector

- System power and cooling constraint and how it influences ASIC design

- Design methodology to optimize front-end from system point of view

- Single layer detector vs multi-layer (ETL design: 1 layer → 2 layer)

- TDC design choice: needs ultra low power → new design

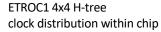

- Precision clock distribution considerations: from system to detector, to chip, to pixel and to each TDC delay unit (using H-tree approach)

- Design to enhance physics reach:

- such as detection/trigger for long live particles, with wide TDC window

- Design for monitoring and calibration considerations: waveform sampler

- Time-frame of ASIC development: "several mini-ASICs vs. single full ASIC"

•••

### Will not have time to get into these in this talk ....

Proper System Design is the Key to the success of any challenging ASIC project

A good design is a compromise between system design and ASIC design

The approach: "ASIC == A System design Including a Chip"

ETROC2 is designed in such a way as if it is the final design for full functionalities

(with extra flexibilities for performance study purpose)

# For technical details, please see ETROC papers and recent talks. This talk only has few highlights, then on future prospect and challenges

Characterization of the CMS Endcap Timing Layer readout chip prototype with charge injection

https://iopscience.iop.org/article/10.1088/1748-0221/16/06/P06038

The Analog Front-end for the LGAD Based Precision Timing Application in CMS ETL

https://arxiv.org/abs/2012.14526

IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 68, NO. 8, AUGUST 2021

A Low-Power Time-to-Digital Converter for the CMS Endcap Timing Layer (ETL) Upgrade

https://ieeexplore.ieee.org/document/9446843

#### In-pixel automatic threshold calibration for the CMS Endcap Timing Layer readout chip

https://iopscience.iop.org/article/10.1088/1748-0221/16/09/T09006

FERMILAB-CONF-20-549-E

#### A New Scheme of Redundant Timing Crosschecking for Frontend Systems

https://ieeexplore.ieee.org/document/9447027

# A 2.56 GS/s 12-bit 8x-Interleaved ADC with 156.6 dB FoMs in 65 nm CMOS

#### 2022 TWEPP talks related to ETROC:

From ETROC1 to ETROC2:

https://indico.cern.ch/event/1127562/contributions/4904521/ (TWEPP 2022, Tuesday)

ETROC Emulator:

https://indico.cern.ch/event/1127562/contributions/4904781/ (TWEPP 2022, Wed)

**ETROC Waveform Sampler:**

https://indico.cern.ch/event/1127562/contributions/4904540/ (TWEPP 2022, Thursday)

TDC with Uncontrolled Delay lines: calibration approach and method

https://indico.cern.ch/event/1127562/contributions/4904530/ (TWEPP 2022, Thursday)

IEEE Transactions on Very Large Scale Integration Systems (TVLSI), Volume: 30, Issue: 2, Feb. 2022) Page(s): 123 – 133

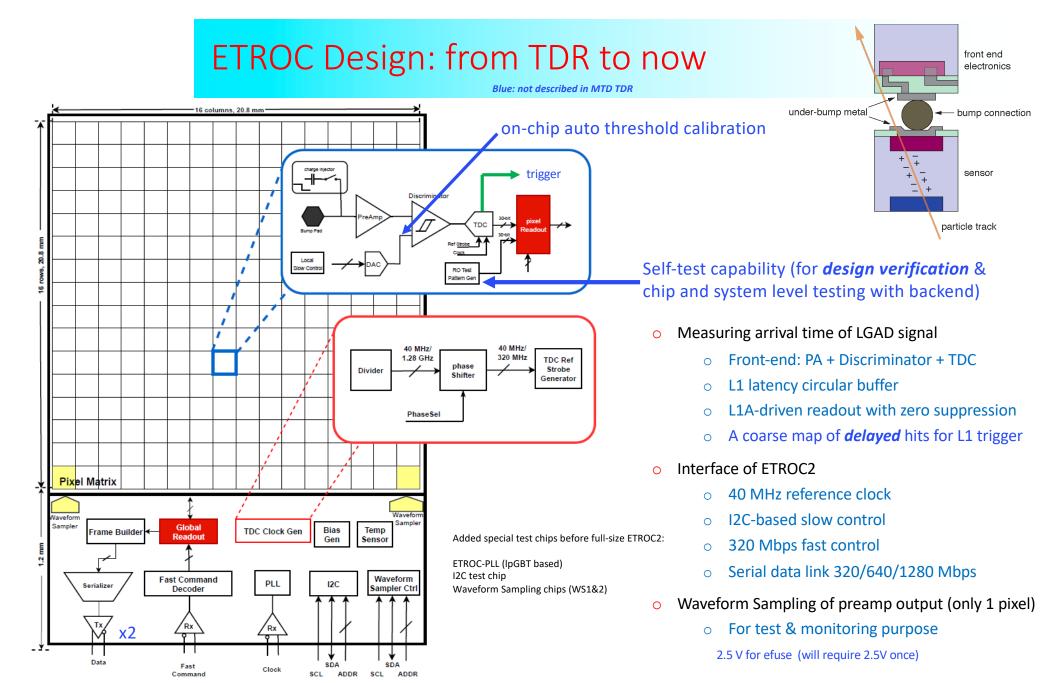

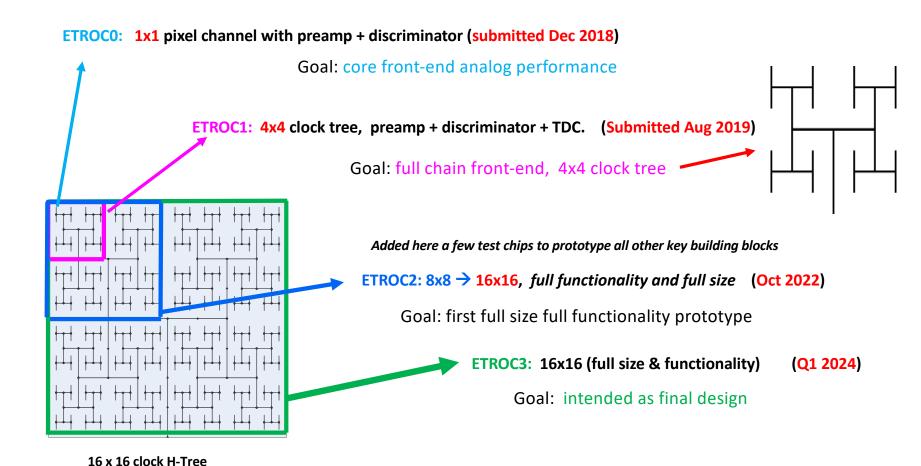

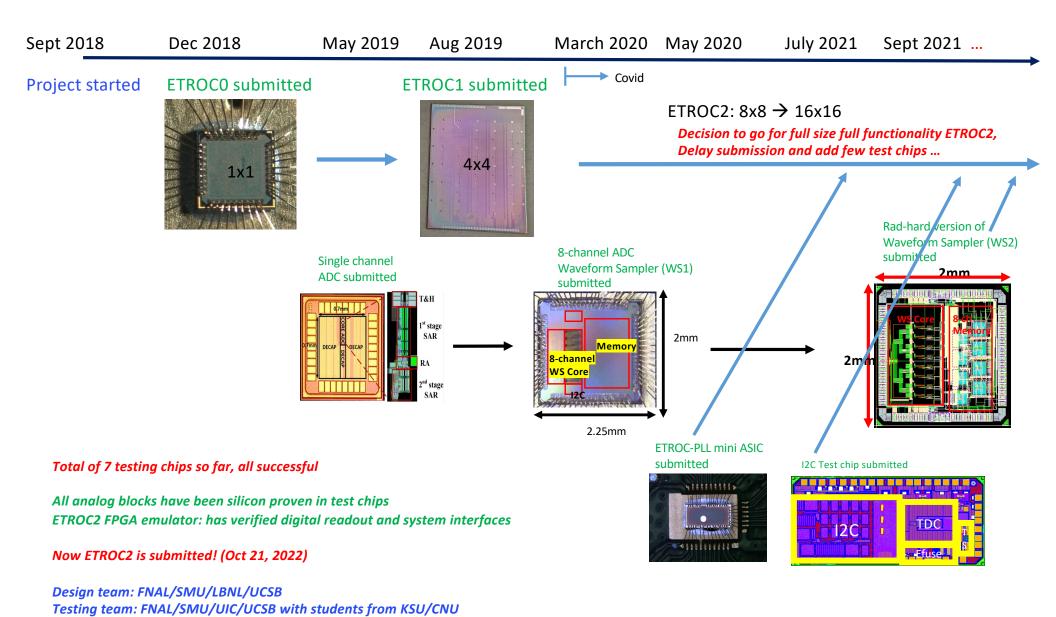

## ETROC Development Strategy & Schedule

## **ETROC** prototyping history

## **ETROC Overall Status**

- ETROC0 (single channel, preamp + discriminator)

- Charge injection/Cosmic/Laser done

- TID test to 100Mrads done

- Beam testing: ~30ps achieved in beam.

- ETROC1 (4x4), preamp + discriminator + new TDC

- New TDC extensively tested: excellent performance and low power (<~6ps resolution)</li>

- Bare ETROC1 charge injection testing: excellent performance (~10ps resolution with charge injection)

- ETROC1 and 5x5 LGAD sensor bump-bonded

- Encountered noise related to 40MHz memory activity after bump bonding with senso

- Noise source identified and understood, addressed in ETROC2 design

- Beam testing: results from beam telescope with LGAD at higher gain

- Obtained down to ~ 40ps per hit at system level in beam in 2021

- Second round of beam testing in 2022, results consistent

- ETROC1 TID testing (to be done, delayed due to COVID)

- Towards ETROC2 (16x16)

- ETROC PLL mini-ASIC (with lpGBT PLL core): test results very good, including SEU

- Waveform Sampler prototypes and I2C test chip work well.

- ETROC2 emulator (for pixel and global readout) works well

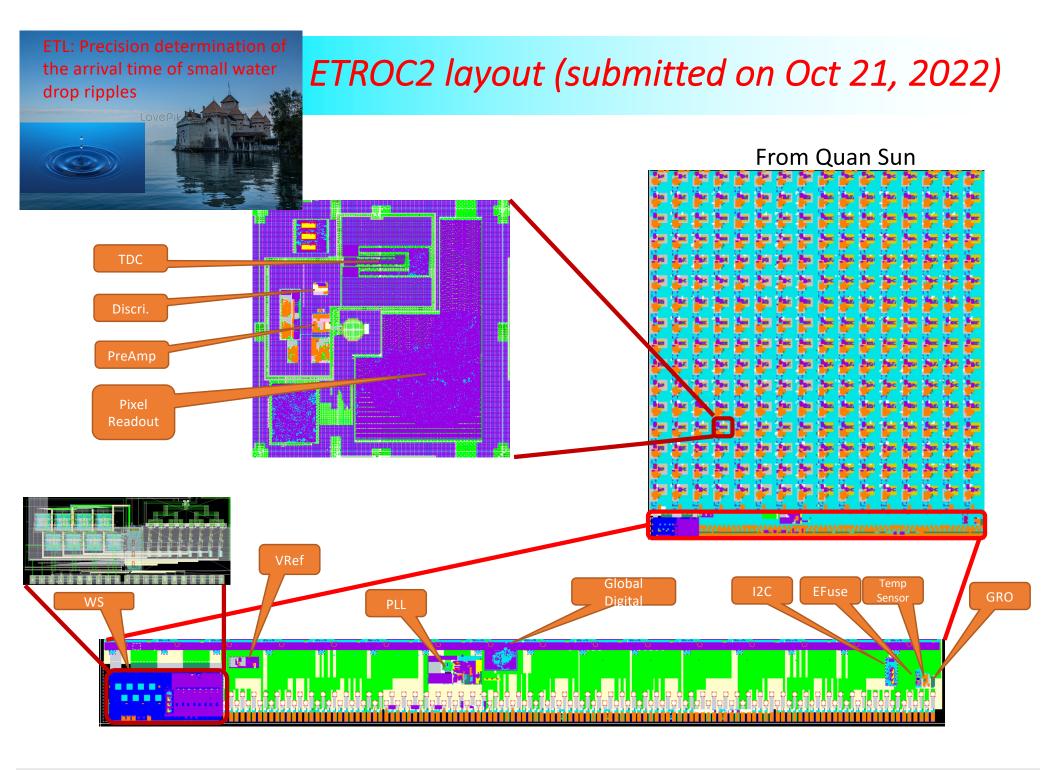

- ETROC2 design submitted in Oct 2022

- ETROC3: intended as final version, submission in 2024

Dedicated Technical Reviews in the past (by God Parents and CERN CHIPS and ASIC Support):

Three God Parents reviews (2018-2021)

ETROC2 features review (Oct 2021)

ETROC2 pre-submission review (July 20th, 2022)

ETROC2 final submission review (Oct 7<sup>th</sup>, 2022)

ETROC2 final submission to IMEC (Oct 21, 2022)

ASIC design: FNAL/SMU/LBNL

Testing: FNAL/SMU/UIC/KSU/KNU/CNU

& in collaboration with IpGBT team,

with help from:

**ETROC God Parent Committee**

CERN ASIC Support & CHIPS for ETROC2,

Torino/UCSC groups (sensor),

and Barcelona group (bump bonding)

Due to limited time, this talk will only have few highlights

The ETROC2 design has been extensively reviewed by experts

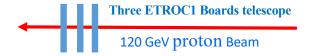

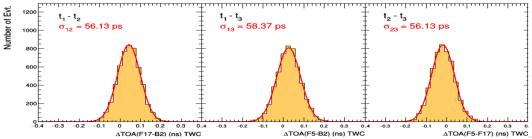

#### A simple ETROCO Beam Telescope (with 3 HPK-ETROCO boards)

Simple "suitcase" setup in parasitic mode running at FNAL MTest Jan-Feb 2020  $\sigma_2 = \sqrt{0.5 \cdot (\sigma_{21}^2 + \sigma_{32}^2 - \sigma_{31}^2)}$   $\approx 33 \ (ps)$ t3 t2 t1 Ch 3 2 1 120 GeV proton Beam preamp waveform t3-t1 HV230 t2-t1 HV230 t3-t2 HV230 entries: 1892 std: 0.0638 mean: 0.17 entries: 1892 std: 0.0577 mean: 0.43 entries: 1892 std: 0.0547 mean: -0.26 200 175 200 150 57.7ps 54.7ps 63.8ps 150 E 125 E 150 E 100 3 100

Time Resolution(ns)

50

0.3

Time Resolution(ns)

11/30/22

0.2

ETROC project, Ted Liu

-0.5 -0.4 -0.3 -0.2 -0.1 0.0

At room

temperature

p 9

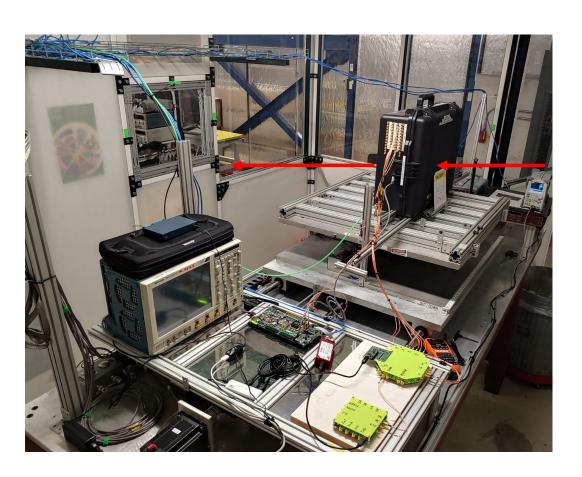

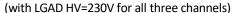

#### ETROC1 Beam Telescope @ FTBF

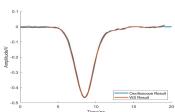

Precision timing full chain signal processing: preamp  $\rightarrow$  discriminator  $\rightarrow$  TDC (TOA/TOT) $\rightarrow$  output with external and internal precision clock distributions

#### 2021 vs 2022 Test Beam test results

ch1 (pixel 5)

Clock distribution

# Simulation /expectation vs spec

| LGAD+ preamp/discriminator + TDC bin     | 35 ps   |       |

|------------------------------------------|---------|-------|

| Time-walk correction residual            | < 10 ps |       |

|                                          | < 10 ps |       |

| Internal clock distribution              |         |       |

| System clock distribution                | < 15 ps |       |

| Per hit total time resolution            | 41 ps   | 50 ps |

| Per track (2 hits) total time resolution | 29 ps   | 35 ps |

ch2 (pixel 5)

**Three ETROC1 Boards telescope**

120 GeV proton Beam

Ch 3 2 1

ch3 (pixel 5 or 9)

The measured time resolution includes all four contributions in the table

#### Single-hit timing resolution (ps) with TWC:

$$\sigma_{i} = \sqrt{0.5 \cdot \left(\sigma_{ij}^{2} + \sigma_{ik}^{2} - \sigma_{jk}^{2}\right)}$$

~ 42.0/42.7/41.3 ps (2021 beam test)

~ 41.3/38.0/41.3 ps (2022 beam test)

reproduced last year's beam test results, with new ETROC1 boards and independent analysis

(2022 beam test mostly done by 4 graduate students)

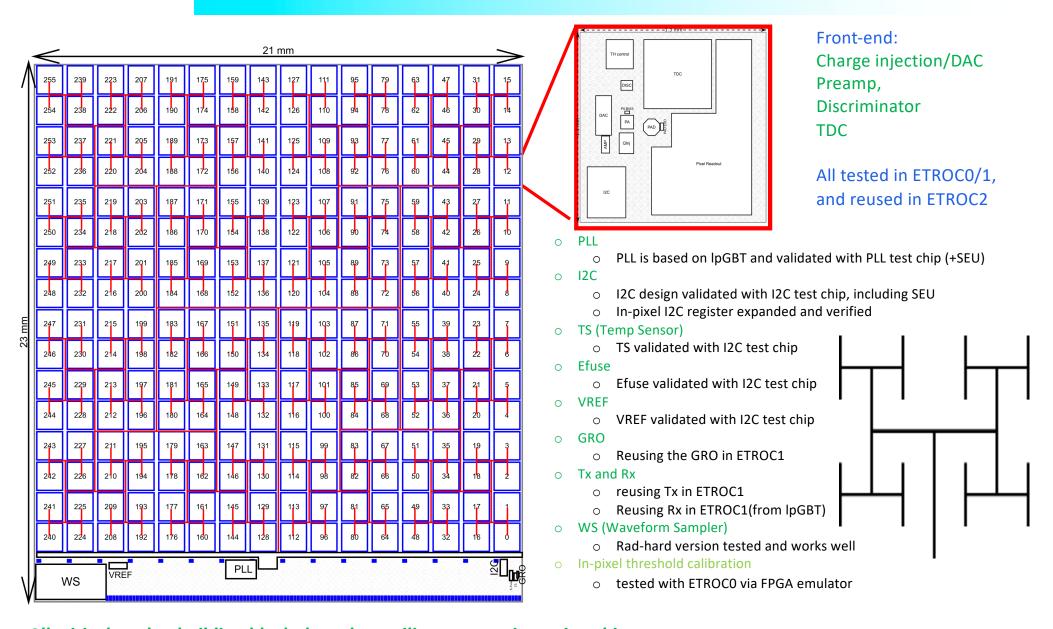

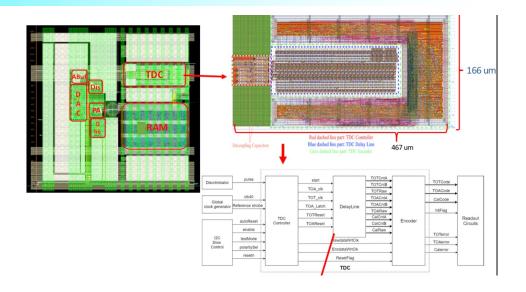

#### ETROC2 design: most building blocks have been silicon proven

All critical analog building blocks have been silicon proven in testing chips, and the digital building blocks have been emulated in FPGA and tested with the downstream readout board with backend.

# ETROC2 key features: from user point of view

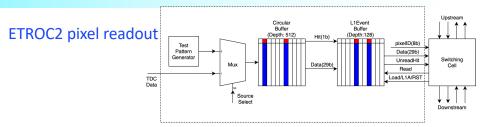

- Self-test pattern generator

- Can be used to test the digital data flow and link interfaces. Users can dial the occupancy of pixels and change patterns

- This feature has been used extensively to simulate and verify the readout design of ETROC2, at RTL level and post layout stage

- First thing user can test with ETROC2 emulator, the same test can then be done for bare ETROC2 and bump bonded ETROC2

- At chip level (as build in self-testing capability), board level, and system level (with DAQ backend)

- Testing with charge injection

- Test the full path from charge injection to preamp to discriminator to TDC to circular buffer to event buffer to global digital readout

- Discriminator threshold scan and jitter measurements (bare ETROC2 first, then bump bonded ETROC2)

- User can define the window for TOA, TOT and CAL to filter/suppress hits before readout

- User adjustable TOA measurement window (up to 12.5ns, 11.4ns effective)

- Each pixel can be enabled or disabled for DAQ readout

- The relative phases adjustable between the TDC clock, pixel readout clock and global readout clock

- Bump bonded ETROC2 testing with laser, source and then beam

- Full path timing performance study including LGAD

- Auto-threshold scan within pixel

- This new feature will be studied first by dedicated ETROC2 chip level testing

- Trigger path

- Can be used for monitoring purpose initially, a coarse map of user defined hits continuously sent out every BC

- Can be used for self triggering for beam test if so desired, user can define the window for TOA, TOT and CAL for triggered hit

- Use flashing bits in empty BCID (beam gap), defined via I2C. Can be used as cross check and monitoring purpose.

- Waveform Sampler

- Able to record waveform of one pixel up to 16 bunch crossing (400 ns), start and stop controlled via fast command, readout via I2C

- power-down when not used, intend to use for monitoring purpose during detector operation

- Power consumption estimate is ~1W per chip, to be confirmed with ETROC2 chips

https://indico.cern.ch/event/1127562/contributions/4904540/

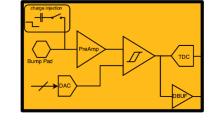

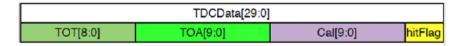

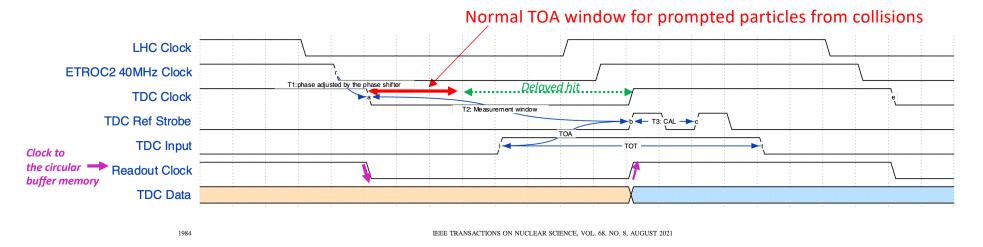

# **TDC** operation

hitFlag: discriminator is fired or not

- ☐ bin= T3/Cal\_code

- ☐ TOA=12.5 bin\*TOA\_code

T3 is programable with, 3.125 ns by default.

A Low-Power Time-to-Digital Converter for the CMS Endcap Timing Layer (ETL) Upgrade

https://ieeexplore.ieee.org/document/9446843

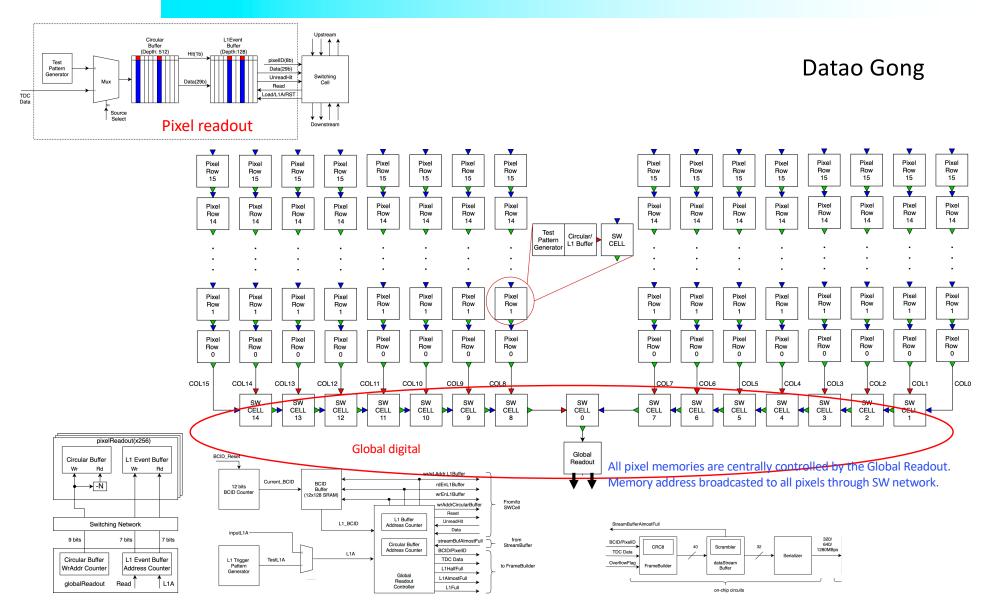

#### The overall ETROC readout

The ETROC2 emulator will emulate the entire ETROC2 digital processing chain. Details see talk at TWEPP 2022,

"An FPGA-based readout chip emulator for the CMS ETL detector upgrade" by Tiankuan Liu/Jinyuan Wu. <a href="https://indico.cern.ch/event/1127562/contributions/4904781/">https://indico.cern.ch/event/1127562/contributions/4904781/</a>

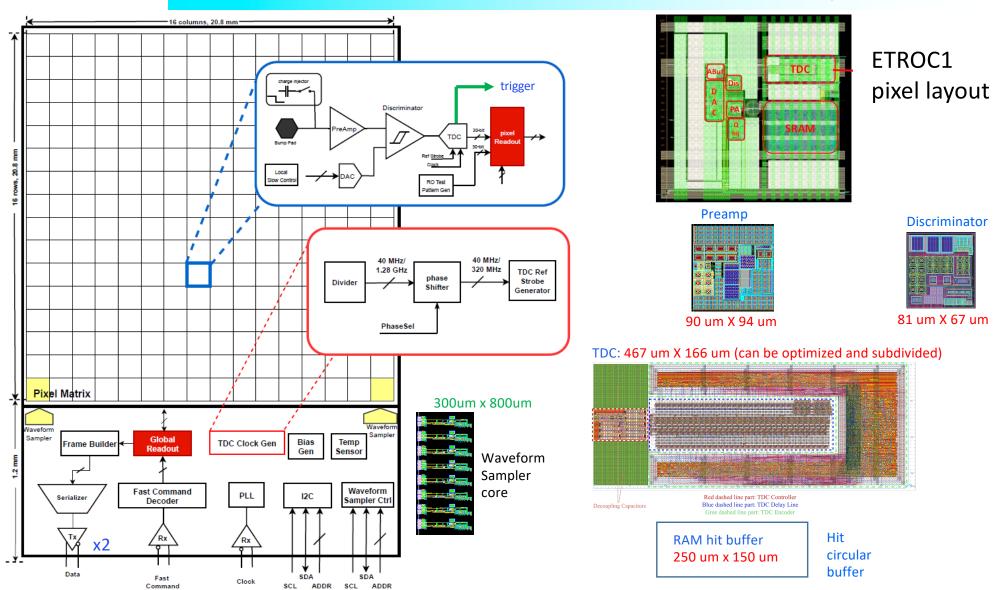

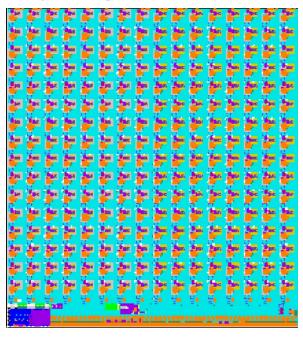

## ETROC: pixel size vs design block size

65nm implementation

Future challenges: how to reduce the pixel size from 1.3mm x 1.3mm to say 250μm x 250μm?

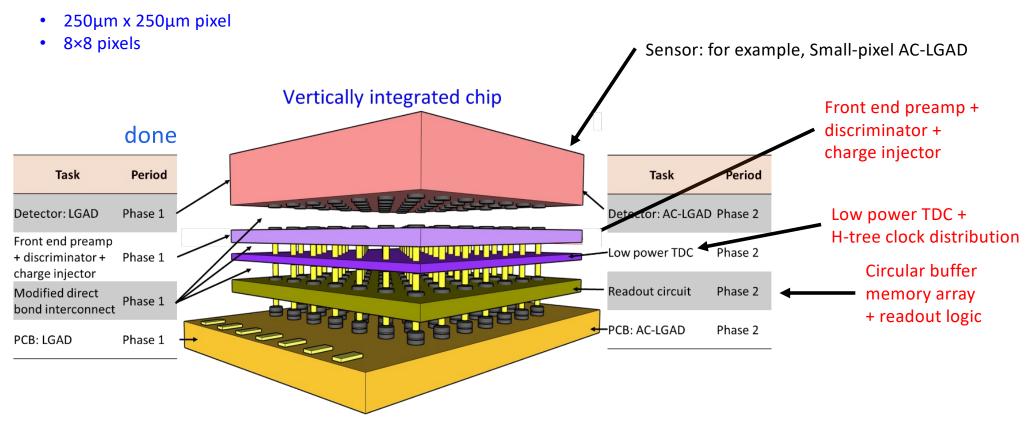

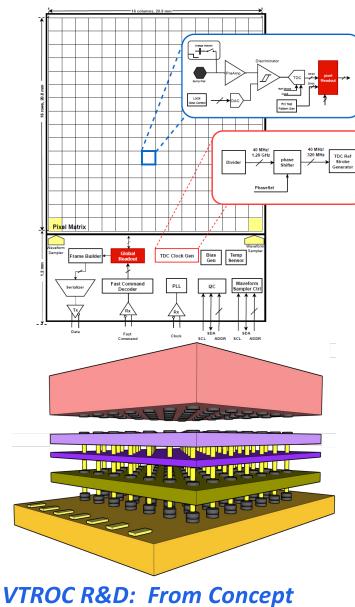

# Towards the future: What can 3DIC VERTICAL INTEGRATION help? → repartition the design blocks into multi-tiers

#### Phase II SBIR proposal (EPIR-Fermilab):

"Versatile, high-density, high-yield, low-capacitance

3D integration for nuclear physics detectors" (phase 2)

For Proof-of-principle demonstration:

3DIC providing separation of low-noise analog circuitry from digital blocks. Interconnections made by TSVs and Direct Bond Interconnect (DBI).

# From CMS ETROC to future R&D

CMS ETL ETROC: from Concept (2019) to full chip design ETROC2 submission (Oct 2022)

"Versatile, high-density, high-yield, low-capacitance

3D integration for nuclear physics detectors" (phase 2)

Phase 1 done

Phase 2 proposal submission next week

first demonstration for proof-of-principle

to