# Highly-scalable, Cryogenic Readout Electronics LArPix & LightPix

Brooke Russell

CPAD Workshop

December 1, 2022

#### Granular readout electronics for cryogenic applications

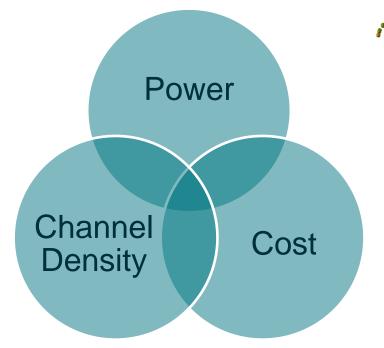

Key challenge: scalability

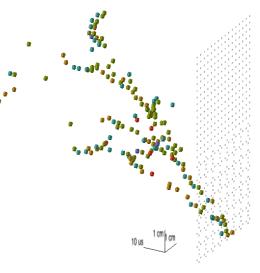

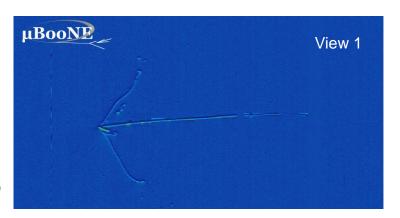

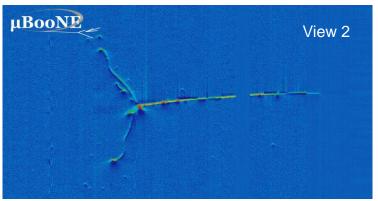

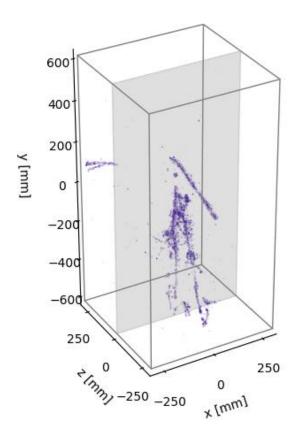

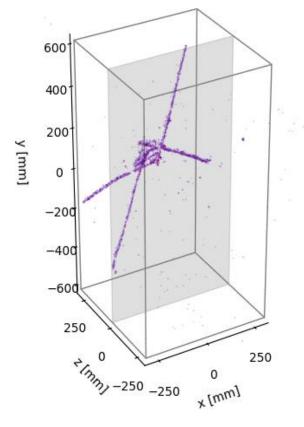

LArPix-v1 recorded cosmic EM shower

First proof of principle demonstration by Dan Dwyer *et al. JINST 13 (2018) P10007*

LArPix: scalable LArTPC pixel readout

LightPix: scalable, cryogenic-compatible SiPM readout

OF NEW JERSEY

UC SANTA BARBARA

UNIVERSITÄT **BERN**

### Why pixels?

- True 3D imaging *Unambiguous, inherently 3D <u>raw</u> data*

- Self-triggered pixel-by-pixel data

~100% livetime

Technical challenge: instrumenting ~1000 m² anode area at 4 mm granularity → requires scalable design

Pixel readout (LArPix cosmics data)

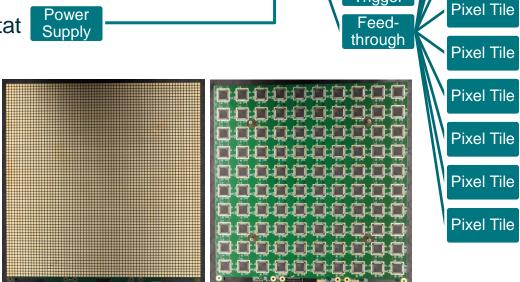

### **LArPix System Architecture**

A contained, end-to-end system focused on reliability & robustness

- Limit single-point failures

- Scalable to O(M) channel systems

#### Design features

- Single active component in cryo environment

- Minimal and redundant connections to outside cryostat

- Mechanically and cryogenically robust

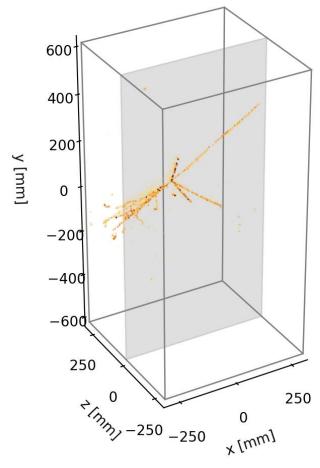

PACMAN Warm Controller

Feedthrough

Warm

Controller

32 cm by 32 cm anode PCB tile

Timing

Fiber

Ethernet

Switch

Master

DAQ

Pixel Tile

**Pixel Tile**

Pixel Tile

Pixel Tile

LRO

Trigger

Clock

Sync

External

Trigger

Pixel Tile

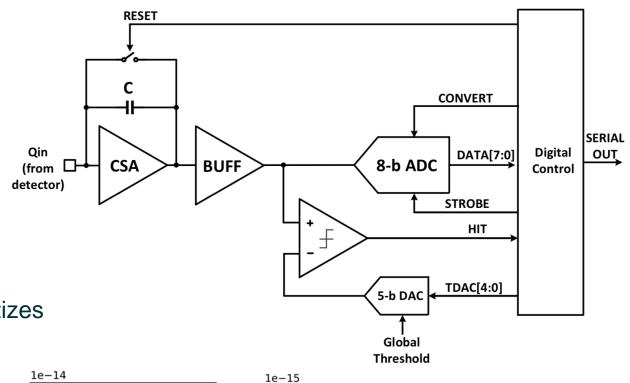

## **LArPix ASIC Concept**

Low-power, integrating amplifier with self-triggered digitization and readout

Pixel dormant until signal exceeds tunable threshold

- Integrates charge for  $\sim 3\mu s$  ( $\sim 4$  mm drift), then digitizes

- Ready for next signal

Pixels are continuously active

- Serial I/O data rate is slow (~5 Mb/s per I/O channel) to limit digital power

- Modest data volumes: ~1 MB/s per square meter of anode in surface cosmic flux

Incorporation of buffering, ADC sampling, and digitization

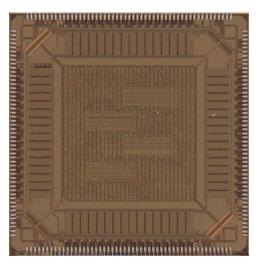

#### **LArPix-v2 ASIC Implementation**

| Version | CMOS Process | Receipt | I/O                 |

|---------|--------------|---------|---------------------|

| 2a      | 180 nm       | 2/2020  | Pseudo-differential |

| 2b      | 180 nm       | 8/2021  | True differential   |

| 2c      | 130 nm       | 11/2022 | True differential   |

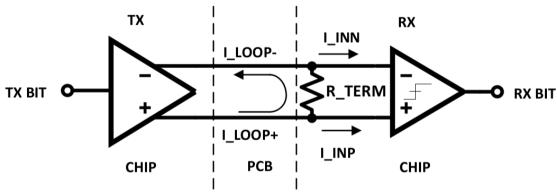

LArPix-v2b, -v2c ASIC: low-voltage, low-power digital I/O

- O(10  $\mu$ W) per transmitter & receiver

- Highly-tunable loop current and termination resistance supports multiple modes of operation (chip-to-chip, multidrop, etc.)

- Optional mode for automatic transmitter power-down when no data

LArPix-v2b ASIC

| Specification           | Value                             |  |

|-------------------------|-----------------------------------|--|

| Analog inputs           | 64                                |  |

| Dynamic range           | 1.5 V                             |  |

| ADC resolution          | 8 bits                            |  |

| ADC LSB                 | 4 mV (chip configurable)          |  |

| Threshold range         | 0 to 1.8 V (channel configurable) |  |

| Timestamp precision     | 100 ns (1 clock cycle)            |  |

| FIFO event memory depth | 2048                              |  |

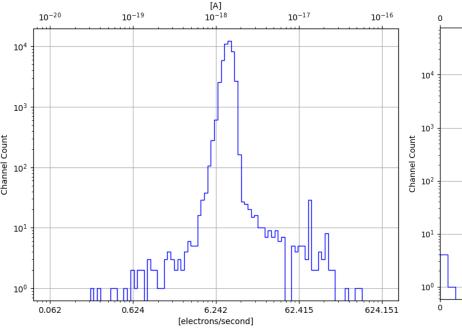

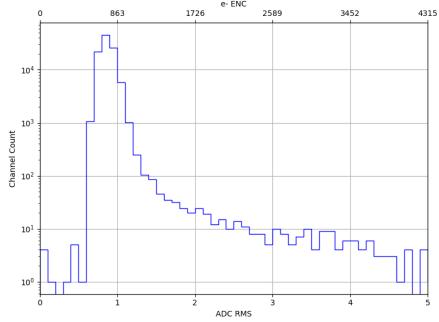

#### **LArPix-v2b Performance**

- Low-voltage I/O working as designed

- Prototype v2b-based pixel tiles deployed in LArTPC operation

| Specification   | Value                    |

|-----------------|--------------------------|

| Gain            | 4.5 μV/e-                |

| Noise           | ~800 e- ENC              |

| Leakage current | << 100 aA                |

| Power           | $O(100~\mu W)$ / channel |

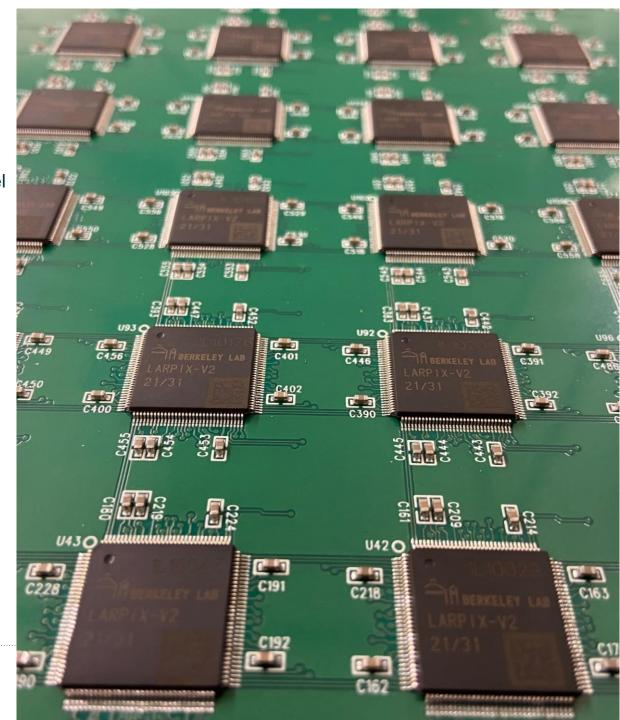

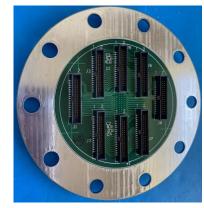

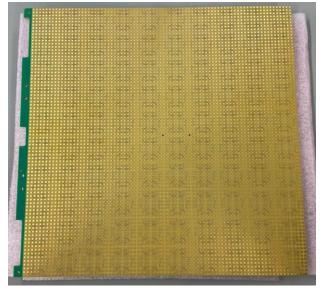

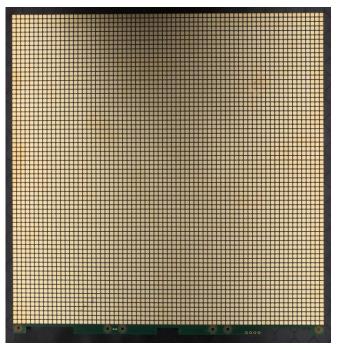

32 cm by 32 cm LArPixv2b anode PCB tile

3.8 mm pixel pitch 100 ASICs/tile 6400 channels/tile

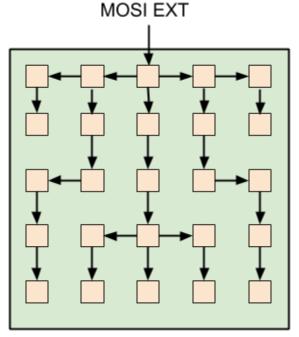

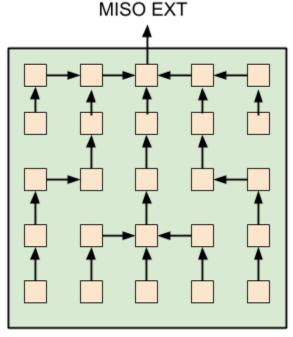

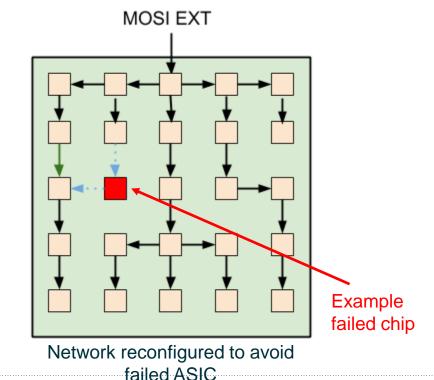

## **Hydra IO**

#### Dynamic I/O routing

AD-HOC NETWORK OF READOUT APPLICATION-SPECIFIC INTEGRATED CIRCUITS FOR RELIABLE DETECTOR INSTRUMENTATION U.S. Patent Application Ser. No: 63/140,434

2022 R&D 100 Award

- I/O can occur between any neighboring chips on pixel tile

- Network constructed by explicitly connecting neighboring ASICs in a determined fashion

#### Realized and exercised with LArPix-v2

Upstream configuration commands

Downstream data flow

Digital multiplexing: O(1k) pixels / I/O channel

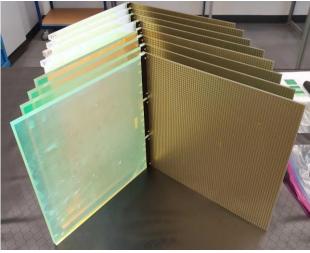

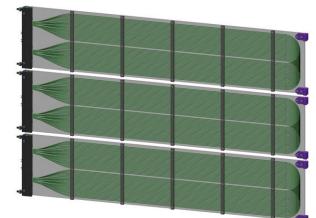

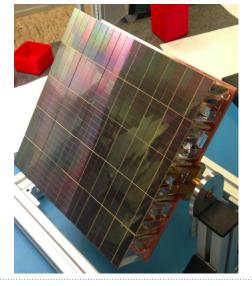

# System Prototyping

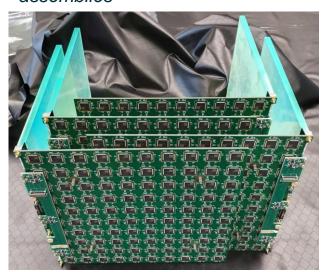

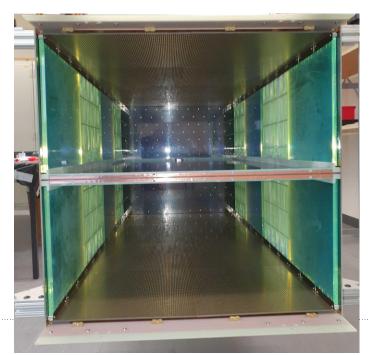

- All production and assembly performed by industry

- Individually tested O(10k) ASICs, O(100) pixel tiles

- Three ton-scale TPCs built and tested

Single pixel tile & light module assemblies

One anode, fully-assembled

10 Two anodes installed inside field cage

# System Prototypes.

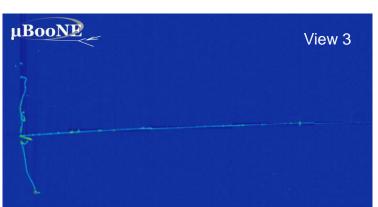

Raw data with 200 keV channel threshold

600 400 200 200 -200

-400

-600

250

Thyp, -250 -250

- Successful deployment and operation of **three** O(100k) channel systems >100M cosmic ray events recorded

- Quick-turn industry fabrication at competitive cost O(\$0.10/channel) at large O(10 M) channel system

250

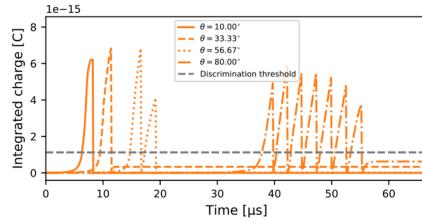

### Pixel response validation

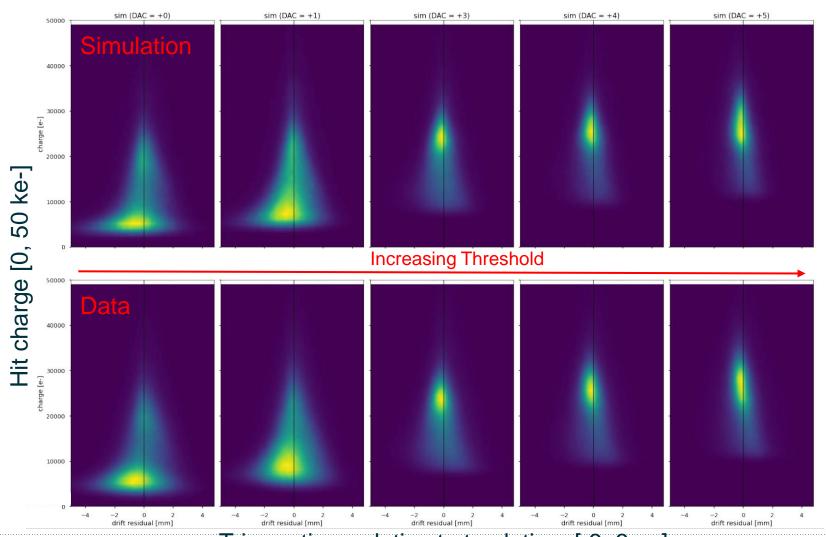

# Pixel trigger response versus threshold (data versus MC)

- Detailed ASIC front-end charge response simulation using GPU-optimized algorithms

- To first order, good datasimulation agreement in channel threshold crossing time and charge measurement

"Highly-parallelized simulation of a pixelated LArTPC on a GPU" publication in preparation

Trigger time relative to track time [-3, 3  $\mu$ s]

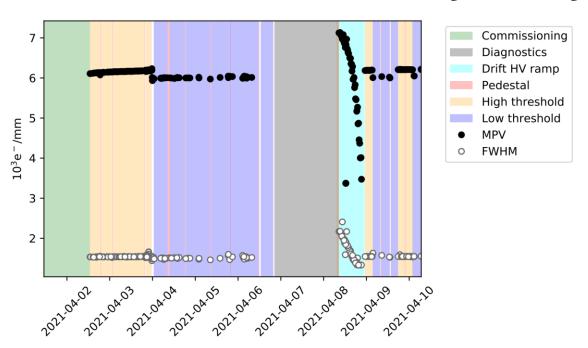

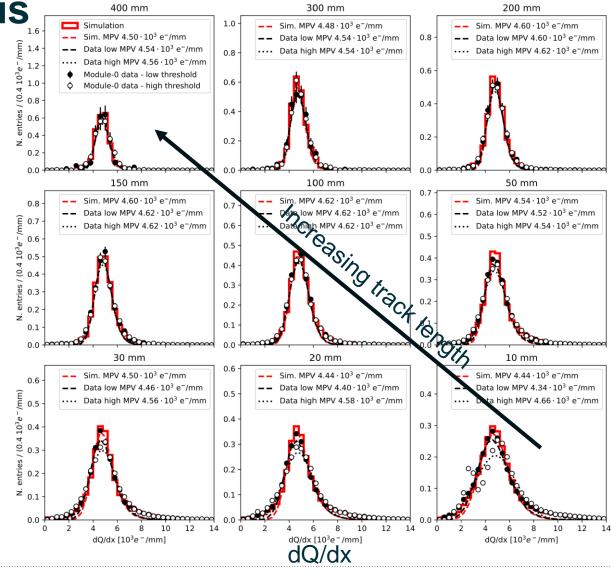

**Track-level Cosmic Ray Analysis**

- Pixels are continuously active (>100M cosmic ray events recorded)

- Serial data packets stream out of system as channels self-trigger

- MIP response is consistent with expectation and stable throughout data taking

"Performance of a modular ton-scale pixel-readout liquid argon Time Projection Chamber" publication in preparation

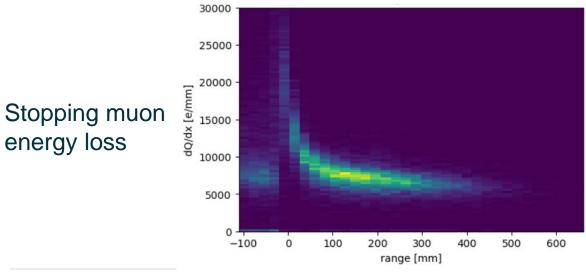

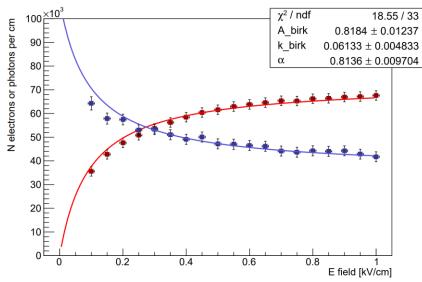

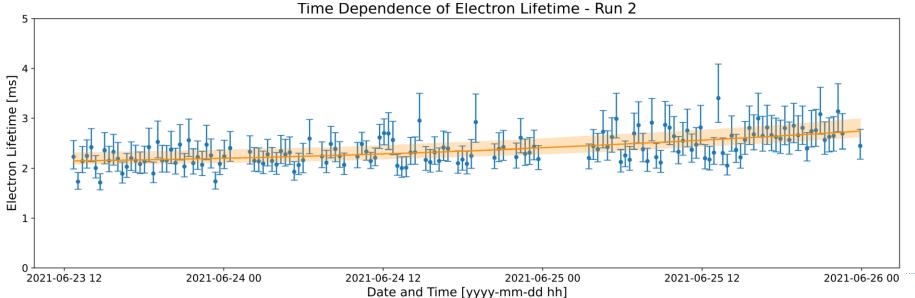

#### **Detector Physics Studies**

"Performance of a modular ton-scale pixel-readout liquid argon Time Projection Chamber" publication in preparation

Charge-light anticorrelation

LAr purity electron lifetime

# LightPix

#### **LightPix Concept**

- Low-power cryogenic-compatible, scalable (>10<sup>6</sup>) SiPM readout electronics at very low system cost

- Adapting existing LArPix system architecture

- Shared cabling, feedthrough, warm electronics

- LightPix ASIC re-uses majority of LArPix design, but replaces ADC with TDC

- Provide a path for highly-granular photodetection systems for very large detectors

Example of light trap SiPM detector format *LCM*

Replace pixel pads with SiPMs

Example of direct SiPM detector format DarkSide-20k

## **LightPix ASIC Implementation**

(from 🗆 🕂

detector)

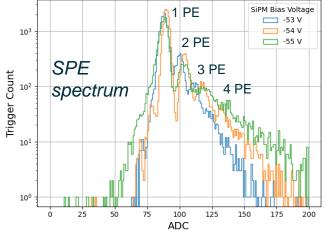

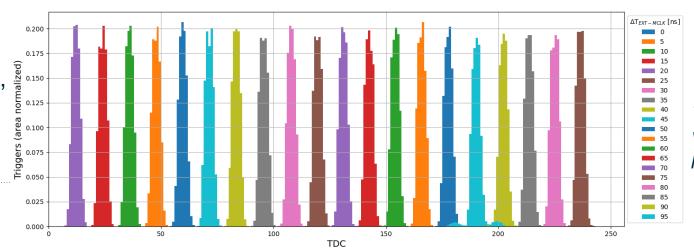

LightPix-v1b TDC evaluation for SPE from commercial 3 mm x 3mm SiPMs

Linear to <1 ns over the full 100 ns timing range

< 1 ns jitter</p>

< 2 ns time-walk bias</li>

< 1 ns RMS global timing accuracy</li>

# CONVERT TDC EN RAMP GEN 8-b ADC Digital Control Control STROBE TDAC[4:0] Global Threshold

#### LightPix-v2

Dual TDC/ADC functionality in single ASIC – design complete, awaiting production

TDC output versus test pulse time offset

# **Summary**

#### **LArPix**

- Status

- Successfully produced, qualified, deployed multiple O(100k) channel systems

- ~1/2 million pixel detector operation in NuMI GeV neutrino beam (2023)

- Near-term R&D focus

- ASIC

- Correlated double sampling to improve noise

- Implement 10-bit ADC to improve charge resolution

- Anode tile

- Robustness to microphonics

- Mitigate far-field induced charge with pixel pad geometry

#### **LightPix**

- Status

- TDC meets design targets

- Multi-SiPM performance demonstration in-progress

- Near-term R&D focus

- TDC + ADC functionality in next ASIC version

- Deployment and testing of light detector system in prototype LArTPC

- · Exploration/optimization of light detector formats