# Stave-Oriented Photon Detector Readout with Event Waveform Recording

G.W. Deptuch, A. Bolotnikov, G.A. Carini, A. Dallapenna, D. Górni, N. St John, S. Mandal, C. Miraval, E. Raguzin, V. Radeka, S. Rescia

11/29/2022

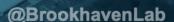

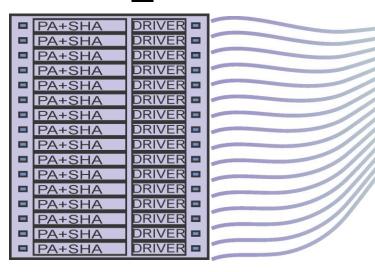

# **DUNE 3-ASIC IAr TPC Streaming Readout**

Waveforms are digitized at 2 MHz and read out without zero suppression

Electronics circuits are mounted near the sense wires,

- Amplifier and Shaper 16 channels

- ADC 16 channels

- Data Merger and Serializer 2 × 1.25 Gbps

- 3-ASIC readout for DUNE far detector:

- Front-End: LArASIC (180 nm) by BNL,

- Time interleaved ADC: ColdADC (65 nm) by LBNL, FNAL, BNL)

- Data concentrator/transceiver: ColdDATA

by FNAL, BNL digital implementation and P&R

- One 10 kTon FD-1HD detector has:

- 3000 x 128-channel Front End Mother Boards with 24000 x FE ASICs, 24000 x ADC ASICs, 6000 COLDATA ASICs

Total 12000 1.28 Gbps links (9.2 Tbps of waveform data)

To DAQ To SSP

To Slow Control

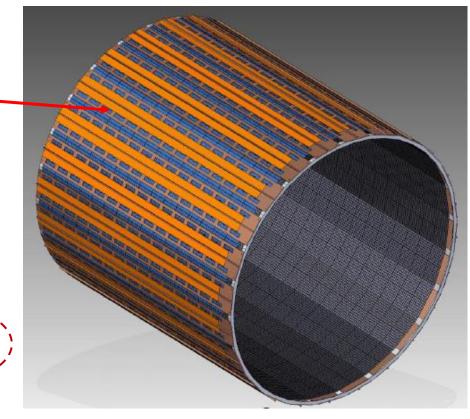

# Staves, Tiles, Mini-tiles, SiPMs

Staves: 24

Tiles : **24** x 2 x 10 = **480**

Minitiles/subarrays 6 cm^2:

**480** x 16 = **7680**

SiPM Area: 7680 x 6 cm $^2$  $\pm$ 4.6 m $^2$ )

| Technolo           | ogy    | "HPK" | "FBK"     |         |

|--------------------|--------|-------|-----------|---------|

| <b>C/A</b> [nF,    | /cm^2] | 3.5   | 8.5       |         |

| $V_{op}$           | [V]    | 60    | 30        |         |

| C <sub>6cm^2</sub> | [nF]   | 21    | 51        |         |

| $C_{2s}$           | [nF]   | 5     | 12.5 in s | eries   |

| $V_{2s}$           | [V]    | 120   | 60 Scon   | nection |

## Readout challenge:

Fine segmentation of 7860 SiPM subarrays=electronic channels (<1 p.e./subarray), still results in a "giant" subarray capacitance/channel, ~5-12 nF in the best case (series connections  $C_{2s}$ ), and ~20-50 nF in the worst case (SiPMs in parallel).

SNR>10 for 1 p.e. essential for nEXO!

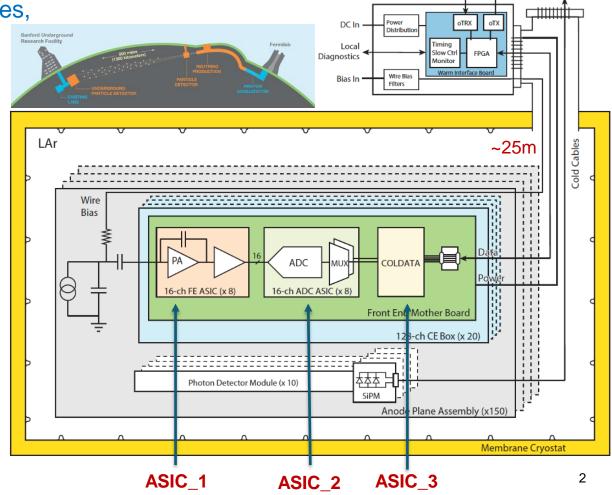

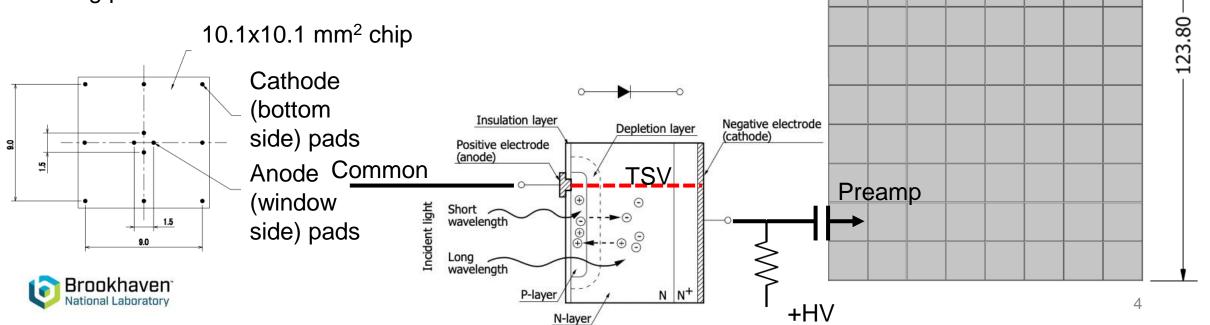

# Fused silica interposer optimized for HPK SiPM geometry Tile (top view)

- Total 96 SiPMs (8×12)

- SiPMs arranged in 4x4 arrays, each consisting of 2x3 subarray (2s3p)

- 0.2 mm gaps between SiPMs

- 16 readout channels

- UV SiPM is "p-on-n" type device with anode at window side

Bonding pads on a new Hamamatsu S16483 ATS device

82.40

Mini-tile (or subarray)

## Readout architecture and extraction of signal from the large capacitance SiPMs

Integration of SiPMs and PRE: Weak Coupling of SiPM and electronic readout: C<sub>b</sub> << C<sub>d</sub>

Radiopure 500 pF/100 V capacitor easier to realize, and lower risk than 50 nF/100V; **SiPM Interposer Electronics Daughterboard** - one of 16 subarrays/tile shown **Digital ASIC** LAr ASIC (one of 16 channels) 2x3 subarray x16 x16 Low pass ADC+PLL+DIG semigaussian  $R_1$ Common  $HV_{in}$ 3 bonds per subarray 0.500 (bump or wire)  $HV_{in}$ x 16=48 per tile One of 16 sets of Common for all 24 R1,R2,Cb is shown tiles in a stave

**Calibration and** diagnostics of electronics independent of SiPM capacitance, bias and condition (open or short).

PRE TDR: Fig. 10.4.2. Tile readout with all active electronics on 5 daughter board

Small  $C_h$  allows higher inductance interconnections.

In situ SiPM array capacitance measurement

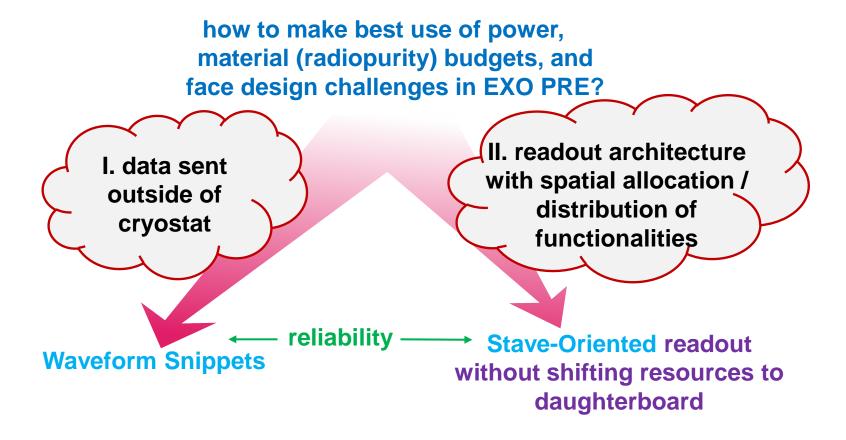

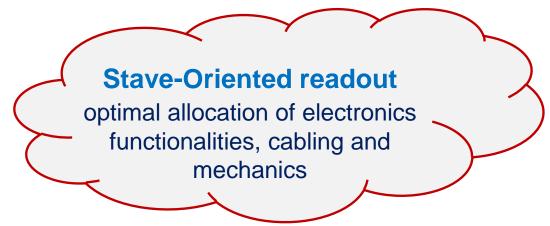

# Introduction of WSSO

Waveform Snippet and Stave-Oriented = WSSO scheme

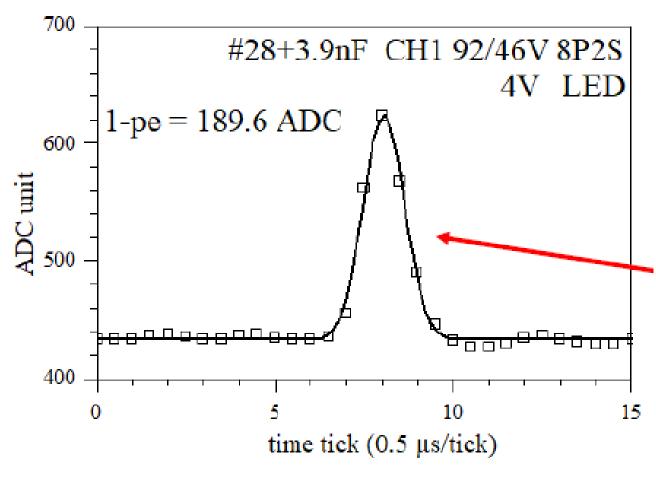

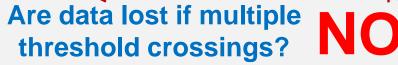

# **WSSO** - illustration

Waveform acquired with the SiPM + FE(LArASIC) to show system proof-of-concept.

Information about single p.e. is fully captured by a 'snippet' of samples (30 samples shown):

- avalanche = 0.4 pC at OV = 4 V

- 1-p.e. S/N ~60;

- 1-p.e. coincidence resolution <u>between two</u> <u>subarrays</u> < 20 ns</li>

# Recipe of WSSO

elimination of sending continuous stream

## **Waveform Snippets**

parts of digitized time sequences containing pre-signal+signal+post-signal samples

- the filtered FE signal is continuously sampled and digitized, exactly as for data-streaming  $(\tau_p=1~\mu s$  and 2 MSps).

- the data are examined for events (signals larger than  $\frac{1}{2}$  p.e.), and then a **snippet of samples** (waveform snippet WS) is retained.

- WSs contain a small number of samples of each signal and the baseline before and after the event (20 32 samples, equivalent to 10 -16  $\mu$ s, may be sufficient).

- each WS is identified through time stamp and channel number for identification.

# **WSSO** - protocol

Example of WS extraction

(assuming WS length = 32 samples and single samples crossing threshold)

more than one threshold crossing in one length of WS may mean multiple events.

circular buffer memory of 64 samples

**\**

## Details:

definition to time stamp, length of WS, etc.

can be decided and programmed in an-on-ASIC WS registration protocol

# WSSO v.s. streaming data rates

assumption of max DCR and calibration rate =  $4 \times 10^3$  events/s (per channel)

## Per Tile:

WS: snippet size [32 samples]  $\times$  event rate [4  $\times$  10<sup>3</sup> events/s]  $\times$  ADC resolution [12 b]  $\times$  # channels/minitiles [16]  $\approx$  24.6 Mbps/tile V.S.

Streaming: [ADC conv. rate] 2 MSps × ADC resolution [12 b] × # channels/minitiles [16] = 384 Mbps/tile

## Per Stave:

WS: tile data rate [24.6 Mbps] x # tiles [20 tiles/stave] ≈ 491.6 Mbps/stave v.s.

**Streaming:** tile data rate [384 Mbps] x # tiles [20 tiles/stave] ≈ **7.68 Gbps/stave**

## **Total:**

WS: stave data rate [491.6 Mbps] x # tiles [24 stave] ≈ 11.8 Gbps v.s.

**Streaming:** stave data rate [7.68 Gbps] × # tiles [24 staves] ≈ 184.3 Gbps

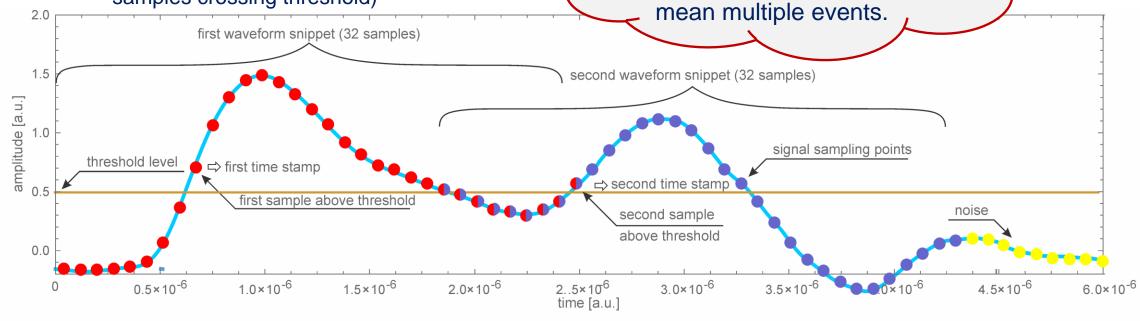

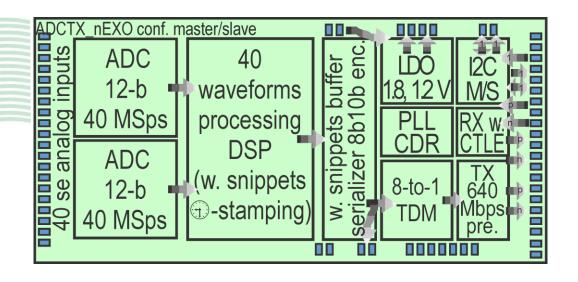

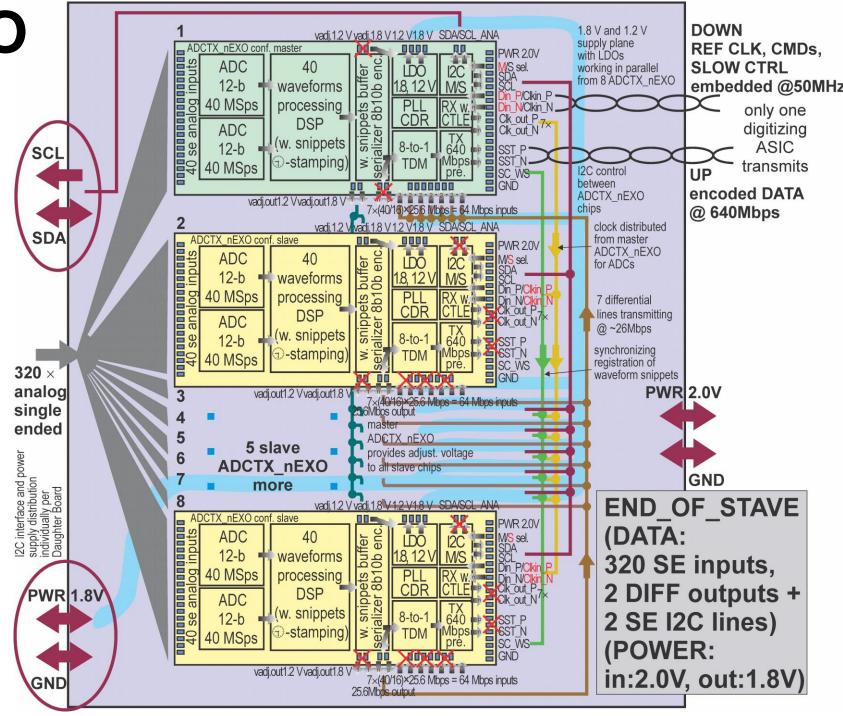

# **Concept of WSSO**

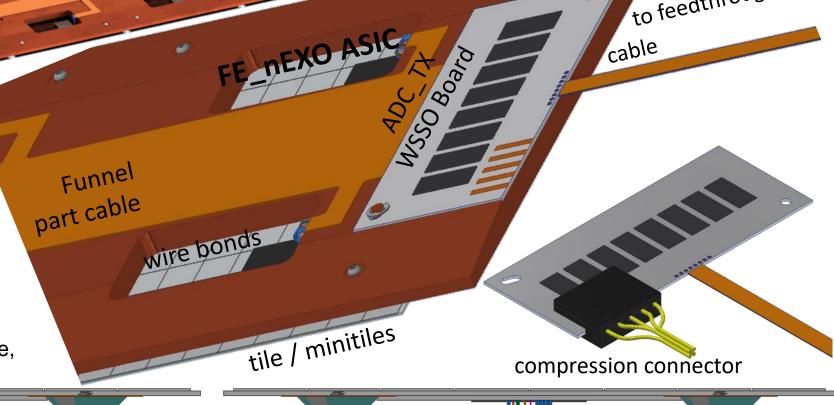

power regulation on tops of staves: two power for ADCTX\_nEXO ASIC one power distributed down to FE\_nEXO ASIC,

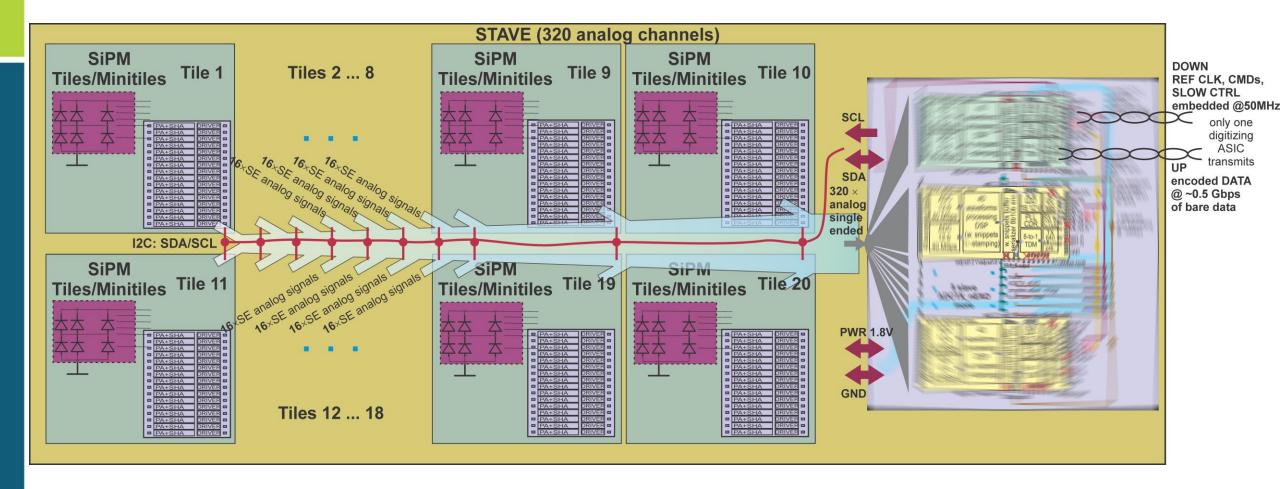

# Is SO entirely new and unproven?

Could all analog lines be driven outside to external ADCs in nEXO?

it is not a good idea, as among other troubles, it would require 7680 analog lines be driven through feedthrough

# **ASICs in WSSO**

**ASICs: FE nEXO**

ADCTX\_nEXO

**Location:** Daughter Board

**Location:** Top of Stave instead of Daughter Board

Single-ended (SE) analog waveforms

# Recipe of WSSO

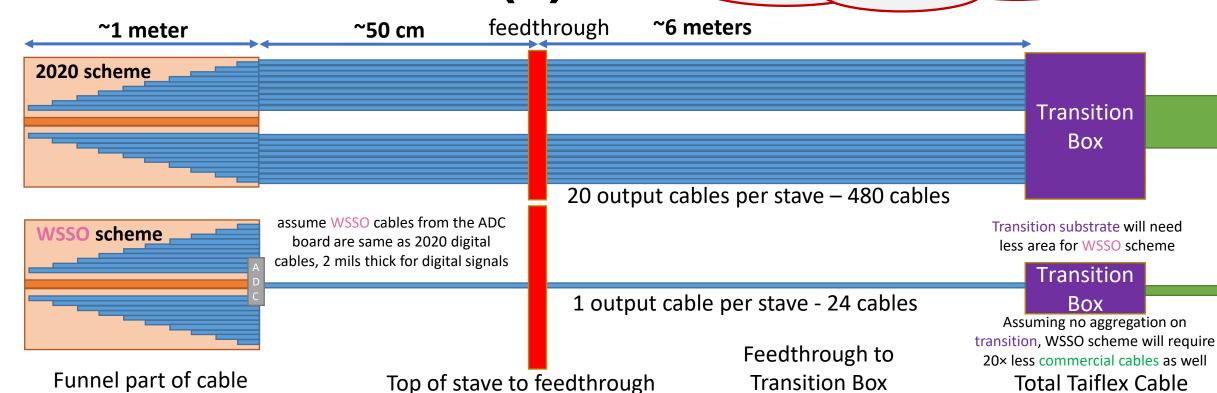

provide interface to stave with reduction of **20** data cables from stave to transition box to **1** cable

- optimal placement of ASICs in 2-ASIC readout solution,

- more than 10 × reduction of data cables = easier and more reliable mechanics of feedthroughs,

- improving radiopurity through reduction of polyimide volume,

- no distribution of digital signals across staves, and easy handling of slow-control,

- less components (decoupling capacitors on daughter boards) and lighter power distribution,

- achieving modularity, reconfigurability and suitability for testing as stave is one self-contained subsystem block,

- makes stave possible for testing in laboratory and includes test modes :

- taking empty (not containing thresholded data) waveform snippets (tacking baseline/low freq. noise),

- allowing streaming one selected channel without applying any threshold.

# Questions for SO (1)

**15% less**

material budget and radiopurity comparing 2020 with WSSO

Funnel part of cable

| Scheme | Volume<br>(cm³) | Mass (g) |

|--------|-----------------|----------|

| 2020   | 106.02          | 150.54   |

| WSSO   | 89.86           | 127.59   |

| Brookha<br>National Labo |  |

|--------------------------|--|

Top of stave to feedthrough

| Volume<br>(cm³) | Mass (g) |

|-----------------|----------|

| 64.25           | 91.24    |

| 3.21            | 4.56     |

**Transition Box**

| Volume<br>(cm³) | Mass (g) |

|-----------------|----------|

| 771.02          | 1094.85  |

| 38.55           | 54.74    |

Volume Mass (cm<sup>3</sup>) (g) 1245.39 877.04 128.41 182.33

**95%** less **95% less**

**85%** less

# Questions about SO (2)

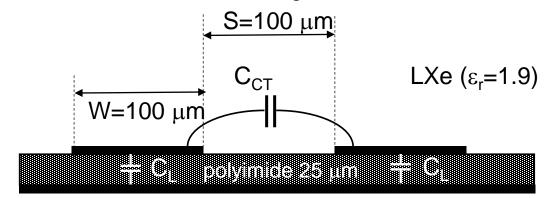

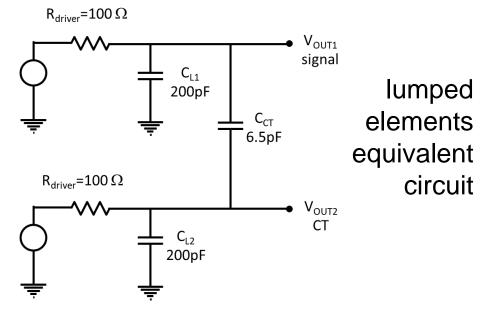

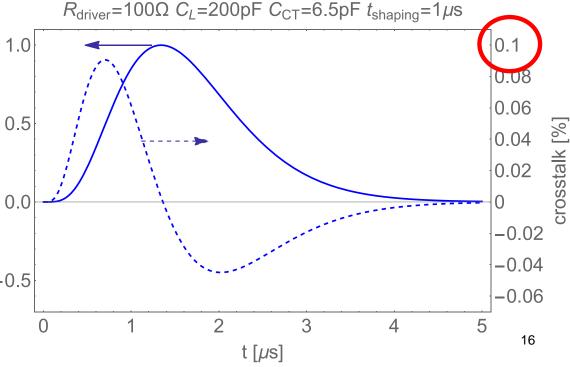

cross-talks between single-ended analog lines

signal lines: 100 µm (4 mil) width / 100 µm (4 mil) spacing conductor: 0.5 oz Copper, thickness = 17 µm (0.67 mil) dielectric: Kapton, thickness = 25 µm (1 mil) ground plane: 0.5 oz Copper under signal traces bandwidth of transmitted signals is limited < 300 kHz

capacitive coupling (dependent on the driver's output- and receiver's input resistance) can be maintained **below 1%** -0.5

$V_{\rm out,sh}[t]$

Signal & Crosstalk W=S=100µm

# Main questions for SO (3) | location and feasibility | ADC\_TX WSSO board | top of stave to feedthrough cable | cable

## ADC\_TX WSSO Board:

- hosts 8 ADC\_TX\_nEXO ASICs as is the most complex object,

- can be silica or polyamide, 4-layer board (7%)

- max dimensions 3.5"x1",

- contacts for Taiflex cable and temporary connection for testing fixture,

ADC\_TX\_nEXO ASIC Board

- 320 analog input channels split into 8 ADC\_TX\_nEXO ASICs,

- each ADC\_TX\_nEXO ASIC is identical,

- only one master is required per stave,

- master ADCTX\_nEXO ASIC recovers clock,

- master synchronizes all ADC\_TX\_nEXO ASICs,

- two loops of slow control,

- voltage regulation for 1.2 V (digital) and

1.8 V (all analog)

# Principal points of WSSO

- The Waveform Snippet and Stave-Oriented (WSSO) scheme will provide all the signal generated by SiPMs with a record for all events, at a significantly lower data rate, caontrasting to the original concept, where:

- the baseline samples contain information about nothing but noise,

- 480 data cables transfer 24 cables-worth signals.

- WSSO provides a reduction in the number of low dispersion cables and their connections by an order of magnitude or more, a reduction in the amount of potentially background contributing material, a simplification of the feedthrough design and lower cost, etc.

- WSSO improves reliability, making feedthroughs less prone to disconnect or get damaged.

- WSSO scheme makes the staves into self-contained objects simplifying testing of the staves and assembly into the cryostat.

# Reserve Slides

# Comparison of readout schemes

| Readout Scheme                         | 1) Continuous sampling with waveform recording "data streaming"         | 2) Continuous sampling with "WS data recording"                                          | Comments on 1)                    | Comments on 2)                     |

|----------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------|

| Data rate / tile<br>@ 2MSps 12-bit ADC | 384 Mbps                                                                | 24.6 Mbps<br>(32 samples per WS)                                                         | -                                 | -                                  |

| Number of low dispersion data links    | 480 cables                                                              | 24 or 48 cables                                                                          | Critical connections on each tile | Critical connections on each stave |

| Daughter board design                  | entire analog and ADC<br>+ digital + data transfer<br>circuits and LDOs | FE ASIC on the board; ADC + digital + data transfer and LDOs are integral for each stave | Location:<br>daughter<br>board    | Location: top of stave             |

| Power dissipation location             | 100% on daughter boards                                                 | 1/3 on daughter boards;<br>2/3 on top of stave                                           | 2 powers on DB                    | 1 power on<br>DB                   |

| Location of ASICs                      | on daughter boards                                                      | FE ASIC on daughter board;<br>ADC-digital ASIC on top of stave                           |                                   |                                    |

| Location of V <sub>DD</sub> capacitors | 100% on daughter boards                                                 | 1/3 on daughter boards;<br>2/3 on top of stave                                           |                                   | 21                                 |

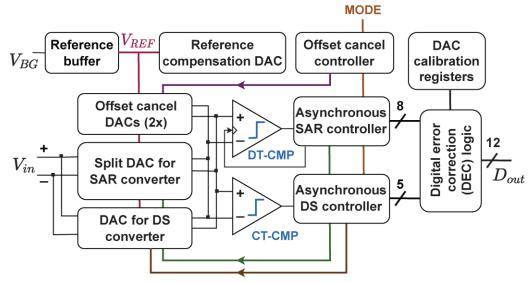

## nEXO ADC

## SysADC\_P1

## Low-power, 12-bit, hybrid ADC design in 65 nm CMOS:

Overall: 8-bit SAR (MSB) + 5-bit digital slope (LSB),

SAR/digital slope boundary uses 1 redundant bit for robustness, thus resulting in 12-bit resolution.

## Asynchronous successive approximation (SAR) converter:

Fully-differential charge redistribution architecture, Split capacitor DAC using low-power merge-and-split switching, Uses one redundant conversion cycle for robustness.

## Asynchronous digital slope (DS) converter:

Asynchronous low-power delay line-based architecture, DS capacitors are laid out within the SAR DAC to minimize gain mismatch and simplify calibration.

### Additional features:

On-chip reference buffer w/ cancellation of switching transients, On-chip digital calibration of comparator offset; supports off-chip calibration of DAC capacitor mismatch.

Preliminary performance specifications

| Parameter                     | Value               |

|-------------------------------|---------------------|

| Sampling rate                 | Up to 50 MS/s       |

| Output resolution             | 12-bit              |

| Full-scale voltage            | 1.7 V <sub>pp</sub> |

| Effective no. of bits (ENOB)  | 11.0                |

| Core power (at 50 MS/sec)     | 820 µW              |

| Reference buffer power        | 1.15 mW             |

| Walden FOM (including buffer) | 19.5 fJ/bit         |

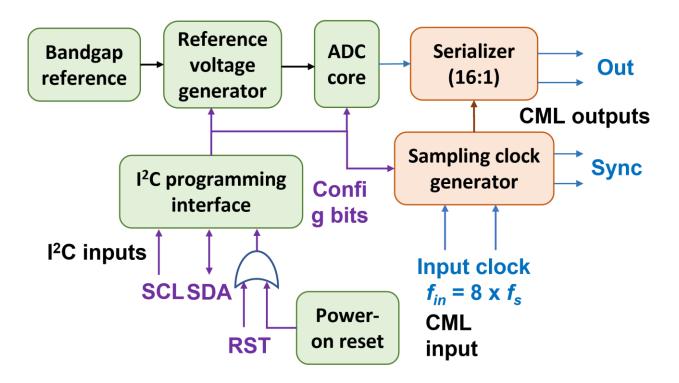

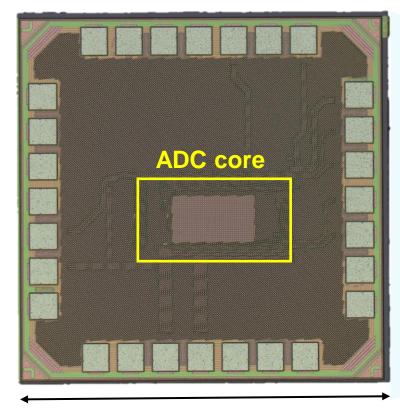

## **nEXO ADC**

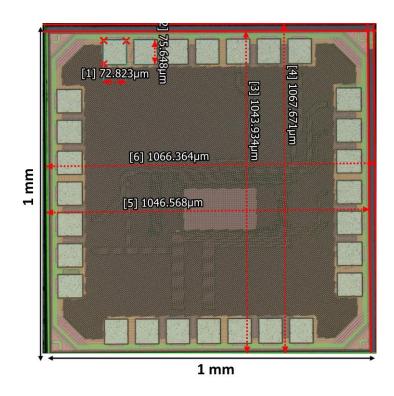

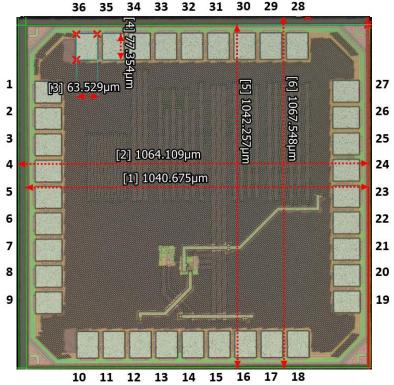

- The 1 mm<sup>2</sup> test chip integrates the ADC with accessory circuits (band-gap voltage reference, clock receiver, sampling clock generator, output serializer, serial programming interface, and power-on reset),

- Layout area of the ADC core (not including reference buffer) = 320  $\mu$ m x 160  $\mu$ m,

- Chip was submitted for fabrication in the TSMC 65nm CMOS LP 1P9M process in June (testing is underway).

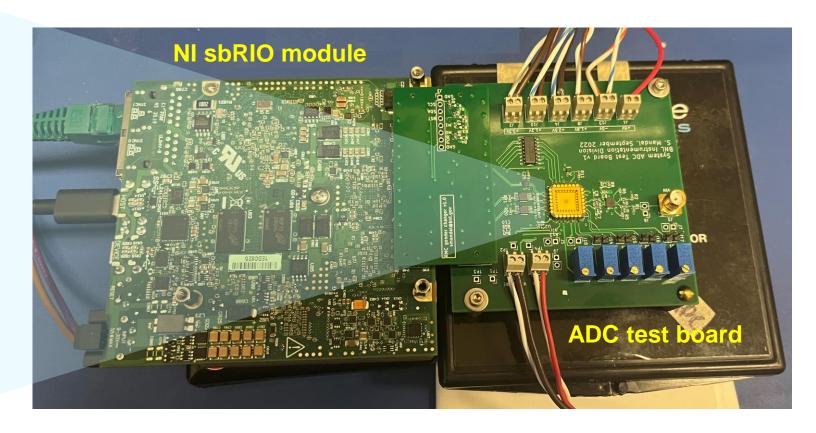

# **ADC** test setup

1 mm

- The ADC test board includes a low-noise, low-distortion, high-slew-rate ADC driver (ADA4927) that also performs single-ended to differential conversion.

- The board also contains digital level translators (1.2V / 2.5V) for the ADC outputs and I<sup>2</sup>C signals.

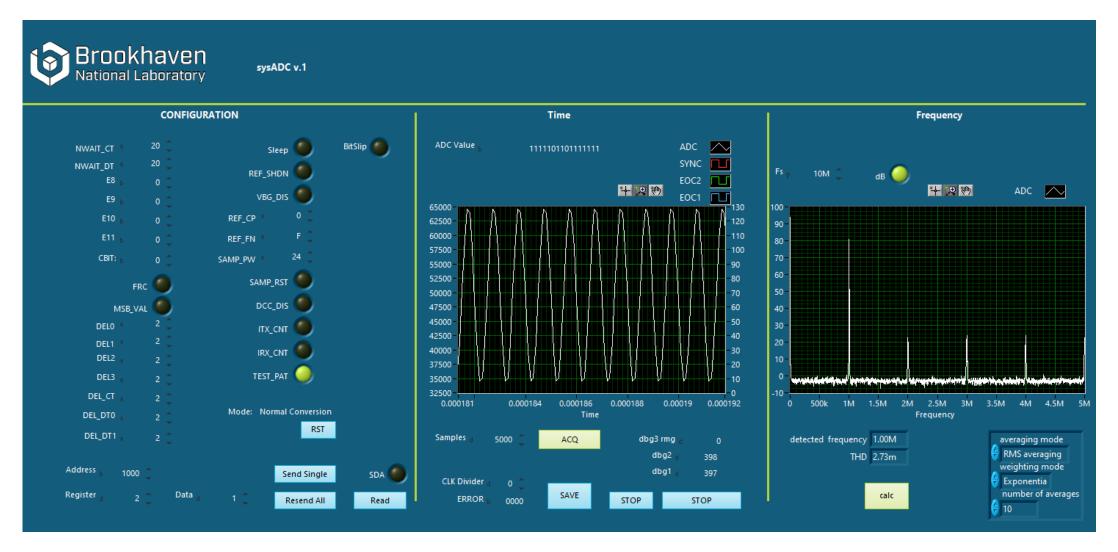

# Test GUI (developed in LabVIEW)

## **nEXO** Line Driver

**VCTRL**

R-DAC

VcmSEL<1:0>

## PELnDrv P1

Phase

Detector

Standalone DLL

Pump

Vn CP HL<2:0>

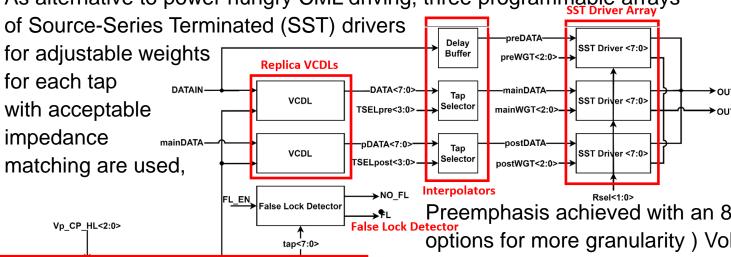

- Low-power line drivers tailored to the application to effectively drive the desired cable in a power-efficient manner,

- Non-conventional method of generating pre-emphasis (patent pending) developed for lossy transmission cables such as the one radiopure cable used for the nEXO experiment,

As alternative to power hungry CML driving, three programmable arrays

VCDL

Iminval<1:0>

Preemphasis achieved with an 8-stage (digital Interpolators allow 16 delay options for more granularity) Voltage-Controlled Delay-Locked Loop (DLL), featuring a single-test False Lock Detector, where replicas create delayed versions of the input data to form pre-emphasised stream,

The 1 mm<sup>2</sup> test chip contains/integrates the full line driver without serializer but with testability (PRBS transmission data generator),

Chip was submitted for fabrication in the TSMC 65nm CMOS LP process in June (expected in August), efforts started to handle testing.

## **nEXO** Line Driver

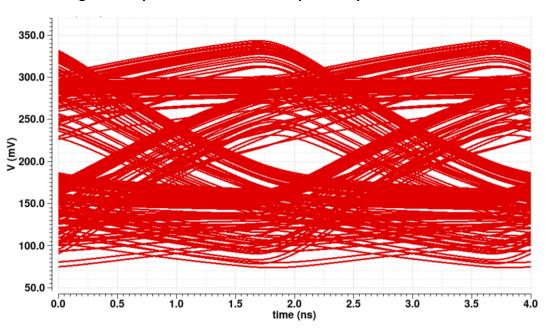

## **Regular Line Driver (no Pre-Emphasis):**

Settings: Pre-Tap Duration: 100% of UI | Post-Tap Duration: 100% of IO

Eye Opening: 37.6mV and 0.879ns

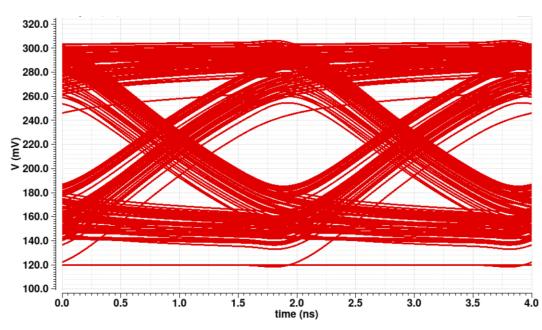

## **Optimal Line Driver Pre-Emphasis Settings:**

Pre-Tap Duration: 10% of UI | Post-Tap Duration: 90% of IO

Eye Opening: 74.4mV and 1.183ns

Input: 7b PRBS signal running at bit period of 2ns (500MHz)

Tap Weights: 600mV each

Cable length: 6m