# MIDNA: Sub-electron skipper-CCD readout with multichannel cryogenic low-noise readout ASICs

Troy England<sup>1</sup>, Fabricio Alcalde Bessia<sup>2</sup>, Hongzhi Sun<sup>1</sup>, Leandro Stefanazzi<sup>1</sup>, Davide Braga<sup>1</sup>, Miguel Sofo Haro<sup>2</sup>, Claudio Chavez<sup>1</sup>, Shaorui Li<sup>1</sup>, Juan Estrada<sup>1</sup>, Farah Fahim<sup>1</sup>

<sup>1</sup>Fermi National Accelerator Laboratory

<sup>2</sup>Instituto Balseiro and Instituto de Nanociencia y Nanotecnologia INN (CNEA-CONICET)

#### **Outline**

- Skipper CCDs used for Dark Matter

- Midna ASIC for Skipper CCD Readout

- Midna 2 Architecture and Results

- Conclusions and Future Development

### **CCDs for Low Noise Imaging**

- CCDs have long been the main choice for low noise scientific imaging

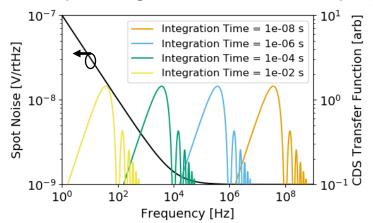

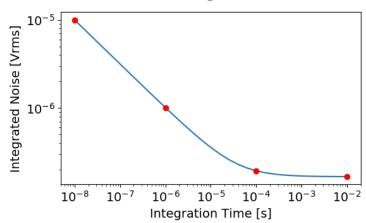

- The low noise has been enabled by a combination of integrating the readout for long periods and using correlated double sampling (CDS) [1]

- Unfortunately, 1/f noise means that there was a limit to the effectiveness of this approach

- Long integration moved the content of interest to lower and lower frequencies

- The spreading out of the CDS sampling points reduced the filtering of flicker noise

### Skipper CCDs for Exceptional Low Noise for Dark Matter Search

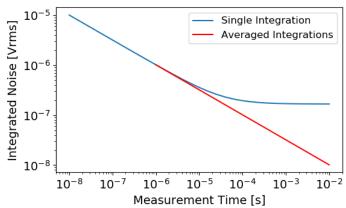

- Skipper CCDs and similar technologies enabled the non-destructive readout of the same pixel many times [2]

- The noise can be lowered by averaging many shorter reads rather than one long read

- It continues the decreasing noise trend with longer measurement times

- There are still limits to this approach

- Leakage in the charge transport in the CCD (low)

- Speed of the various readout stages and clocking

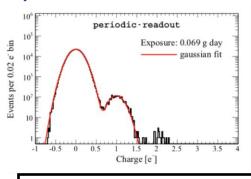

- A skipper CCD has demonstrated the lowest ever, 0.068 e<sub>rms</sub>, noise floor in CCDs [3]

- Required 4000 read averages at 10 μs/read

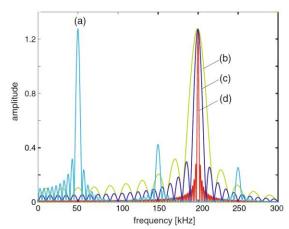

Fig. 8 Frequency response of the Skipper readout system for  $T_S = 10~\mu \text{s}$  and N = 10 (a) and for  $T_S = 2.5~\mu \text{s}$  and N = 10 (b), N = 20 (c) and N = 100 (d)

From [3]

### **Skipper-CCD for Dark Matter Search**

FNAL / MINOS

Phys. Rev. Lett. 122, 161801 (2019)

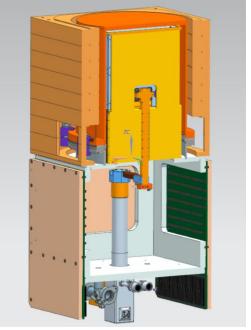

**SNOLAB**

During December 2019 we installed the first skipper-CCD at SNOLAB. (2.5 g active mass)

#### **SENSEI 100**

Design for the 100g experiment is done, and orders for parts have been placed.

#### Next: 28 Gigapixel digital camera for dark matter!

Cooling, readout, packaging and testing of the required <u>24000 skipper-CCD sensors</u> require engineering solutions that are not available yet for scientific CCDs.

Multi skipper-CCD modules for SENSEI-100 currently being tested with great success.

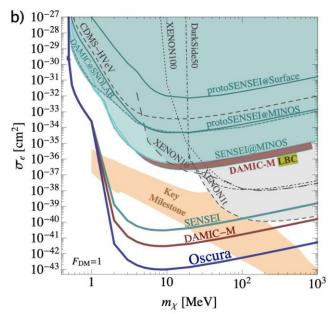

### **OSCURA: 4 year Research and Development Effort**

See talks by <u>Claudio Chavez</u> and Ana Martina Botti in WG7

"DOE Dark matter New Initiatives" FNAL, LBNL, PNNL, U. Chicago, U. Washington, Stony Brook University.

Fermilab is leading the effort to develop the a skipper-CCD dark matter detector with active mass of 10 kg of Silicon.

Fabrication of <u>skipper-CCDs needs to be adapted</u> <u>to the changes in the semiconductor industry. We have identified new industrial</u> partners for this, and will be testing them over the next year.

Taking the skipper-CCDs to their full potential as dark matter detectors.

# 28 Gigapixel digital camera for dark matter!

Cooling, readout, packaging and testing of the required <u>24000 skipper-CCD sensors require</u> <u>engineering solutions that are not available yet for scientific CCDs.</u>

Radiation background required is ~10 lower than state of the art experiments.

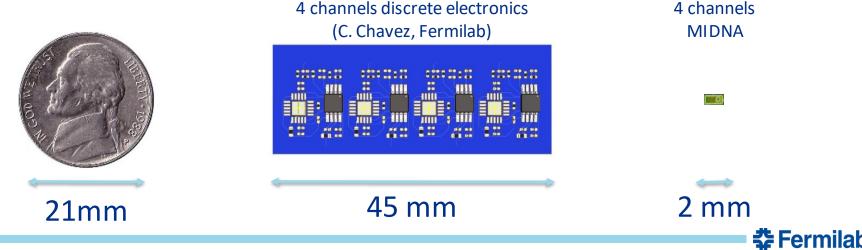

### An ASIC to Support Scaling to 28 Gigapixels, MIDNA

- MIDNA is a prototype cryogenic low-noise skipper-CCD readout ASIC

- It is an enabling technology for the OSCURA dark matter detection project

- Integrates multiple readout channels onto a single chip, replacing numerous costly PCB components and saving valuable physical space

- Operates at 120 Kelvin where COTS devices are not guaranteed to specification

### **MIDNA Specifications and Roadmap of the Chips**

- Less than one third of typical CCD readout noise

- 3000 electron maximum input

- Pile up to achieve sub-electron readout noise with CCD (for signals up to 5e<sup>-</sup>)

- Capable of cryogenic operation between 100 and 130 Kelvin

#### MIDNA v1

- Prototype proof of concept

- Noise is top priority

- Little priority on integration

- Auxiliary test structures

#### MIDNA v2

- Refined performance

- Support circuitry integration

- Keep minor scaling

#### MIDNA Future

- Scale to need, 100s channels practical

- On chip digitization

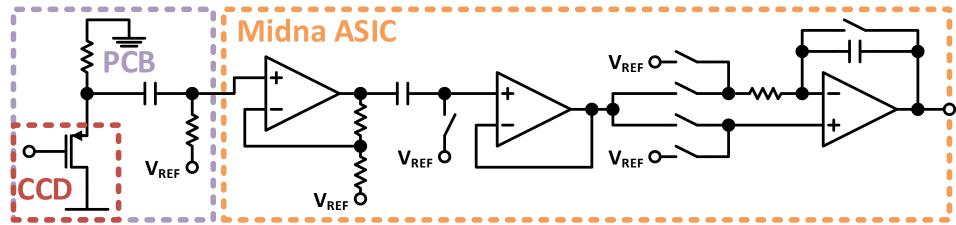

### **MIDNA Channel**

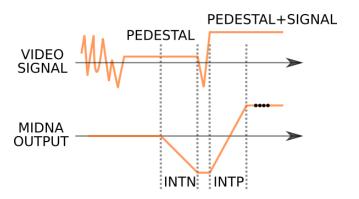

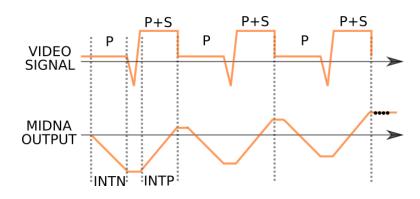

- The foundation of the MIDNA channel is a dual-slope integrator

- The integrator is used to implement CDS and filtering

- Chopping included in the integrator is key to sub-electron performance

- See <u>T.England's CPAD 2021 presentation</u>

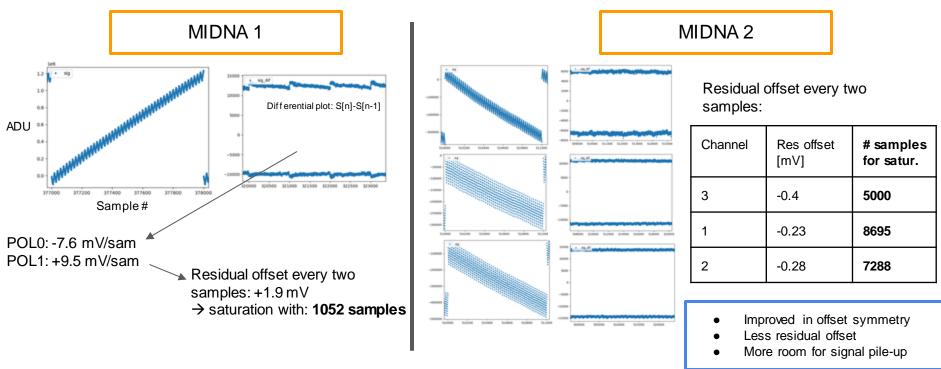

#### **MIDNA 2 incremental improvements**

- Internal BGR reference and independent voltage buffering

- Reduced integrator offset for improved analog pile-up

- Chopping now default

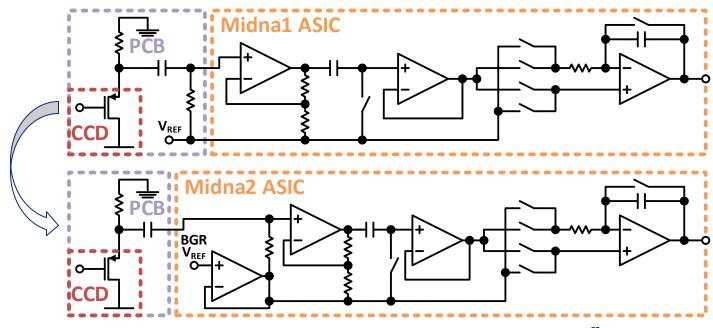

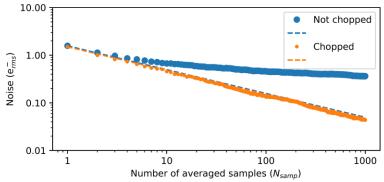

# **Integrator Chopping**

Chopping allows the integration of the feedback amplifier's internal offset and low frequency noise in opposing directions during readout, greatly lowering the magnitude of the transfer function from the effective noise source to the output of the channel

Test results for a standard-sequence measurement of an AC-grounded channel with and without chopping of the integrator.

- Without mitigation of the 1/f noise contributed by the integrator feedback amplifier, the noise magnitude saturates

- With chopping, noise reduction continues as N<sup>-1/2</sup>, indicative of white noise

- → Chopping critical for low noise results

### MIDNA 2 adds Support Circuitry on chip for OSCURA Scaling

#### MIDNA v1

- Size: 2mm x 1mm

- Four parallel readout channels

- Digital controller

- External biasing

- Test structures

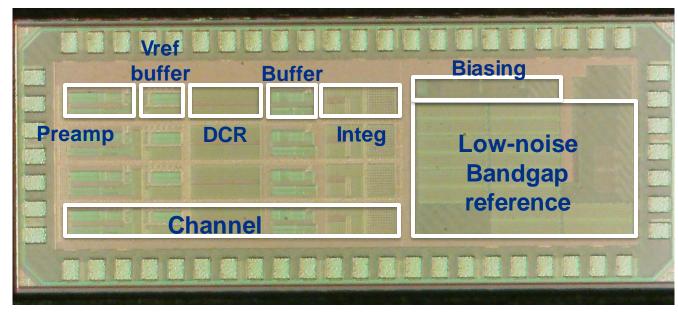

#### MIDNA v2

- Size: 2.5mm x 1mm

- Four parallel readout channels

- On-chip voltage bandgap reference and biasing

- Reduced Integrator offset and chopping by default.

- Reference voltage buffered on each channel.

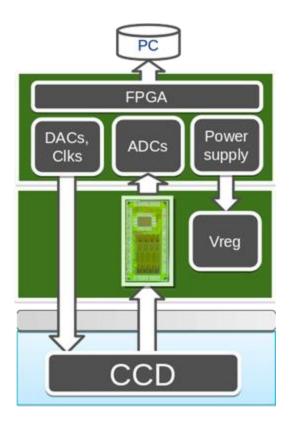

### **Block Diagram**

- Each channel is about 150 µm x 1.3 mm

- Chip is 2.5 mm x 1 mm

- Taped out in March 2022

- Four analog channels

- 4.5mW/channel

- On chip low-noise bandgap reference

- · On chip biasing

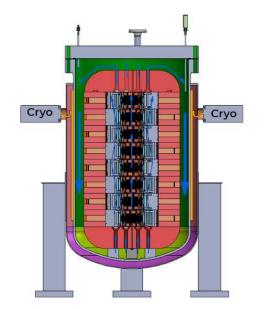

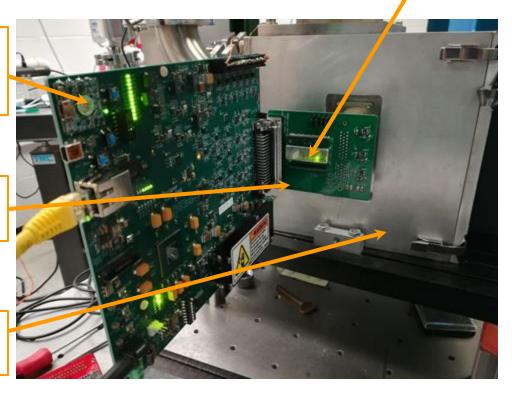

# **MIDNA 1 Measurement Setup**

MIDNA (shielded)

Low-Threshold Acquisition (LTA) board

Outside Dewar board

Cooled down CCD

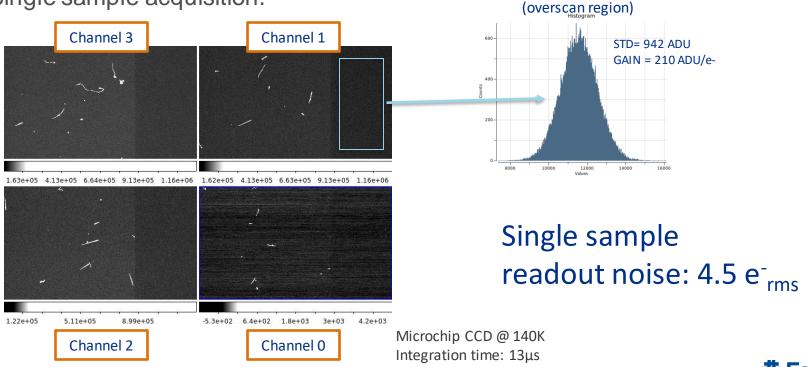

### MIDNA 1 CCD Image Readout

Channel working. We see particle interactions.

Single sample acquisition.

Pixel histogram

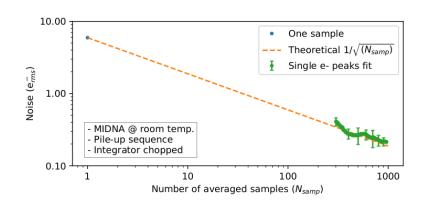

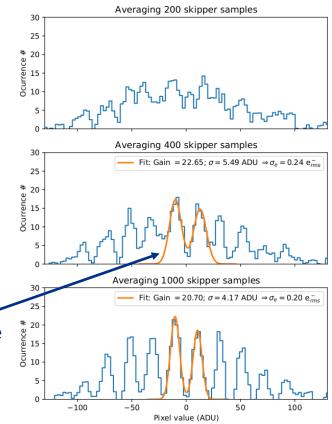

#### MIDNA 1 Achieves Sub-electron CCD Readout Noise

- Even with MIDNA at room temperature, subelectron readout noise was achieved

- Noise is dominated by the CCD

- 0.2 e-rms achieved with 1000 piled up reads

Separation of single electron peaks visible even at 400 reads

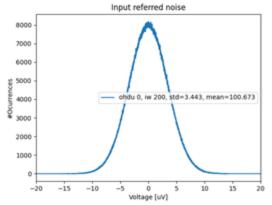

### **MIDNA2** Results: Input Referred Noise

#### ASIC readout noise (no CCD)

- Inputs AC grounded

- Standard sequence. No polarity. IW=13.3µs. SamplePeriod=826µs.

- On average, 3.5 μV<sub>RMS</sub> input referred noise.

- Equivalent to 2 e<sup>-</sup><sub>RMS</sub> (CCD gain of 1.8μV/e-)

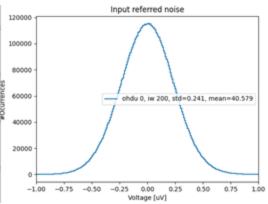

#### Reference voltage noise

- Inputs AC grounded Always RESET

- Standard sequence. Polarity neg/pos. IW=13.3µs. SamplePeriod=826µs.

- Less than 0.3 μV<sub>RMS</sub> input referred noise

- Equivalent to 0.166 e<sup>-</sup><sub>RMS</sub> (CCD gain of 1.8μV/e-)

- → Negligible contribution from additional circuitry

#### **Standard sequence** for reading out one sample:

- one negative integration phase

- one positive integration phase

- one sampling phase (black dots).

#### **Analog pile-up sequence** (e.g. for 3 skipper samples):

- many pairs of integration phases

- · only one final sampling phase.

- No reset between skipper samples

- → Analog averaging reduces the number of ADC conversion and data transfer, at the cost of DR

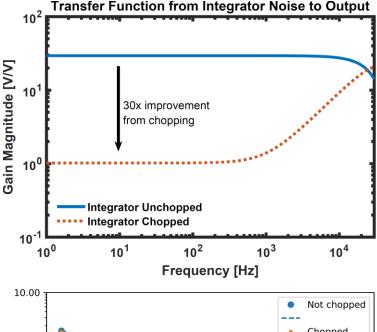

# Offset with polarity switching: MIDNA 1 vs. MIDNA 2

DCR always ON. Polarity switch every 10 CDS. IW=13.3µs. Pile-up N=1000.

5-10x improvement in the residual offset from the integrator with chopping, and this improvement comes from a better symmetry in pos and neg polarities.

#### **Conclusions and Future Work**

- MIDNA 1 successfully demonstrated CCD readout with sub-electron noise

- At a variety of temperatures: room temperature down to ~100K

- With multiple pile up techniques: cancelation sequence, on chip pile up & off chip pile up

- MIDNA 2 brings more support circuitry on chip to scale OSCURA

- Lowers complexity of OSCURA, with fewer external components and connections to room temperature

- Eliminates sources of external interference

- Testing ongoing, positive results so far

- Upgrade CCD for lower system noise

- The future of MIDNA is multi-faceted, beyond OSCURA

- MIDNA itself can be scaled practically to 100s of channels

- Integrate on-chip ADCs, memory, and programmable digital control

- Work has expanded to multiple other projects, see talks by A.Quinn and B.Parpillon and L.Rota