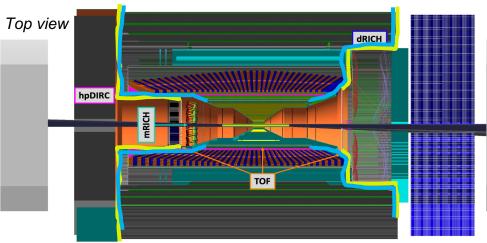

# ePIC Endcap TOF Layout: optimization and update

Wei Li (Rice University)

EPIC TOF-PID WG meeting September 30, 2022

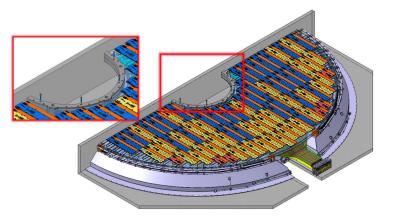

### v0 design of endcap TOF layout

For v0 design, we propose:

- Barrel: 0.5x10 mm<sup>2</sup> strips Zhenyu, 9/10

- Endcap: 0.5x0.5 mm<sup>2</sup> pixels (same as RPs) - Wei, 8/29

- A total of ~13M pixel channels

- Total power: 20 kW (7 for backward and 13 for forward)

Reducing the # of channels, if possible, will help mitigate pressure on the cooling infrastructure and reduce material budget

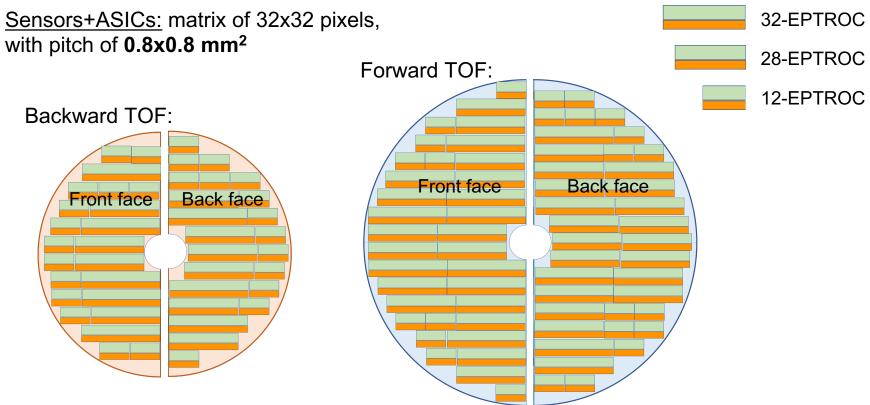

### Sensors, ASICs and Service Hybrids

#### Sensors:

- Each sensor is a matrix of 0.5x0.5 mm<sup>2</sup> pitch pixels

- In general, larger sensors are preferred to maximize active area but also have to consider yields etc. in fabrication

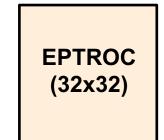

- Each sensor is assumed to be 32x32 pixels or 1.6x1.6 cm<sup>2</sup>

#### ASICs:

• Match the sensor pixelization and size and bump bonded to the sensor

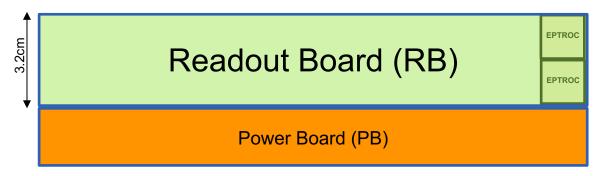

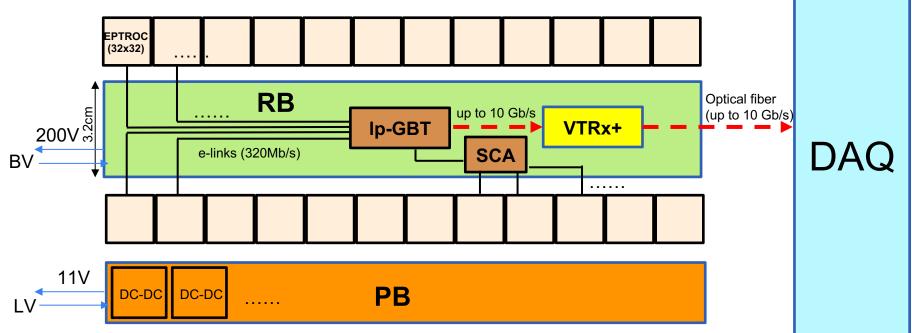

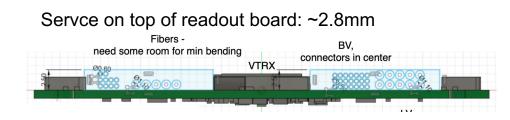

<u>Service Hybrids:</u> situated **on top of sensor+ASICs** provide power and readout services to the modules via flex circuit connectors

### Service Hybrids

(CERN chips or

EIC equivalent ones)

- Ip-GBT: low power gigabit transceiver

- VTRx+: optical link module for data transmission

- SCA: control and configuration of FE chips, and enable DC-DCs

#### Service Hybrids

#### 7-module SH/RB VTRX LpGBT ETROC1 SCA IA 0.83A 1.5V 0.1A 2.5V 0.11A 10V 12V 11V ETROC2 Module-1 linPOL 9 V **≜**9V LVPS PP2 **PPO** Ä ETROC3 1.2V **2I 2I** 9V [ bPOL12 **ETROC4** Power Board 7-module SH/RB **Readout Board** 10X ETROC25 1A ETROC26 Module-7 Large (7 Module) RB 🔿 I = 5.87 A 1A ETROC27 Medium (6 Module) RB 🔿 I = 5.08 A **9**V 1A ETROC28 1.2V bPOL12 (3 Module) RB 🔿 I = 2.73 A Short

#### **Powering of Readout board**

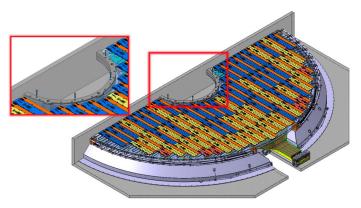

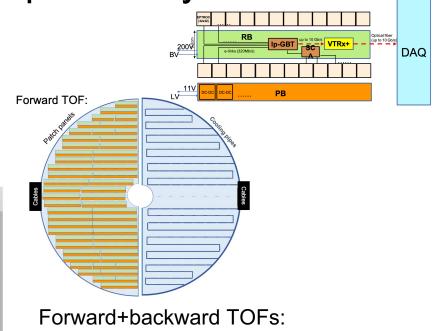

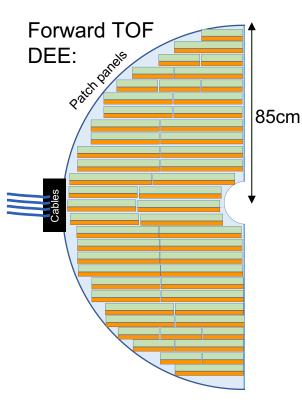

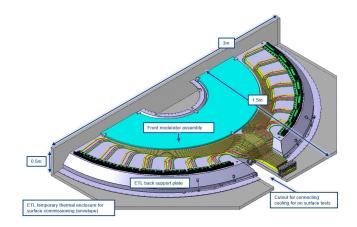

## ETOF Layout (v0)

**48 EPTROCs**

40 EPTROCs

24 EPTROCs

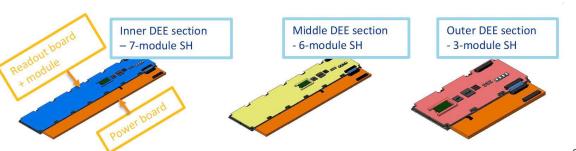

3 types of modules to tile the full DEE:

For each module:

- 1 fiber to DAQ

- 2 LV cables (1 supply, 1 return)

- 2 BV cables (1 supply, 1 return)

|               | Forward | Backward |

|---------------|---------|----------|

| Sensors/ASICs | 8704    | 4608     |

| LV cables     | 424     | 248      |

| HV cables     | 424     | 248      |

| Fibers        | 212     | 124      |

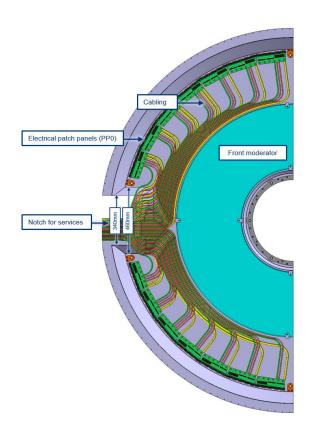

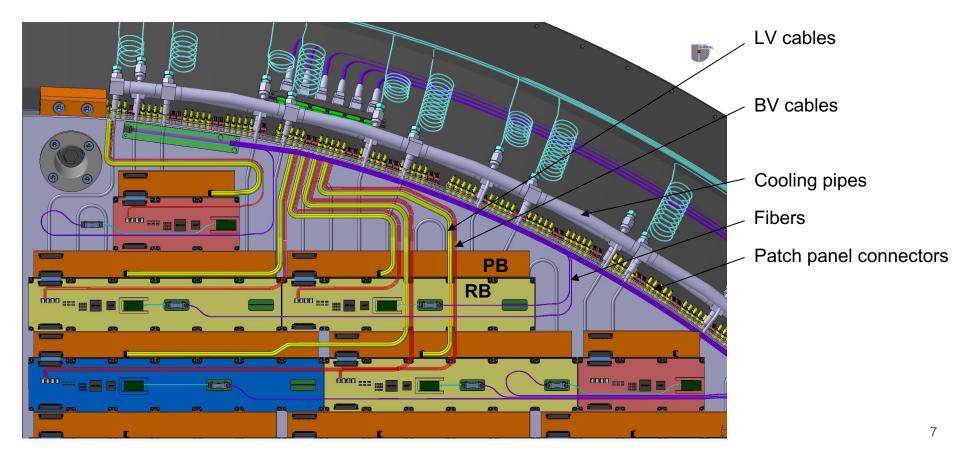

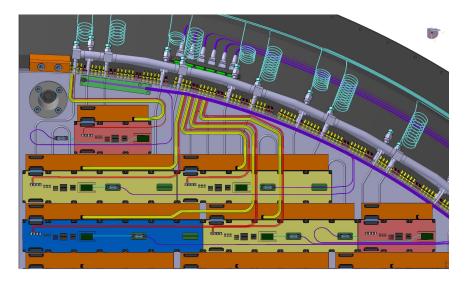

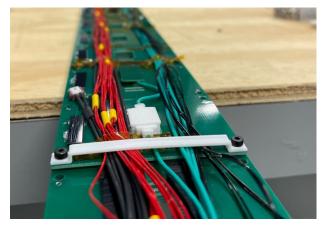

#### Service routing in CMS ETL

#### CMS ETL Layout

1: Flipped module 2: Readout board 3: Board-to-board connector 4: Connector to powerboard 5: BV connector 6: GBT-SCA 7: lpGBT 8: VTRx+

- 20------m The

### CMS ETL Layout

#### Power budget

0.5x0.5 mm<sup>2</sup> option

| 0.5x0.5              | Forward | Backward |

|----------------------|---------|----------|

| Sensors              | 0.6kW   | 0.35kW   |

| EPTROC               | 8.5kW   | 4.8kW    |

| DC-DC                | 3.5kW   | 2kW      |

| lpGBT,<br>VTRx+, SCA | 0.5kW   | 0.3kW    |

| Power<br>cables      | 0.5kW   | 0.3kW    |

| Total                | 13.6kW  | 7.75kW   |

#### 0.8x0.8 mm<sup>2</sup> option

| 0.8x0.8              | Forward          | Backward         |

|----------------------|------------------|------------------|

| Sensors              | 0.2kW            | 0.13kW           |

| EPTROC               | 3.2kW<br>(6.4kW) | 1.8kW<br>(3.6kW) |

| DC-DC                | 1.3kW            | 0.75kW           |

| lpGBT,<br>VTRx+, SCA | 0.2kW            | 0.12kW           |

| Power<br>cables      | 0.2kW            | 0.12kW           |

| Total                | 6.1kW            | 2.9kW            |

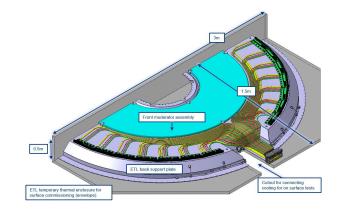

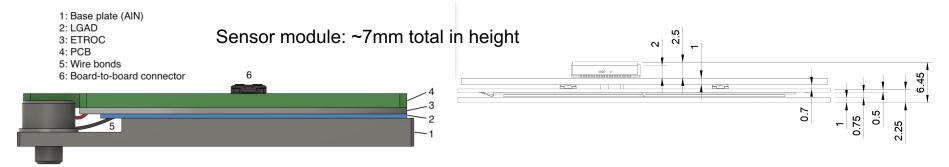

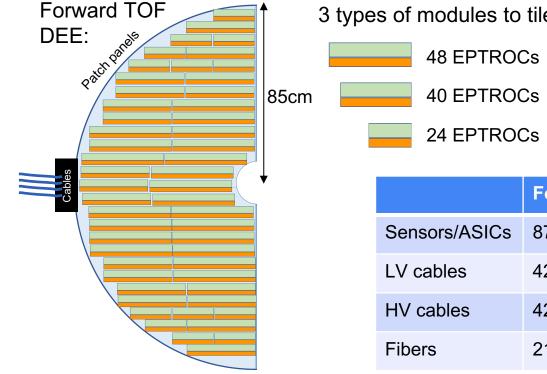

#### Space requirement in z

#### Mockups developed for CMS-ETL

#### Space requirement in z

| Elements in Z              | Envelope |

|----------------------------|----------|

| Front face of electronics  | 7 mm     |

| Cooling and support disk   | 8 mm     |

| Rear face of electronics   | 7 mm     |

| Patch panels + cables      | 22 mm    |

| Back support plate         | 5 mm     |

| Thermal screen (if needed) | 18 mm    |

| Total                      | 67 mm    |

#### Q&A from Tim

#### Q. slide # 5: This is the internal detector wiring?

Yes, correct. This is wiring on the readout PCB board.

Q. how is the power regulation done on the read-out board?

LV is regulated via DC-DC converters

I see here you have an inner assembly where everything is connected via a patch panel.

Q. Do you envision the patch panel as separate circuit boards mounted around the detector?

#### Yes, this is correct.

Q. Are you considering specific connector types or part numbers at this point, for both the modules and patch boards?Yes, we have some preliminary estimate of numbers but they may change a bit as the design evolvesQ. What is the LV and HV requirement for the modules?

#### 12V for LV and 200-350V for HV.

Q. slide #13: what is ~ space given here for cable routing?

We estimated total space requirement in z of about 7 cm max including all cables, service etc.

### Summary

Considered alternative design of eTOF layout with large pitches of AC-LGADs

- 0.5x0.5 mm<sup>2</sup> pixel option could leverage the same ASIC design as RPs but may impose high demand in cooling infrastructure and more materials budget

- Increasing the pixel pitch can help substantially reduce the # of channels and thus cooling requirements (by a factor of 2.56 for 0.8x0.8 mm<sup>2</sup> and 4 for 1x1 mm<sup>2</sup>), while still meeting the requirement in position resolution (also true for RPs?)

- For 0.8x0.8 mm<sup>2</sup> pitch as an example, cooling budget is estimated around 9-15 kW. Designs with other options can be easily derived.

We should study the performance and impact of increased pitch size in simulations (in progress) and R&Ds (eRD112 in FY23) in detail.

Next, we plan also to start working on details of design including electronics, cables etc. and evaluate more realistic material budget.

### Backups

### Optimizing the layout (v1)

### Optimizing the layout

#### $0.5 \times 0.5 \text{ mm}^2 \text{ option}$

|               | Forward | Backward |

|---------------|---------|----------|

| Sensors/ASICs | 8704    | 4608     |

| LV cables     | 424     | 248      |

| HV cables     | 424     | 248      |

| Fibers        | 212     | 124      |

#### 0.8x0.8 mm<sup>2</sup> option

|               | Forward | Backward |

|---------------|---------|----------|

| Sensors/ASICs | 3112    | 1744     |

| LV cables     | 248     | 184      |

| HV cables     | 248     | 184      |

| Fibers        | 124     | 92       |

For each module:

- 1 fiber to DAQ

- 2 LV cables (1 supply, 1 return)

- 2 BV cables (1 supply, 1 return)

### **ETOF** Power budget

| 0.8x0.8              | Forward          | Backward         |

|----------------------|------------------|------------------|

| Sensors              | 0.2kW            | 0.13kW           |

| EPTROC               | 3.2kW<br>(6.4kW) | 1.8kW<br>(3.6kW) |

| DC-DC                | 1.3kW            | 0.75kW           |

| lpGBT,<br>VTRx+, SCA | 0.2kW            | 0.12kW           |

| Power cables         | 0.2kW            | 0.12kW           |

| Total                | 6.1kW            | 2.9kW            |

| 1.3x1.3              | Forward          | Backward         |

|----------------------|------------------|------------------|

| Sensors              | 0.1kW            | 0.05kW           |

| EPTROC               | 1.2kW<br>(2.4kW) | 0.7kW<br>(1.4kW) |

| DC-DC                | 1.3kW            | 0.75kW           |

| lpGBT,<br>VTRx+, SCA | 0.2kW            | 0.12kW           |

| Power cables         | 0.2kW            | 0.12kW           |

| Total                | 3kW              | 1.8kW            |

### **ETOF** Layout

3 types of modules to tile the full DEE:

For each module:

- 1 fiber to DAQ ٠

- 2 LV cables (1 supply, 1 return)

- 2 BV cables (1 supply, 1 return) •

|               | Forward | Backward |

|---------------|---------|----------|

| Sensors/ASICs | 8704    | 4608     |

| LV cables     | 424     | 248      |

| HV cables     | 424     | 248      |

| Fibers        | 212     | 124      |

### Optimizing the layout