Beam-Hjet breakup tagging: RHIC Run23 tests

> W. Schmidke EICUG polarim. mtg. 05.10.22

- Motivation

- Run22 tests presentation EICUG polar. mtg. 11.05.22\*

- Requirements for Run23 tests:

Hjet readout extra module ?

need input from JLab DAQ experts:

different readout mode Hjet/tagger modules ?

- Hjet trigger  $\rightarrow$  tagger module ?

- Extra slides: info on Hjet/JLab readout (A. Poblaguev)

# Motivation

h.p

h

dipole

target

h.p

- Absolute polarimetry requires elastic scattering:

e.g. Hjet @ RHIC pp→pp, <sup>3</sup>He @ EIC hh→hh or hp→hp

- Proton can break up e.g. pp→pNπ large mass difference (p,pπ) ~100 MeV resolved in Hjet recoil detector

- <sup>3</sup>He can break up hh→hdp or hh→hnpp small mass difference (h,dp) or (h,npp) few MeV not resolved in Hjet recoil detector

- Can tag <sup>3</sup>He breakup fragments, reject inelastic events, estimate corrections to elastic

- Implementation might look like:

- EIC IR design group:

- place @ IR4 defined for polarimeters\*

- with required sequence: Hjet→dipole→drift space→n,p taggers (d too close to beam)

\*https://indico.bnl.gov/event/16983/contributions/67945/attachments/43143/72531/EICUG\_polarim\_07.09.22.pdf

taggers

# Run22 tests: pp

- Spare ZDCs (hadron calorimeters) installed: downstream of Hjet, after dipole bend Read out in spare pC polarimeter DAQ channels (easy, run between pC measurements) dipo

- Tagger hits correlated w/ p-beam: <sup>1</sup>/<sub>2</sub>/<sub>2</sub>/<sub>2</sub>/<sub>2</sub> hit, p-beam same bunch structure

**Demonstrated:** tagging p-beam breakup in Hjet o target interactions

5000

3000

2000

1000

a

õ

abort

RHIC bunch #

# Run23 tests: <sup>3</sup>He p

• 2023: plan to have RHIC APEX\* time with <sup>3</sup>He beam

\*Accelerator Physics EXperiments

- Allow ultimate breakup tagging test: hp→pnpp, detect recoil p in Hjet, n in taggers estimate breakup rate (expect few %)

- Need to correlate Hjet, tagger hits: same DAQ system

Present Hjet DAQ (96 channels) details extra slides

- each channel autonomous: trig. on pulse > threshold

- saved each channel

- full wave form, ~80 samples, ~4 nS

- Amplitude & Time reconstructed from wave form

- time stamp: RHIC bunch # (0-119)

RHIC revolution #, incremented every 12.8  $\mu$ S together identify unique bunch ×ing, offline correlate different chan.

Saved in buffer, read out VME every ?

# DAQ: Hjet + taggers

- Present Hjet DAQ has 6 FADC250 modules, 16 chan. each

- Could sacrifice few (4-6) unimportant Hjet chan., plug in taggers

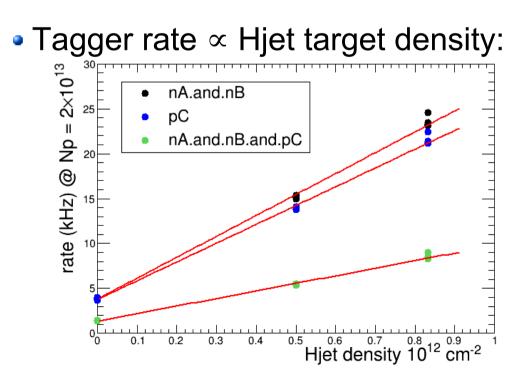

- But rates: Hjet channels ~10 Hz; tagger channels 10's kHz taggers would quickly fill module buffers

- Can we add another FADC250 module for tagger chans. ?

If yes:

Can the tagger module store all but waveform samples ? save factor ~20 buffer filling rate. Maybe still too high...

**Better solution:**

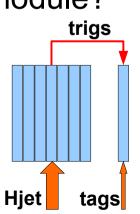

- Can Hjet channel triggers be used to trigger tagger module?

- tagger rate stored < Hjet rate, no rate problem

- but no independent measure of tagger rates

• Andrei's slides on Hjet VME readout @ PSTP 2015:

Ruhr-Universität Bochum / Germany

14. - 18. September 2015

BROOKHAVEN NATIONAL LABORATORY

## New DAQ for the HJET polarimeter at RHIC

Andrei Poblaguev Brookhaven National Laboratory

<u>The RHIC/AGS Polarimetry Group:</u> I. Alekseev, E. Aschenauer, G. Atoian, A. Bazilevsky, K.O. Eyser, H. Huang, D.Kalinkin, Y. Makdisi, A.Poblaguev, W. Schmidke, D. Smirnov, D. Svirida, G. Webb, K. Yip, A. Zelenski

## New VME based DAQ (2015-...)

- Wiener VME 64x crate + Single Board Computer

- 6 FADC Boards (Jefferson Lab)

- 16 channels per board

- 12 bit

- 250 MHz

- General Purp. Firmware

- internal trigger

- deadtime-less

- raw waveform available

- External signals:

- > 244 MHz Clocks derived from 28.15 MHz RF signal

- > Sync Reset (every Jet Cycle, ~5 min)

- Front Panel Signal Distribution Module (Jefferson Lab)

- BNL V128 Input-register (Jet polarization status)

Total Rate in HJET ~ 10 kHz (2 Mbyte/s) allows us to use FADC general purpose firmware and acquire raw waveforms (80 samples -> 328 ns)

- The new DAQ was assembled without destroying the old DAQ. The infrastructure of the old DAQ was employed in the new one.

- It takes only about 30 min. to switch between DAQ's (reconnection of 96 signal cables)

- A software interface to use new data format with old analysis was developed.

- This allows us to migrate to new DAQ smoothly.

- New data analysis was also developed.

## Single Board Computer (SBC)

## CONCURRENT

### VX 915/011-14

- 4-core 2.1 GHz Intel Core i7-3612QE Processor

- 16 Gbytes DDR3-1600 DRAM with ECC

- VME64 interface supporting A64/A32/A24/A16/D64/D32/D16/D8(E0), MBLT64, 2eSST and 2eVME

- 500 Gbyte Hard Drive

- Red Hat Enterprise 6 Linux

The SBC is powerful enough to provide detailed online analysis in parallel with data taking.

### FADC250

|          | fADC250                                |                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R 57     | VME64x Flash ADC Module Specifications |                                                                                                                                                                                                                                                                                                                                                                                      |

|          | Signal Inputs                          | Range     -0.5V, -1V & -2V. User Selectable       Offset     ±10% FS per channel via DACs                                                                                                                                                                                                                                                                                            |

| )        | Clock                                  | Sampling         250 MSPS, Differential           Jitter         1 pS (10-bit ADC), 350 fS (12-bit ADC)           Source         Internal and External                                                                                                                                                                                                                               |

| ) )      | Control<br>Inputs/Outputs              | Clock       IN – Diff., LVPECL (Front Panel & Backplane)         Trigger       IN, OUT - Differential (Front Panel & Backplane)         Status 1       OUT – Differential (Front Panel & Backplane)         Status 2       OUT – Differential (Front Panel & Backplane)         Sync       OUT – Differential (Front Panel & Backplane)         Trigger SWSoftware Strobe (Internal) |

|          | Conversion<br>Characteristics          | Resolution 10-bit (8 and 12-bit by chip replacement)<br>INL ± 0.8 LSB<br>DNL ± 0.5 LSB<br>SNR 56.8 dB @ 100 MHz Input<br>Data Latency 32 nS                                                                                                                                                                                                                                          |

|          | Trigger Latency                        | 78μS                                                                                                                                                                                                                                                                                                                                                                                 |

|          | Data Memory                            | 8 µS                                                                                                                                                                                                                                                                                                                                                                                 |

| JLAB     | Data Processing                        | Sparcification<br>Windowing<br>Charge, Pedestal, Peak<br>Time (Over Threshold, Relative to trigger)<br>Output (Backplane, VXS)                                                                                                                                                                                                                                                       |

| fADC-250 | Interface                              | VME64x – 2eVME Data Transfer Cycles (40, 80, 160 & 320<br>MB/sec) with VXS-P0                                                                                                                                                                                                                                                                                                        |

| fal)     | Packaging                              | 6U VME64x                                                                                                                                                                                                                                                                                                                                                                            |

| _        | Power                                  | +3.3V, +5V, +12V, -12V                                                                                                                                                                                                                                                                                                                                                               |

|          | F.B., J.AB. FADC_SPBC.DOC              |                                                                                                                                                                                                                                                                                                                                                                                      |

### The board was designed for the Jlab Hall D.

- 16 Channel

- 12 bit, 250 MHz

- Internal Trigger , deadtime free

- Waveform length up to 511 samples (2 μs)

- Dead Time Free

#### **External Inputs:**

(from the Signal Distribution Card)

- Trigger

- Sync Reset

- Clocks

## Front Panel Signal Distribution Module for the FADC250 (FP-SD)

2

3

5

6

В

D

F

1 - 7

CLOCK SVNC\_RESET TRIGGER

MOD TRIGGER BUSY

EXT CLOCK GND

EXT SYNC\_RESET EXT TRIGGER OR BUSY

EXT CLOCK

EXT SVNC\_RESET

OR BUSY

MOD F2 TRIGGER MOD 7 TRIGGER MOD 6 TRIGGER

MOD 5 TRIGGER

MOD 4 TRIGGER MOD 3 TRIGGER

MOD 2 TRIGGER MOD 1 TRIGGER

- The SD-FP distributes <u>synchronized</u> Clock, Trigger, and Sync Reset signals to up to 7 FADC250 boards.

- Supports external and internally generated signals

For RHIC Run15 we borrowed 7 FADC 250 boards and FP-SD from JLab.

We have got significant help from Jlab Fast Electronics Group. FADC Firmware was upgraded in accordance with our requirements.

We acknowledge the outstanding contribution of Chris Cuevas, Hai Dong, Ed Jastrzembski, and Bryan Moffit to the development the new DAQ for the Hjet polarimeter at RHIC.