## SRO at JLab - Status

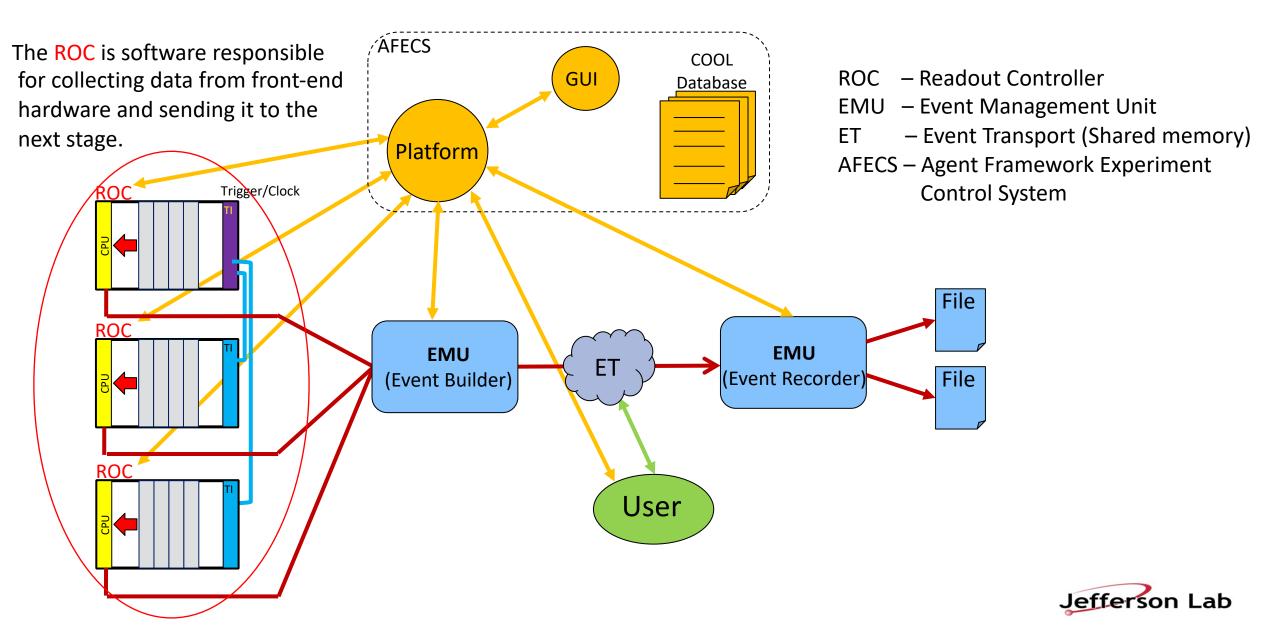

- **Objective:** Support the traditional triggered model along with streaming in one integrated DAQ framework.

- Leverage existing hardware. Add firmware and software to support Streaming.

- Focus on the parallels of the the JLab framework with the planned ePIC DAQ.

- General info on data formats we are using

- Next steps...

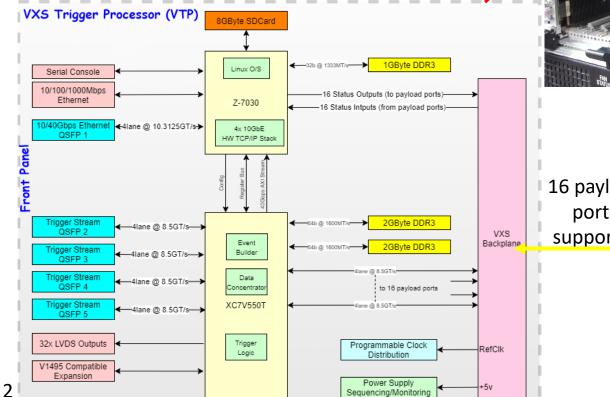

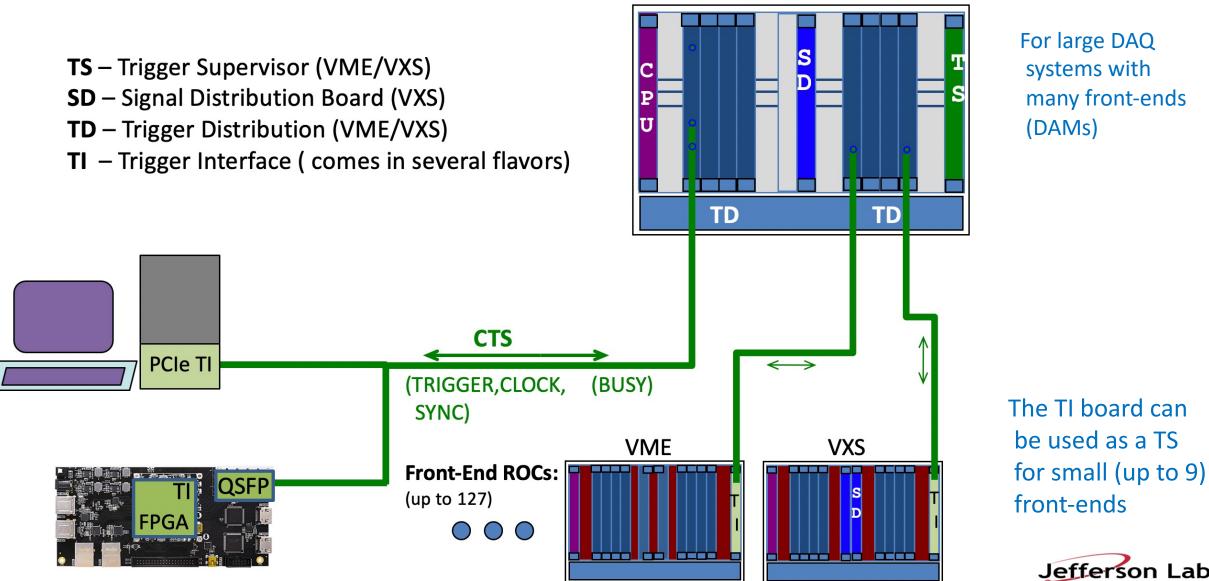

# **JLab VXS Platform**

Linux OS on the Zync-7030 SoC (2-core ARM 7L, 1GB DDR3) 10/40Gbps Ethernet output

#### Xilinx Virtex 7 FPGA

20x4 serial lanes from both the VXS backplane and the Front panel. 4GB DDR3 RAM

### **Single Crate System**

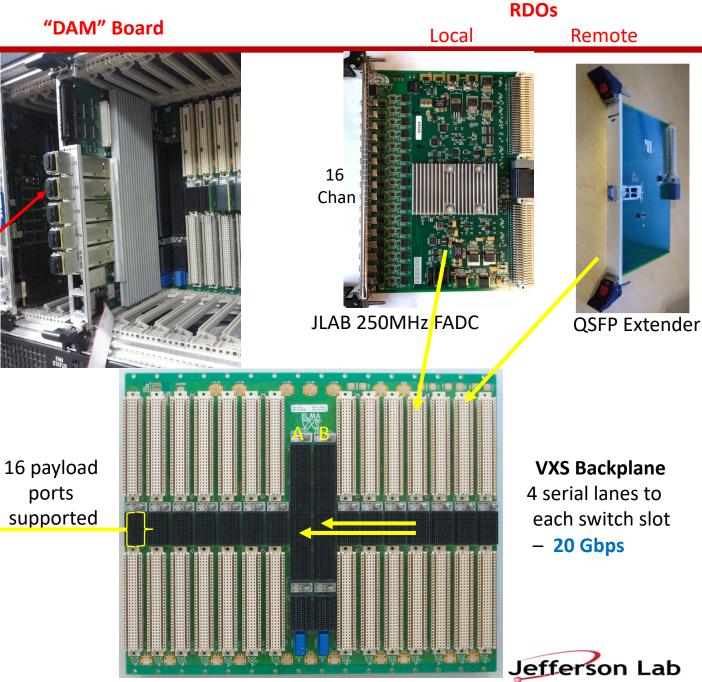

# JLAB FADC as an RDO (Streaming mode)

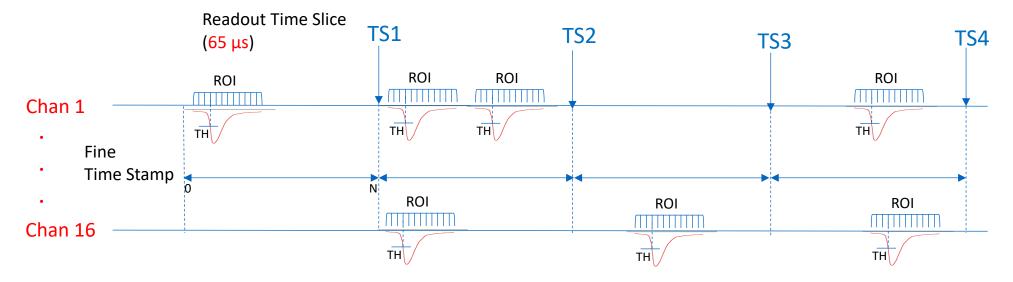

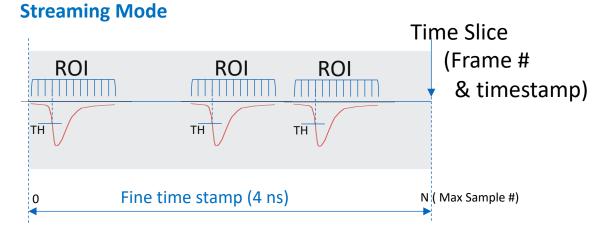

A 250 MHz FADC generates a 12 bit sample every 4ns. That's 3 Gb/s for one channel. 16 channels is 48 Gb/s. Currently, we identify a threshold crossing (hit) and integrate charge over a ROI and send only a sum and timestamp for each hit.

Available VXS bandwidth will allow for 1 hit every 32ns from all channels sent to the DAM. A data frame (**Time Slice**) for all available hits is generated in the DAM (currently every 65µs)

2 FPGAs manage the FADC processing

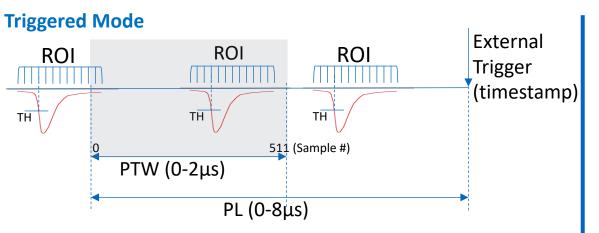

Note: The FADC can still simultaneously operate in triggered mode with an 8µs pipeline and 2µs readout window. With readout over the VMEBUS

# **FADCs - Triggered vs Streaming**

PL: Programmed Lookback PTW: Time window

#### Data we get on a trigger:

- All waveform samples for the ROI

- Threshold Sample # (hit time within the PTW)

- Trigger absolute timestamp

1 Frame = N Clocks (up to 16bits, currently 65536 ns)

### Data we get for a Frame:

- Pedestal subtracted sums over an ROI for every hit over threshold

- Threshold sample # (fine time stamp for each hit)

- Frame # and absolute timestamp for the frame

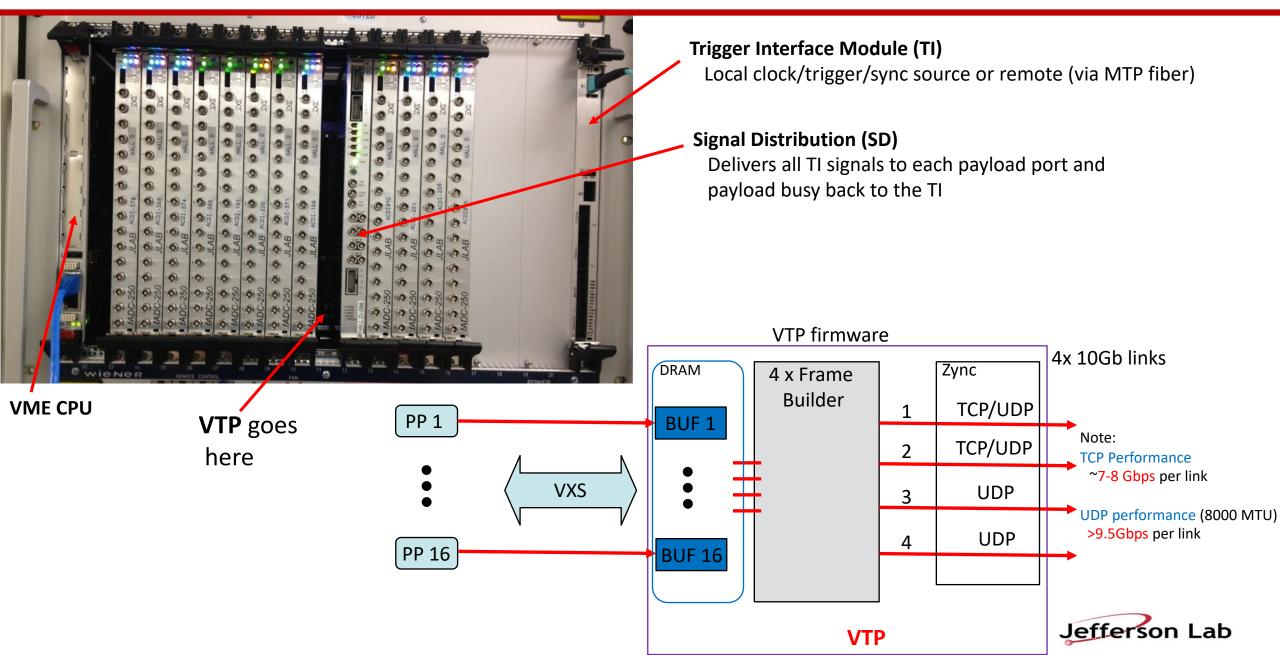

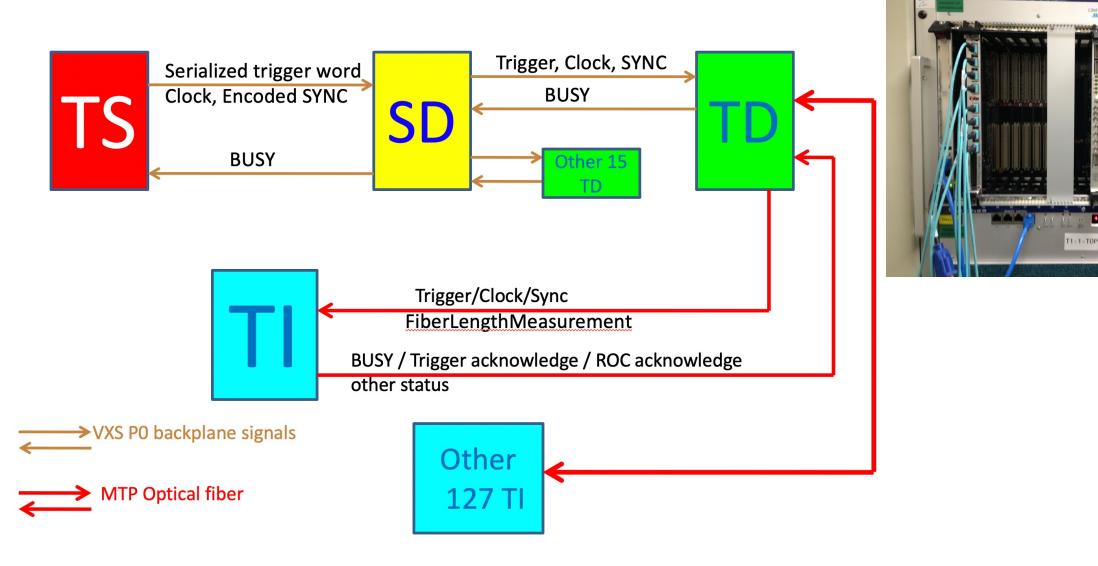

## JLab Timing System Components (GTU)

+5V0 5+02V 12A

## JLAB Clock and Trigger Distribution System

#### **Trigger Distribution Crate**

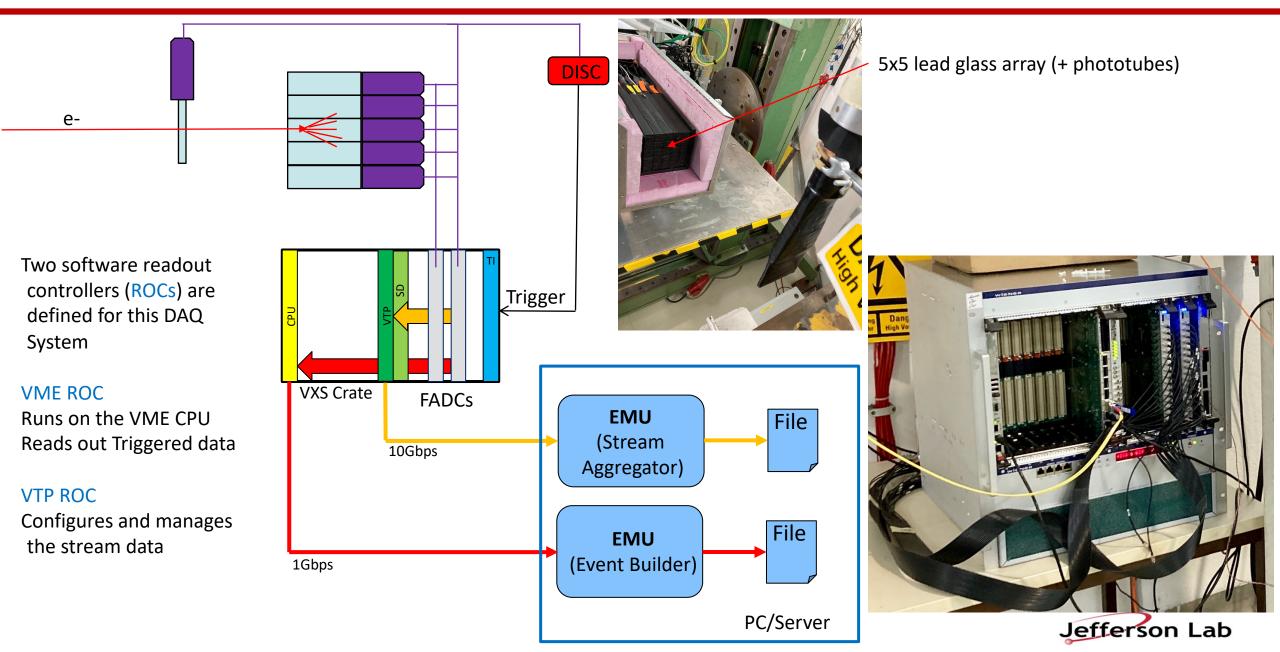

# Simple Hybrid DAQ System

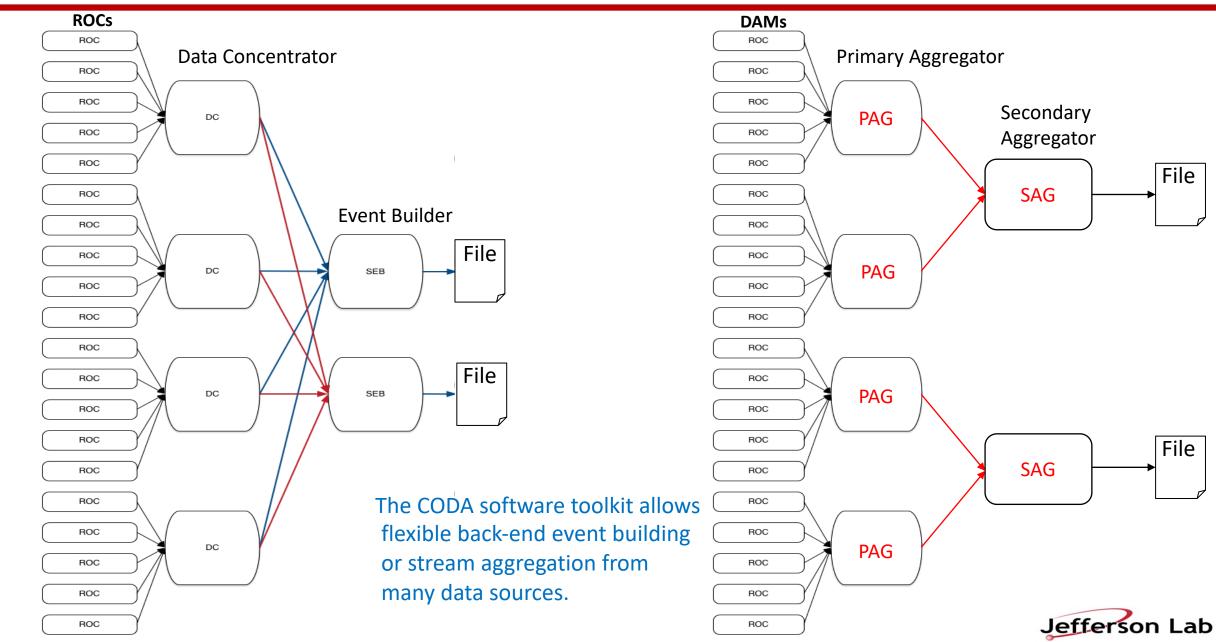

# Scaling up the DAQ

**Triggered DAQ**

Streaming DAQ

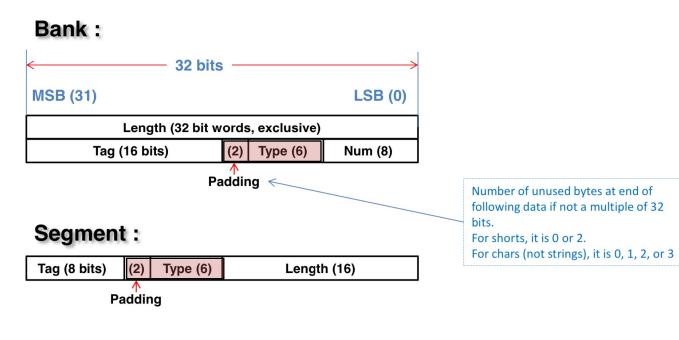

### **EVIO Primitive Data Structures**

• EVIO data formats are based on 32 bit words

#### **Evio Header Formats**

### Tag Segment :

| Tag (12 bits) | Type (4) | Length (16) |

|---------------|----------|-------------|

|---------------|----------|-------------|

#### **Evio Content Type Codes**

| Content Type | Primitive Data Type          |  |  |

|--------------|------------------------------|--|--|

| 0x0          | 32 bit unknown (not swapped) |  |  |

| 0x1          | 32 bit unsigned int          |  |  |

| 0x2          | 32 bit float                 |  |  |

| 0x3          | 8 bit char* (string)         |  |  |

| 0x4          | 16 bit signed int            |  |  |

| 0x5          | 16 bit unsigned int          |  |  |

| 0x6          | 8 bit signed int             |  |  |

| 0x7          | 8 bit unsigned int           |  |  |

| 0x8          | 64 bit double                |  |  |

| 0x9          | 64 bit signed int            |  |  |

| 0xa          | 64 bit unsigned int          |  |  |

| 0xb          | 32 bit signed int            |  |  |

| Охс          | Tag Segment                  |  |  |

| 0xd          | Segment                      |  |  |

| 0xe          | Bank                         |  |  |

| Oxf          | Composite                    |  |  |

| 0x10         | Bank                         |  |  |

| 0x20         | Segment                      |  |  |

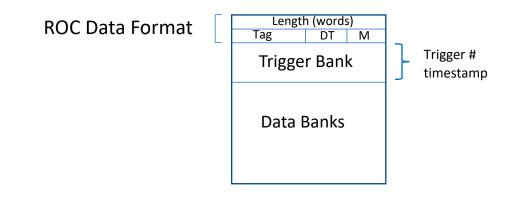

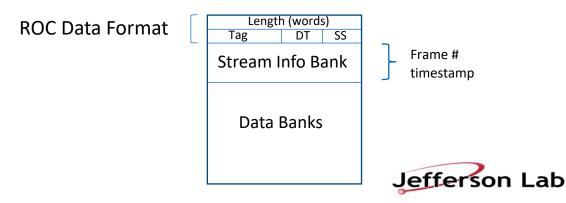

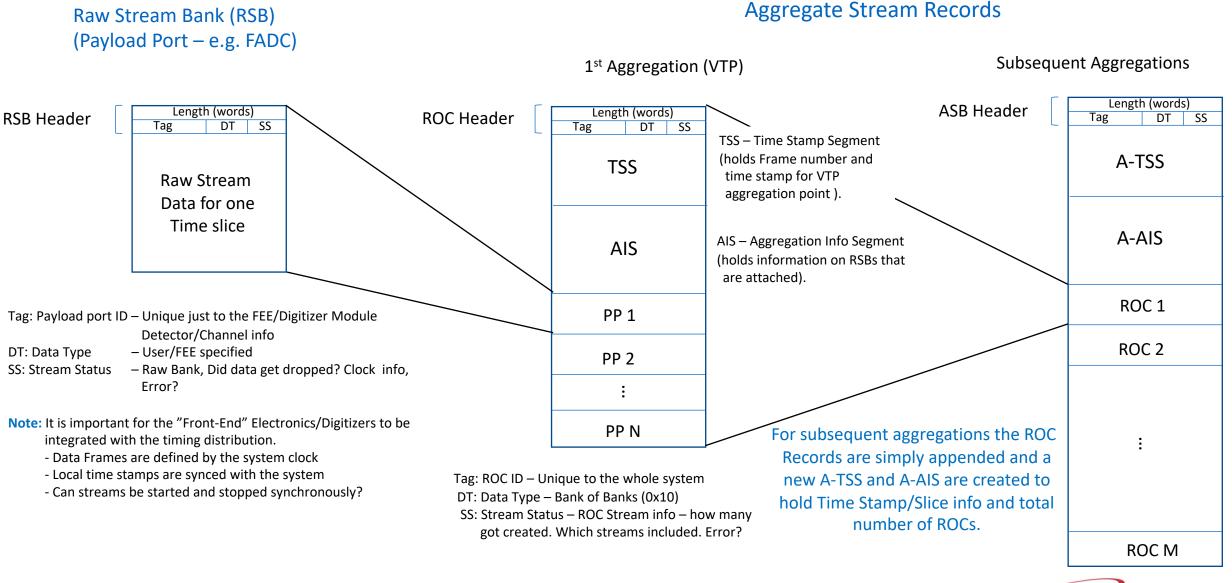

### **Stream Aggregation – Data formats**

Jefferson Lab

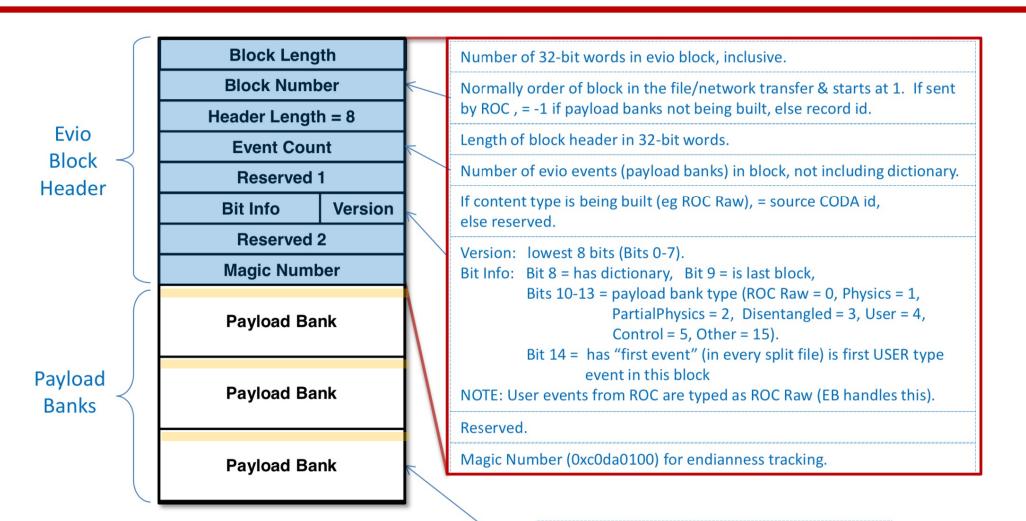

## **CODA Data Transport and Files**

Each payload bank can be a Physics Event, ROC

Raw Record, Control Event, or User event. Note:

there may be a block header between any 2

payload banks.

Format used when sending all types of online CODA data over the network. They are in standard evio buffer/file output format with block headers.

Jefferson Lab

# Where do we go from here?

- Expand current JLab FADC functionality to support waveform readout.

This will require new congestion management on the FADC FPGA.

- Set up larger scale (multiple crate) streaming tests using existing detector systems in the experimental halls.

- This will give analysis software groups some real stream data to chew on.

- Integration of other ASIC-based front-end electronics within the JLab streaming environment still needs to be developed ("remote" RDOs).

- Migrate existing firmware and software libraries to new "DAM" hardware (e.g. FELIX 182).

# **Backup Slides**

## The CODA Data Acquisition Toolkit