# Discrepancy of MIP Peak between 2019 and 2021 Beam Tests

RIKEN/RBRC Itaru Nakagawa

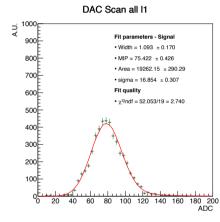

# **DAC** scan comparison

https://indico.bnl.gov/event/15657/contributions/63079/attachments/40865/68318/INTT\_energydeposit\_summary.pdf

#### Testbeam2019, 100 V Proton beam, 120 GeV

The peaks are different

Original though: because of the difference of the supplied voltage

2021 Test beam was operated at 50V instead of 100V. However, observed MIP peak position (collected charge) was too low compared to what we expect from theoretical prediction.

$$\frac{MIP_{2021BT}}{MIP_{2019BT}} = \frac{75}{118} \sim 0.63$$

### 2019 Beam Test

- RCDAQ. FPHX parameters were operated via expert-GUI.

- I couldn't find the exact records of FPHX parameters for the 2019 beam test though, it is likely FPHXs were operated with default parameters.

No specification in the gain setting. Unless we customize parameters via expert-GUI, FPHX just runs with default parameters (or loaded from a default setting file?)

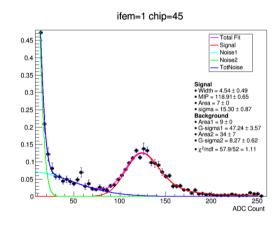

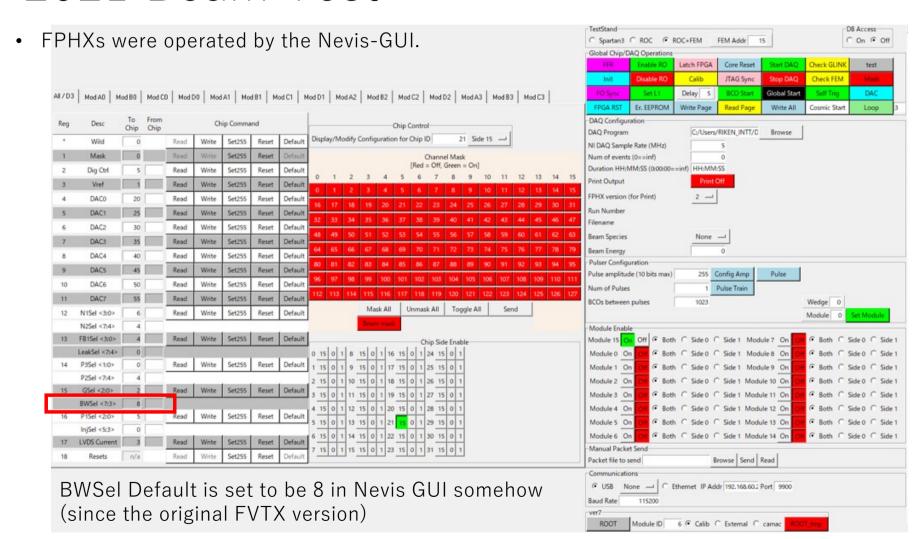

## Expert GUI Screenshot provided from Jin Huang (Typical FVTX Operating Condition)

## 2021 Beam Test

# FPHX Parameters

| Name              | Description      | Default | 2019 Beam<br>Test (FVTX) | 2021 Beam<br>Test |                                        |

|-------------------|------------------|---------|--------------------------|-------------------|----------------------------------------|

| Vref              |                  | 1       | 1                        | 1                 |                                        |

| DAC0              |                  | 8       | 8                        | 15                |                                        |

| DAC1              |                  | 16      | 16                       | 30                |                                        |

| DAC2              |                  | 32      | 32                       | 60                |                                        |

| DAC3              |                  | 48      | 48                       | 90                | Reg Desc To                            |

| DAC4              |                  | 80      | 80                       | 120               | * Wild 0                               |

| DAC5              |                  | 112     | 112                      | 150               | 1 Mask 0 2 Dig Ctrl 5                  |

| DAC6              |                  | 144     | 144                      | 180               | 3 Vref 1<br>4 DAC0 20                  |

| DAC7              |                  | 176     | 176                      | 210               | 5 DAC1 25                              |

| N1Sel             |                  | 6       | 6                        | 6                 | 6 DAC2 30<br>7 DAC3 35                 |

| N2Sel             |                  | 4       | 4                        | 4                 | 8 DAC4 40<br>9 DAC5 45                 |

| FB1Sel            |                  | 4       | 4                        | 4                 | 10 DAC6 50                             |

| LeakSel           |                  | 0       | 0                        | 0                 | 11 DAC7 55<br>12 N1Sel <3:0> 6         |

| P3Sel             |                  | 0       | 0                        | 0                 | N2Sel <7:4> 4 13 FB1Sel <3:0> 4        |

| P2Sel             |                  | 4       | 4                        | 4                 | LeakSel <7:4> 0                        |

| GSel              | Gain Select      | 2       | 2                        | 2                 | 14 P3Sel <1:0> 0<br>P2Sel <7:4> 4      |

| BWSel             | Bandwidth Select | 4       | 4                        | 8                 | 15 GSel <2:0> 2<br>BWSel <7:3> 8       |

| P1Sel             |                  | 5       | 5                        | 5                 | 16 P1Sel <2:0> 5 InjSel <5:3> 0        |

| InjSel            |                  | 0       | 0                        | 0                 | 17 LVDS Current 3                      |

| LVDS Current [mA] |                  | 1       | 3                        | 2                 | Nevis GUI defaults<br>(Even from 2013) |

| Side 0 Side 1 | F      | 001        |             |         | _             | . \           | 0    |

|---------------|--------|------------|-------------|---------|---------------|---------------|------|

| Side 1        | (      | 201        | .9 B        | ear     | n I           | est)          |      |

|               | Side ( | Chip Setti | ngs [Editab | le]     |               | Side 0 Cont   | rols |

| Vref          | 1      | 1          | 1           | 1       | 1             | Vref          |      |

| DAC 0         | 8      | 8          | 8           | 8       | 8             | DAC 0         | 1    |

| DAC 1         | 16     | 16         | 16          | 16      | 16            | DAC 1         | 1    |

| DAC 2         | 32     | 32         | 32          | 32      | 32            | DAC 2         | 3    |

| DAC 3         | 48     | 48         | 48          | 48      | 48            | DAC 3         | 4    |

| DAC 4         | 80     | 80         | 80          | 80      | 80            | DAC 4         | 8    |

| DAC 5         | 112    | 112        | 112         | 112     | 112           | DAC 5         | 11   |

| DAC 6         | 144    | 144        | 144         | 144     | 144           | DAC 6         | 14   |

| DAC 7         | 176    | 176        | 176         | 176     | 176           | DAC 7         | 17   |

| N1Sel         | 6      | 6          | 6           | 6       | 6             | N1Sel         |      |

| N2Sel         | 4      | 4          | 4           | 4       | 4             | N2Sel         |      |

| FB1Sel        | 4      | 4          | 4           | 4       | 4             | FB1Sel        |      |

| LeakSel       | 0      | 0          | 0           | 0       | 0             | LeakSel       |      |

| P3Sel         | 0      | 0          | 0           | 0       | 0             | P3Sel         |      |

| P2Sel         | 4      | 4          | 4           | 4       | 4             | P2Sel         |      |

| GSel          | 2      | 2          | 2           | 2       | 2             | GSel          |      |

| BWSel         | 4      | 4          | 4           | 4       | 4             | BWSel         |      |

| P1Sel         | 5      | 5          | 5           | 5       | 5             | P1Sel         |      |

| InjSel        | 0      | 0          | 0           | 0       | 0             | InjSel        |      |

| LVDS Current  | 7      | 7          | 7           | 7       | 7             | LVDS Current  |      |

| Accept Hits   | 7      | 7          | 7           |         | V             | Accept Hits   | V    |

| Global Inject |        |            |             |         |               | Global Inject |      |

| Serial Select | 0 1    | 0 1        | 0 1         | 0 1     | 0 1           | Serial Select | 0    |

|               | 0+1    | 0+1        | 0+1         | 0+1     | 0+1           |               | 0+1  |

| Channel Mask  |        |            |             |         |               | Channel Ma    | isk  |

|               | Chip 1 | Chip 2     | Chip 3      | Chip 4  | Chip 5        |               |      |

| Revert Chan   | ges Re | ed Chips   | Update El   | EPROM W | rite to Chips | Wedge FF      | R    |

| 4  | DAC0 | 15  |

|----|------|-----|

| 5  | DAC1 | 30  |

| 6  | DAC2 | 60  |

| 7  | DAC3 | 90  |

| 8  | DAC4 | 120 |

| 9  | DAC5 | 150 |

| 10 | DAC6 | 180 |

| 11 | DAC7 | 210 |

|    |      |     |

## FPHX Gain Parameters

- P1Sel<2:0>: sets input transistor bias current = 10uA + [(4uA)(P1Sel)]. Default = 101. Higher bias current gives lower noise.

- Fb1Sel<3:0>: sets integrator feedback transistor bias current Ifb = 1.67nA + [(1.67nA)(Fb1Sel)]. Default = 0100. This current defines the equivalent feedback resistance (Rfb ~ 0.05/lfb), which determines the output pulse fall time (in conjunction with the programmable integrator feedback capacitor Cfb, yielding time constant RfbCfb).

- N1Sel<3:0>: Integrator source follower bias = 1.25uA + [(0.625uA)(N1Sel)].

Default = 0110.4

- LeakSel<3:0>: maximum DC input leakage current compensation = [1.6(Ifb) + (3.33nA)(LeakSel)]. Default = 0000.<sup>42</sup>

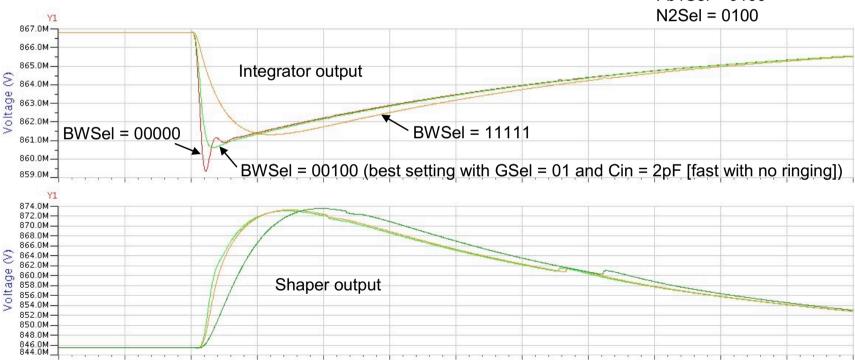

- GSel<2:0>: determines integrator feedback capacitance Cfb = 25fF + [(8.6fF)(GSel<0>) + (25fF)(GSel<1>) + (50fF)(GSel<2>)]. Default = 010.

- With a fixed shaper gain of about 5, the nominal system transfer gain can then be set to approximately 46, 50, 60, 67, 85, 100, 150, or 200 mV/fC.

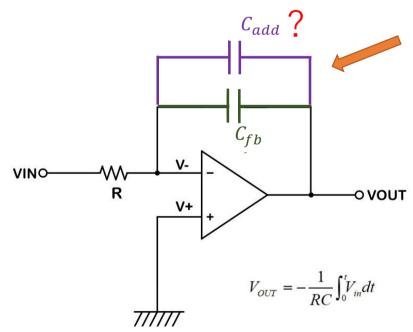

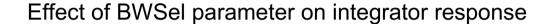

- BWSel<4:0>: adds capacitance to the dominant node of the integrator. Explicit added capacitance = 10fF + [6fF(BWSel)]. Default = 00100. Used to compensate for the effects of varying input capacitance and gain setting on the integrator response. ←

- N2Sel<3:0>: Shaper bias current = 1uA + [(0.5uA)(N2Sel)]. Default = 0100.

This is used to set the bandwidth of the shaper, which determines the output pulse rise time (peaking time). A shaper bias of 3.5uA results in a peaking time of approximately 60ns. Higher settings result in faster peaking times.

- P2Sel<3:0>: Comparator bias current = 0.5uA + [(0.25uA)(P2Sel)]. Default = 0100. Higher settings reduce comparator delay.

- P3Sel<1:0>: Comparator second stage pullup bias current. Default = 00. Mainly affects comparator trailing edge delay higher settings reduce the delay.

- InjSel-2:0>: Digital inject circuit DAC setting. Charge inject magnitude = (1Ke)(InjSel + 1). Default = 000 (1Ke).

- Vref<1:0>: Shaper DC reference voltage = 150mV + [(60mV)(Vref<1:0>)].

Default = 01. For maximum dynamic range, set Vref as low as possible while still maintaining linearity.

- Vth0<7:0> (Threshold ADC 0): 0th ADC comparator (discriminator) threshold = Vref + [(4mV)(Vth0)]. Default Vth0<7:0> = 00001000 (Vref + 32 mV).

- Vth1<7:0>: 1st ADC comparator threshold = Vref + [(4mV)(Vth1)]. Default Vth1<7:0> = 00010000 (Vref + 64 mV).

- Vth2<7:0>: 2nd ADC comparator threshold = <u>Vref</u> + [(4<u>mV)(</u>Vth2)]. Default Vth2<7:0> = 00100000 (<u>Vref</u> + 128 mV).

- Vth3<7:0>: 3rd ADC comparator threshold = <u>Vref</u> + [(4mV)(Vth3)]. Default Vth3<7:0> = 00110000 (<u>Vref</u> + 192 mV).

- Vth4<7:0>: 4th ADC comparator threshold = <u>Vref</u> + [(4<u>mV)(</u>Vth4)]. Default Vth4<7:0> = 01010000 (<u>Vref</u> + 320 mV).

• GSel<2:0> Def=010

$C_{fb}[fF] = 25 + 8.6 \cdot GSel\langle 0 \rangle + 25 \cdot GSel\langle 1 \rangle + 50 \cdot GSel\langle 2 \rangle$

• BWSel<4:0> Def=00100

$$C_{add}[fF] = 10 + 6 \cdot BWSel$$

#### Total Capacitance

$$C_{Total} = C_{fb} + C_{add}$$

?

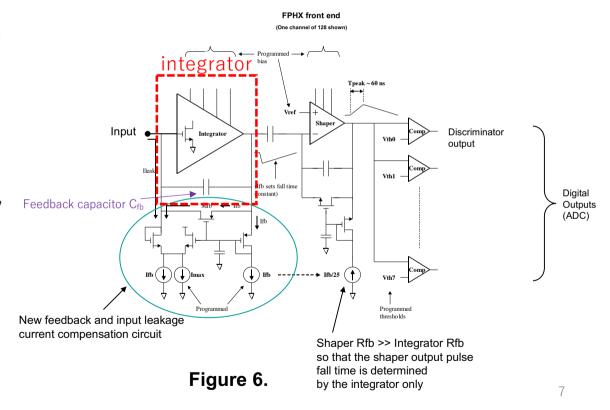

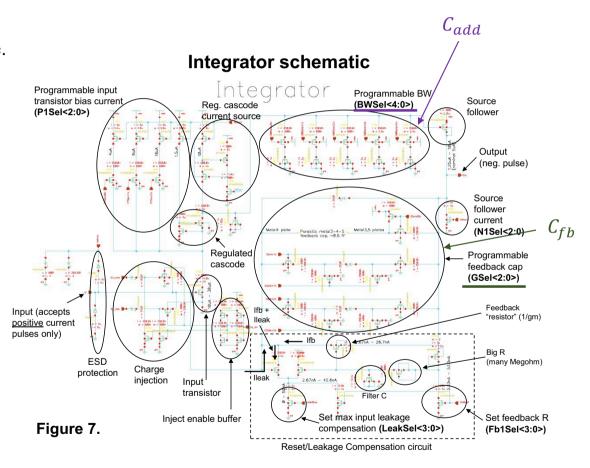

# FPHX Integrator Schematic

A new type of continuous reset and leakage compensation circuit has been designed for the integrator. In Figure 6, a programmable current labeled Ifb sets the effective reset resistance. Mfb acts exactly like a resistor of value 1/gm for small signals, where gm depends directly on Ifb since Mfb is in weak inversion. This programmed resistance, in conjunction with the feedback capacitor, sets the RC fall time (return to baseline) of the shaped signal. For large signals, when the output swings more than a hundred mV or so, Mfb no longer looks like a resistor, but a constant current source. The return to baseline then becomes linear until the output approaches the reset level, at which point it becomes an exponential RC decay again.

#### Simplified conceptual diagram of one channel

# FPHX Integrator Schematic

• The integrator is shown in detail in Figure 7. The input transistor feeds a regulated cascode (to keep the open loop gain high), and is biased by a cascode current source. Additional input transistor bias current is programmed through switched current sources. The integrator bandwidth is adjustable via switched capacitors on the amplifier dominant node. The transfer gain is set with programmable feedback capacitors. A source follower drives the integrator output.

8

# Effect of BWSel Parameter

Qin = 2000e Cin = 2pF (total) GSel = 010 Fb1Sel = 0100

## FPHX Gain Calculation

• GSel<2:0> Def=010

$$C_{fb}[fF] = 25 + 8.6 \cdot GSel\langle 0 \rangle + 25 \cdot GSel\langle 1 \rangle + 50 \cdot GSel\langle 2 \rangle$$

• BWSel<4:0> Def=00100

$$C_{add}[fF] = 10 + 6 \cdot BWSel$$

#### **Total Capacitance**

$$C_{Total} = C_{fb} + C_{add}$$

| Beam Test               | 2019        | 2021        |

|-------------------------|-------------|-------------|

| GSel                    | 2 < 010 >   | 2 < 010 >   |

| BWSel                   | 4 < 00100 > | 8 < 01000 > |

| $C_{fb}[fF]$            | 25+25=50    | 25+25=50    |

| C <sub>add</sub> [fF]   | 10+6•4=34   | 10+6•8=58   |

| C <sub>total</sub> [fF] | 84          | 108         |

| V <sub>out</sub> [a.u.] | 1           | 0.78        |

$$V_{OUT} = -\frac{1}{RC} \int_0^t V_{in} dt$$

Observation Still not sufficient

$$\frac{MIP_{2021BT}}{MIP_{2019BT}} = \frac{75}{118} \sim 0.63$$

# Global Start

Initialization Sequence

```

Gef global_start_daq_prog():

send_fo_sync()

send_fpga_reset()

time.sleep(2)

#send_fo_sync()

send_mreset(regpanels)

send_init(regpanels)

send_enable_ro(regpanels)

send_latch()

#send_latch()

#send_latch()

#send_latch()

send_mreset()

send_enable_ro(regpanels)

send_paltch()

#send_latch()

#send_latch()

send_fem_lvll_delay(int(fem_lvll_delay_var.get()))

send_pulse_module(int(pulse_module_var.get()), int(pulse_wedge_var.get()), f(int(femaddr_var.get())))

send_bco_start()

send_calib()

send_calib()

start_daq_prog(regpanels)

```

Are the parameters automatically loaded to FPHX at the beginning of run?

Sending parameters routine?

return

```

def send_init[(self,wedgeaddr,femaddr):

# chip ID

chipid = int(self.chipid)

print 'ChipConfig.send init: Send init for chip %d' % (int(self.chipid))

Desc

regs = [ 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17 ]

Chip

# Which operation to perform on each register (1=Write, 2=Set, etc. cf. FPHX manual)

# Here are the values to send for each register

vals = [ 128, # Global mask all channels -----

int(self.reg vals[1].get()), # The reset we initialize from the corresponding values

int(self.reg_vals[2].get()),

int(self.reg_vals[3].get()),

DACO

int(self.reg_vals[4].get()),

int(self.reg_vals[5].get()),

DAC<sub>1</sub>

int(self.reg_vals[6].get()),

int(self.reg_vals[7].get()),

DAC<sub>2</sub>

int(self.reg_vals[8].get()),

int(self.reg_vals[9].get()),

int(self.reg_vals[10].get()),

DAC<sub>3</sub>

DAC<sub>4</sub>

int(self.reg_vals2[11].get())<<4 | int(self.reg_vals[11].get()),

int(self.reg_vals2[12].get())<<4

int(self.reg_vals[12].get()),

DAC5

int(self.reg_vals2[13].get())<<4

int(self.reg_vals[13].get()),

int(self.reg_vals2[14].get())<<3

int(self.reg_vals[14].get()),

BWSel

DAC<sub>6</sub>

int(self.reg_vals2[15].get())<<3 | int(self.reg_vals[15].get()),

int(self.reg_vals[16].get())

N1Sel <3:0>

length = int(17*4) # 17 commands

dest = TESTBENCH_FPHX # destination == 'to FPHX'

N2Sel <7:4>

print "Chip %d WedgeAddr 0x%02X:" % (chipid,(lambda:wedgeaddr if wedgeaddr else 0)())

FB1Sel <3:0>

#for r, o, v in zip(regs,ops,vals):

# print "Register %d: oper %d with val %d" % (r,o,v)

LeakSel <7:4>

P3Sel <1:0>

datalen = length

P2Sel <7:4>

data = create_string_buffer(datalen)

GSel <2:0>

offset = 0

BWSel <7:3>

for i in range(0,17):

word = make_fphx_cmd(chipid, regs[i], ops[i], vals[i])

P1Sel <2:0>

struct.pack_into(">I",data,offset,word)

IniSel <5:3>

offset += 4

LVDS Current

# if use_roc.get(): wedgeaddr = (0xF & self.moduleid) | (0xF & iside)<<4

if use_roc.get(): wedgeaddr = (0xFF)

if use_roc.get() == 2: femaddr = femaddr_var.get()

buf = create_packet(dest,data.raw,wedgeaddr,femaddr)

print 'ChipConfig.send_init: Send init packet = %s' % hexify_bytes(buf)

write_bytes_to_target(buf.raw,comm_panel.getTarget())

# Now send down the enable mask

self.send_mask(wedgeaddr,femaddr)

11

```

## To be confirmed

- FPHX operation conditions for 2019 and 2021 beam tests.

- Does default parameters in Nevis-GUI really loaded to FPHX automatically in the initialization routine of the global start?

- Integrator circuit. If  $c_{Total} = c_{fb} + c_{add}$  is correct.

- Actual measurement and comparison of MIP position BWSel=4 vs BWSel=8 is mandatory to observe the actual response.

# Programming Strategy

- First determine **GSel** based on the desired approximate transfer gain (approx. 50 200 mV/fC).

- Then depending on the value of the input capacitance (Cin), program **BWSel** to achieve fast integrator response without ringing.

- For Cin = 2 pF (1.5 pF detector + 0.5 pF parasitic):

If GSel = 000, set BWSel = 00000

If GSel = 010, set BWSel = 00100

If GSel = 100, set BWSel = 01000

If GSel = 110, set BWSel = 01100

BW

| Physics | Dec | Bin  |

|---------|-----|------|

| GSel    | 2   | 010  |

| BWSel   | 4   | 1000 |

Relevant setting for INTT

- For Cin = 1.5 pF (1 pF detector + 0.5 pF parasitic):

- If GSel = 000, set BWSel = 00001

- If GSel = 010, set BWSel = 00110

- If GSel = 100, set BWSel = 01010

- If GSel = 110, set BWSel = 01110

| • | For | Cin = 1 pF (0.5 pF detector + 0.5 pF parasitic):        |

|---|-----|---------------------------------------------------------|

|   |     | If $GSel = 000$ , set $BWSel = 00010$                   |

|   | _   | If $\mathbf{GSel} = 010$ , set $\mathbf{BWSel} = 01000$ |

|   | _ ' | If $GSel = 100$ , set $BWSel = 01110$                   |

|   | _   | If $GSel = 110$ , set $BWSel = 10101$                   |

|   |     |                                                         |

|   | Nevis | Dec | Bin  |

|---|-------|-----|------|

| - | GSel  | 2   | 010  |

|   | BWSel | 8   | 1000 |

- Program **Fb1Sel** based on the desired fall time constant

- Then program N2Sel to achieve the desired rise time/peaking time (rise and fall times will have some effect on the transfer gain)

- Program Vref to the lowest value possible that allows linear response (nominally 00)

- Based on the transfer gain, set the desired comparator thresholds

# FVTX NIM

section committee to too but also to combined accide.

The strip length increases with radius on the sensor, and goes from 3.4 mm at the inner radius to 11.5 mm at the outer radius, with a pitch of 75  $\mu$ m in the radial direction. Each sensor covers 7.5° in  $\phi$ , and since the strips are perpendicular to the radius, they make an angle of 86.25° with respect to the centerline, as can be seen in Fig. 4.

The data words are output over two LVDS serial lines at up to 200 MHz clock rate. The total power consumption of the FPHX is  $\sim$  390  $\mu$ W per channel. The noise, when the chip was wire bonded to a sensor with strips  $\sim$  2–11 mm in length ( $\sim$ 1–2.5 pF), was simulated and measured to be below the design specification of 500 electrons.

INTT Type-A ~ 2.5pF (78um, 12mm) Type-B ~ 3pF or so?