# Proximity focusing RICH with HRPPD sensors (and EICROC ASICs?) for the EIC e-endcap

1

### Alexander Kiselev (BNL)

Ad hoc meeting with detector and electronics experts, March 6, 2023

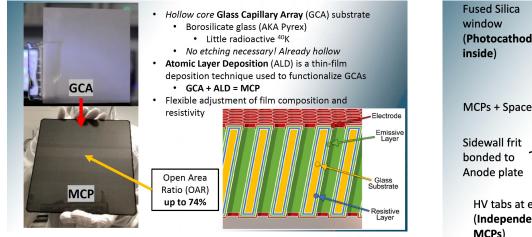

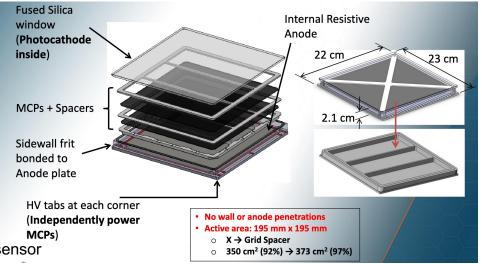

## LAPPDs / HRPPDs by Incom Inc.

- An affordable large area (finely pixelated) vacuum photosensor

- 10x10 cm<sup>2</sup> or 20x20 cm<sup>2</sup> active area

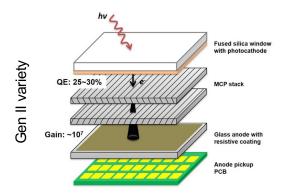

- DC- (Gen I) or capacitively (Gen II) coupled species

- DC-coupled strips or 2D pixellation

- Expected to be (very) cost efficient in mass production

- High enough quantum efficiency and uniform high gain up to ~10<sup>7</sup>

- Sub-mm spatial resolution for finely pixelated tiles

- Single-photon timing resolution on a ~50ps level or higher

### Possible LAPPD applications for the EIC

- mRICH / pfRICH: low dark noise, ToF capability (vs SiPMs)

- DIRC: expected to be more cost-efficient (vs other MCP-PMTs)

- dRICH: problematic, because of the magnetic field orientation

| mRICH / pfRICH | either DC-coupled or Gen II, 10cm formfactor |

|----------------|----------------------------------------------|

| DIRC           | DC-coupled, 10cm                             |

mRICH: 68 HRPPDs total

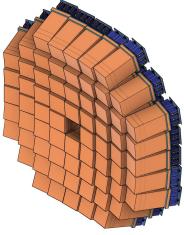

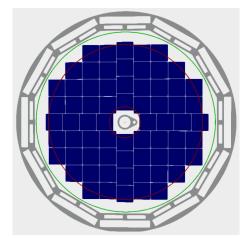

#### pfRICH sensor plane: 68 HRPPDs total

DIRC: 12\*3\*2 = 72 HRPPDs total

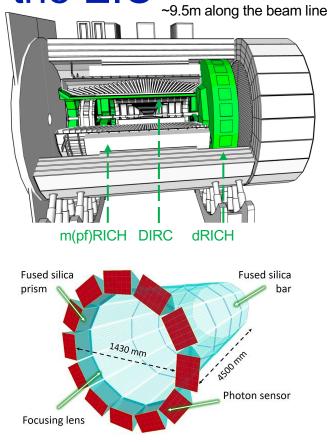

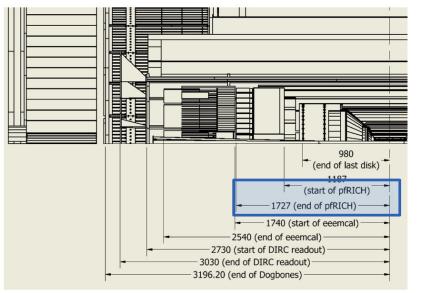

### Boundary conditions in the ePIC e-endcap

| Inner radius | Mimic beam<br>pipe flange |

|--------------|---------------------------|

| Outer radius | 643 mm                    |

| Total length | 541.5 mm                  |

## HRPPD photosensors & FEE

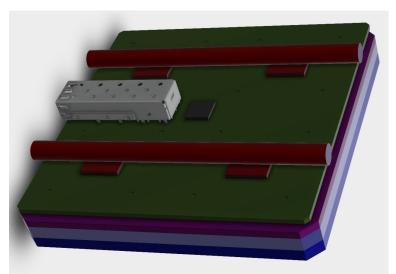

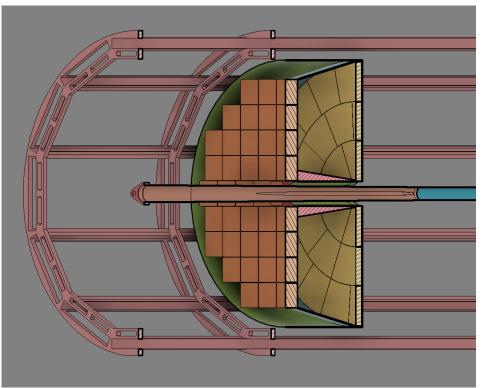

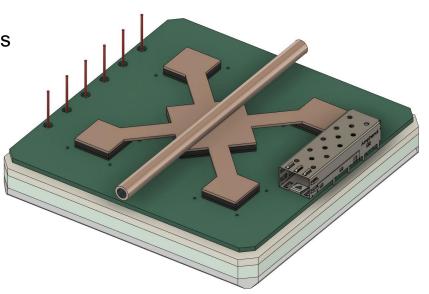

- A flat sensor wall with 68 12cm x 12cm HRPPDs

- 108mm x 108mm sensitive area

- Pixellation: 32x32 -> 1024 pads per sensor

- FEE: assume four 256ch EICROC chips per sensor; 50mm of space reserved overall

- ASIC bump-bonded to the PCB

- Can afford water cooling if needed

- There will be NO FPGA on board (but copper uplinks to an RDO located nearby)

### **Requirements to ASIC**

- Operating gain: variable, up to ~10<sup>7</sup>

- Expected single photon timing resolution ~50ps

- Pad capacitance <10pF, most likely can be made below 5pF

- Leading edge <1ns

- Noise level (DCR) ~1kHz/cm<sup>2</sup>

### **HRPPD-to-ASIC** interface

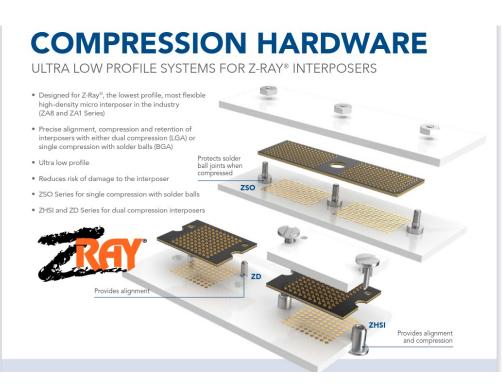

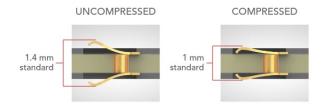

• Agreed to proceed with the Samtec compression interposers as a lead option