# **HGCROC & EICROC Introduction**

Jeff Landgraf

- There are TIC meetings planned to focus on HGCROC (July 10<sup>th</sup>) & EICROC (July 17<sup>th</sup>). Klaus asked DAQ for a short intro regarding these today, as an advertisement and introduction

- OMEGA and in2p3 have now committed considerable resources dedicated specifically to EIC ROC ASIC development. This is great news!

- eRD109 projects are also active developing and evaluating these ASICs

- Frederic Duluco (Ecole Polytechnique CNRS) gave a recent talk regarding these chips to the DAQ WG presentation and recording available at: <u>https://indico.bnl.gov/event/19653/</u>

- Similar base ASICs with modifications...

|   | Detector/Technology | Discrete/ASIC                    | Group | Awarded    |

|---|---------------------|----------------------------------|-------|------------|

| A | Calorimeter         | Discrete                         | IUCF  | April 2023 |

| В | Calorimeter         | HGCROC                           | ORNL  | April 2023 |

| С | dRICH               | ALCOR                            | INFN  | April 2023 |

| D | AC-LGAD             | EICROC                           | Omega |            |

|   |                     | FCFD                             | FNAL  |            |

|   |                     | Barrel L-M Serv. Hybrid          | ORNL  | April 2023 |

|   |                     | 3 <sup>rd</sup> Party Evaluation | UCSC  |            |

| E | MPGD/µRWell         | SALSA                            | CEA   |            |

|   |                     |                                  | USP   |            |

## HGCROC

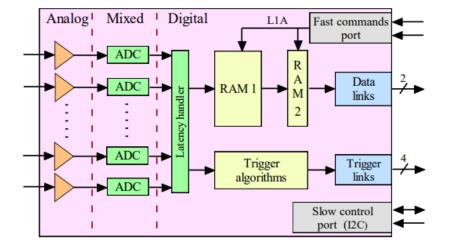

- HGCROC is a waveform digitizing ASIC aimed for digitizing the SiPM readout of the Calorimeters.

- 72 Channels version. HKROC exists with auto-triggered design but half the channels

- > The main challenges for EIC

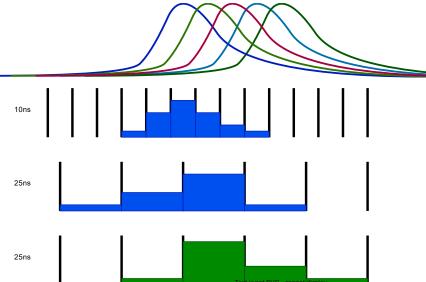

- Digitization Clock 40MHz rather than 100MHz

- Corrections for phase relative to BX

- Can hits be resolved to a BX? (Do they need to be?)

- Clock could be increased to 200MHz, but at the expense of timebin reduction (7→3-4), power use, and possible deadtime

- 10 Bit resolution, so dynamic range may be an issue

- Potential non-linear (or range dependent) pre-amp

- Potential TOT scheme

- "Could be converted to auto-triggered design"

## $\mathsf{HGCROC} \xrightarrow{} \mathsf{EGCROC}\operatorname{\mathsf{-EIC}}$

### What HGCROC-EIC could look like

□ HGCROC / H2GCROC (for SipM) with the integration of auto-triggering

Below is an calorimetry structure (not pixel like ALTIROC or EICROC but interfaces are similar)

- Each event passing the threshold is readout

- Check Hit rate

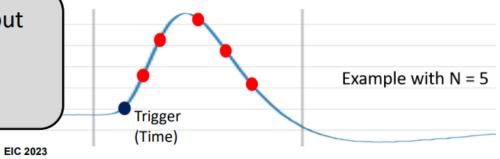

- Auto-trigger with N "samples" (1 to 7) (Same as HKROC)

(Frederic's talk)

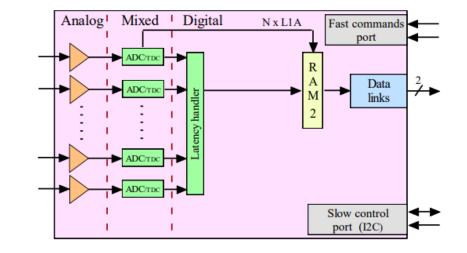

## EICROC

- EICROC is a TOA/TOT threshold based on the ALTIROC aimed for AC-LGAD readout (and possibly the HRPPDs). This could be used in the TOF, eTOF, RP, OffM, pfRICH, DIRC, BO,

- High Resolution, Pixelated readout: ~20ps timing resolution

- Is Clock 40MHz? If so, clock still must be synchronized to EIC BX clock, but digitization issues for HGCROC not as relevant because the only issue is the numerical translation between TOA values under different clock references

#### **YATLAS HGTD: ALTIROC ASIC**

- ALTIROC (Atlas Lgad Timing Integrated ReadOut Chip)

- Design under OMEGA responsibility Collaboration CERN Geneva, LPCF Clermont-Ferrand, IFAE Barcelona, SLAC Stanford, SMU Dallas

- 20 ps timing silicon timing detector for jet identification and pileup rejection

- ⇒ Pixel ASIC for precise timing measurements

- Qmin/Cd ~ 500  $\mu$ V with Cd ~4 pF (1300 x 1300  $\mu$ m2) and Vth min= 2 fC to be compared with other timing ASIC for which Qmin/C > 2 mV with Cd ~ 50 fF (50 x 50  $\mu$ m<sup>2</sup>) and Vth min = 0.1 0.2 fC

- ⇒ Mix of requirements specific to calorimetry and some of the requirements specific to pixel ASICs for trackers

- ⇒ Mix of Analog on Top design for the floorplan and analog performance + Digital on Top design for digital part (70% of the ASIC)

- ALTIROC2 : first 225 channels full matrix LGAD readout chip with 1 GHz preamplifier 4 pF detector capacitance = new territory in HEP

- See details in

https://indico.cern.ch/event/1127562/contributions/4904499/attachments/2511666/4317317/ ALTIROC2\_ATLAS\_HGTD.pdf

ALTIROC2= 2 x 2.1 cm<sup>2</sup>

15 x 15 pixels PA+ discri + TDC + SRAM + all digital blocks