# **AC-LGAD TOF Detector Requirements**

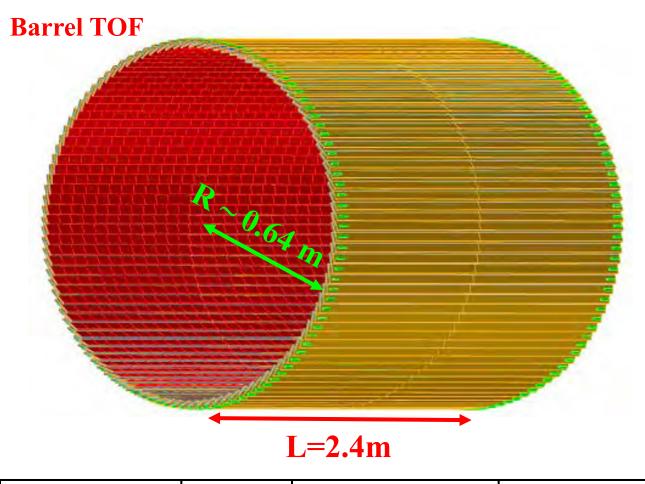

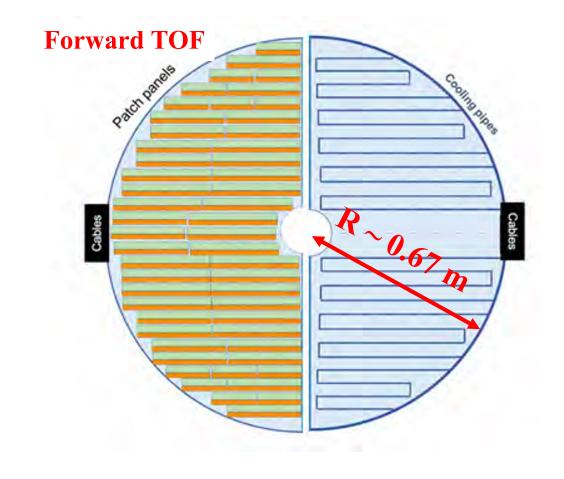

| Detector    | Area                | Channel size  | Channel number | Time resolution | Spatial resolution | Material budget |

|-------------|---------------------|---------------|----------------|-----------------|--------------------|-----------------|

| Barrel TOF  | ~10 m <sup>2</sup>  | 0.5mm x 10mm  | ~2.2 M         | 35 ps           | 30 μm in r·φ       | 0.01 X0         |

| Forward TOF | ~1.4 m <sup>2</sup> | 0.5mm x 0.5mm | ~5.6 M         | 25 ps           | 30 μm in x and y   | 0.05 X0         |

#### **TOF Requirements on Frontend ASIC**

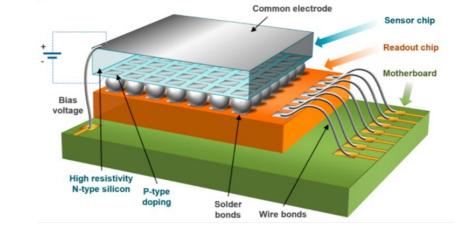

#### FTOF Requirements

- sensor bonding: **bump-bonding**

- pixel size  $0.5 \times 0.5 \text{ mm}^2$  (larger pixels being studied)

- pixel array **32 x 32 (TBD)**

- low power consumption ≤1 mW/channel

- low jitter  $\leq$ 15 ps for MIP@12 fC

- sensitivity to low charge (1-2 fC)

- time resolution (sensor+ASIC+clock)  $\leq$ 25 ps

- spatial resolution ≤30 microns

#### • BTOF Requirements

- sensor bonding: wire-bonding or bump-bonding (TBD)

- strip size **0.5** x **10** mm<sup>2</sup>

- strip array 64 x 2 (TBD)

- low power consumption  $\leq 1$  mW/channel

- low jitter  $\leq$  15 ps for MIP@12 fC

- sensitivity to low charge (1-2 fC)

- time resolution (sensor+ASIC +clock) ≤35 ps Interposer Sensor

- spatial resolution ≤30 microns

Sensor

**ROC**

Zhenyu Ye @ UIC 7/31/23

**ROC**

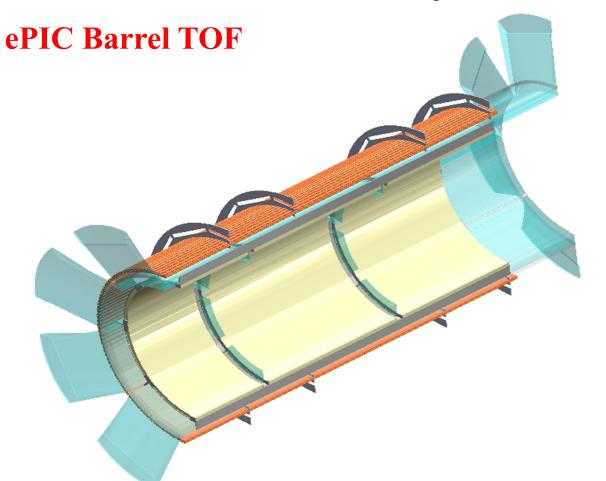

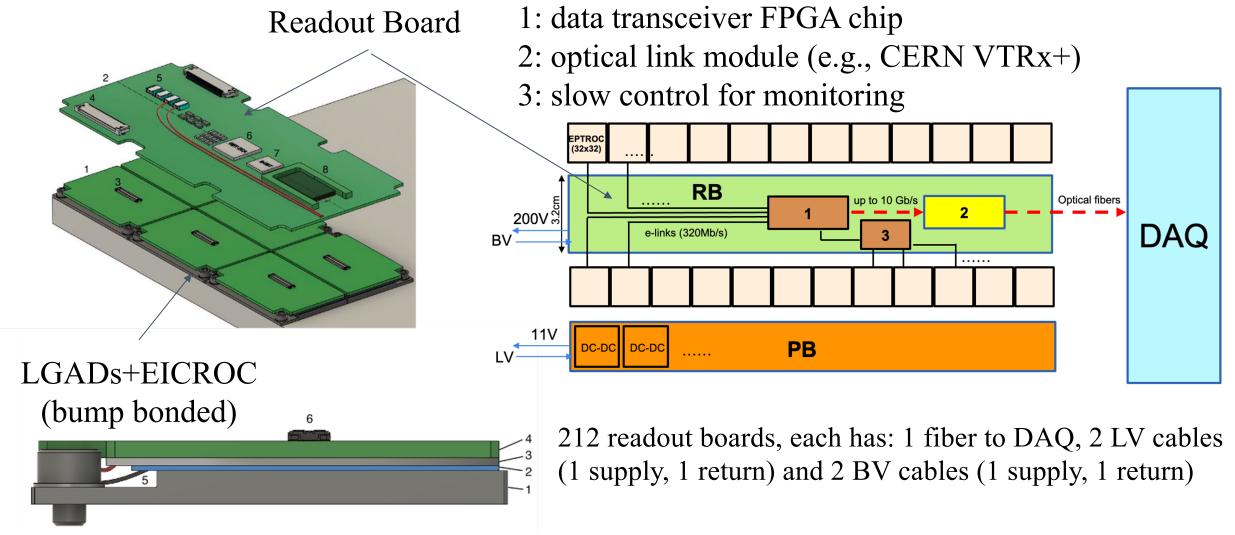

### **BTOF Detector Layout**

ePIC BTOF follows cylindrical silicon tracker design (e.g. STAR IST)

- Tilted stave modules overlap in phi to fully cover the azimuthal  $2\pi$  angle

- Readout boards connected to the end of staves are outside of the BTOF acceptance (see next talk)

- Cooling tubes with liquid coolant at room temperature to take the heat generated by frontend ASIC

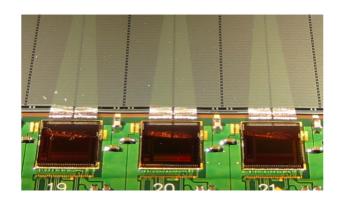

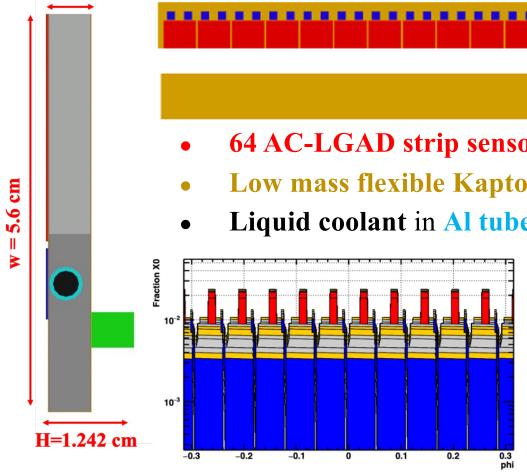

### BTOF Detector Module Conceptual Design

h=0.642 cm

- 64 AC-LGAD strip sensors, each 3.2\*4 cm<sup>2</sup> read out by 2 ASICs

- Low mass flexible Kapton PCB distributes power and I/O signals from connector

- Liquid coolant in Al tube embedded in CF light-weight structure for heat removal

144 modules, each with 2 readout boards with 2 LV+HV cables, 2 DAQ fiber, and 1 cooling line

Power consumption: ~4 kW (2.4kW for ASIC, 1 kW for DC-DC, 0.6kW for sensors+cable)

Total weight: ∼70 kG

#### **STAR IST**

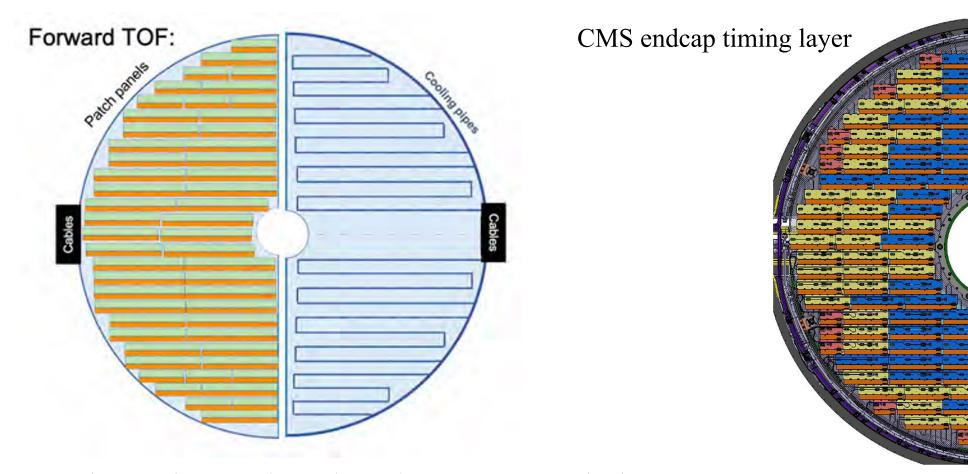

#### FTOF Detector Layout

Forward TOF layout, based on the CMS ETL design:

- Two halves DEEs made of light-weight (carbon fiber) support structure, tiled by rectangular modules of three types with different lengths

- Cooling tubes with coolant at room temperature to take the heat generated by frontend ASICs and other electronic elements

## FTOF Detector Module Conceptual Design

Power consumption: ~13 kW (8.5kW for ASIC, 3.5 kW for DC-DC, 1kW for sensors+cable)

- Considering  $0.7 \times 0.7$  mm<sup>2</sup> sensor design, which reduces the power budget by  $\sim 50\%$