# SRO timing distribution system in Japan

Hidetada Baba RIKEN, Nishina Center, Japan

## Overview

## under consideration

- please tell us your experiences

- Requirements are strongly dependent on facilities or experiments

- 100 ns v.s. 25 ps

- 1 meters v.s. 100 meters

- clock only v.s. data + clock

- local time v.s. global time v.s. sync. with accelerator frequency

- Hardware, methods

- latching scaler, white rabbit, etc

- KEK Honda's MIKUMARI (as described previous talk)

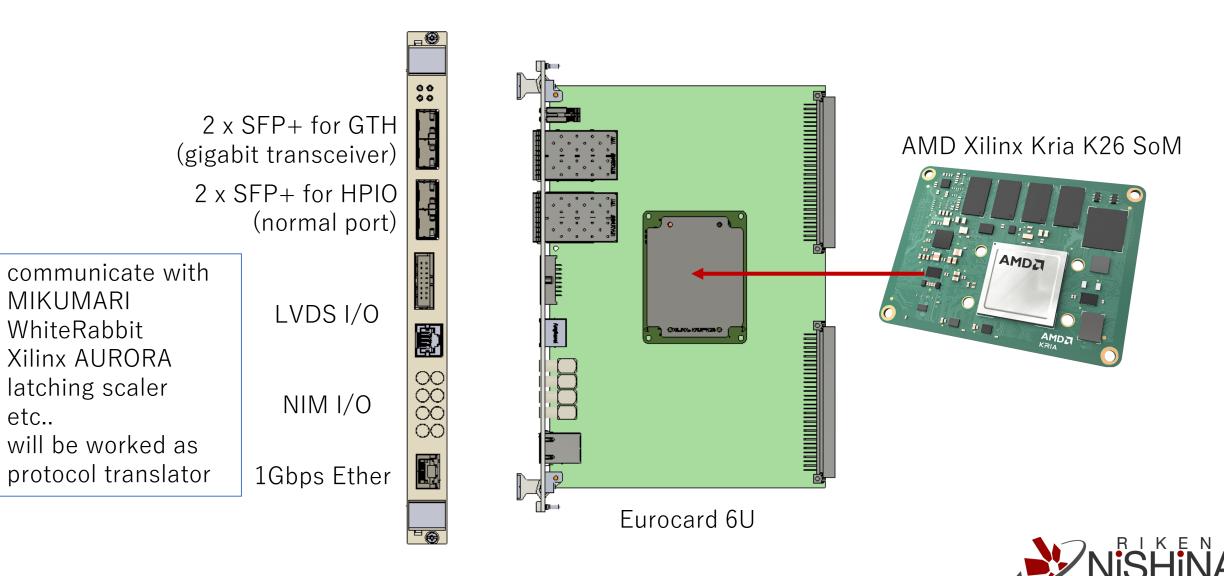

- Versatile clock transceiver module based on AMD Xilinx Kria (this talk)

- we have started some studies, we share our knowledge

- SPADI Alliance in Japan

- timing distribution system is not only for SRO, but also for trigger DAQs

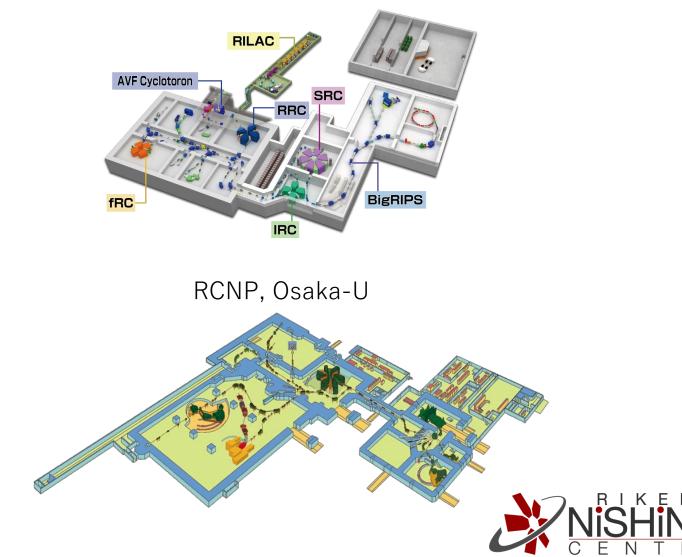

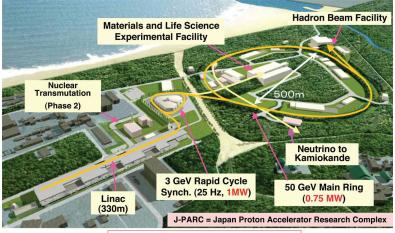

# Nuclear physics Accretor facilities in Japan

RIKEN, RIBF

J-PARC

Joint Project between KEK and JAEA

# Requirement of timing information

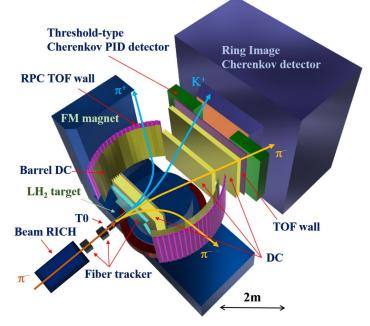

### J-PARC E50 (hadron experiment)

TOF **50 ps** @ few meters MIKUMARI is suitable

RIBF BigRIPS Particle Identification (RI-beam experiment)

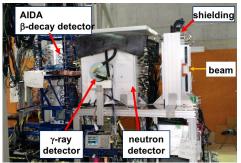

beta-decay experiment@RIBF RI's lifetime is milli-second order -> 10ns order synchronization

for Beta-decay experiments @ RIBF requirement is 10ns synchronization

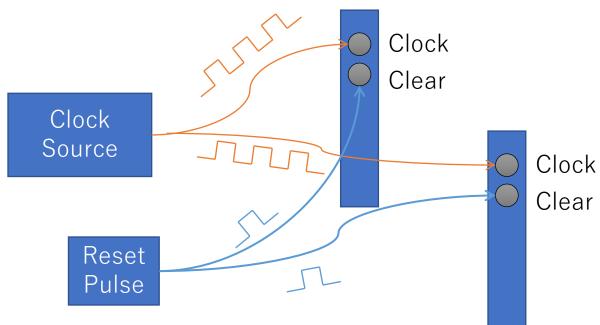

## time-stamp by plain HDL latching scaler

two metal coax. lines: clock + reset (T0) point-to-point + daisy-chain

100 MHz (**10ns**), 48 bits (kind of latching scaler)

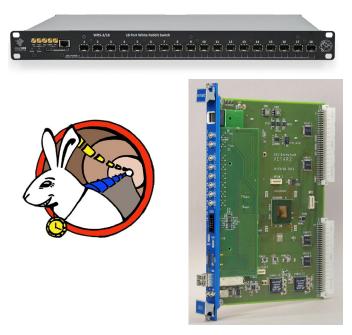

## white rabbit

1 optical cable : clock + data switch fabric

125MHz (**8ns**) from year 1970 (w/o phase detection in this case)

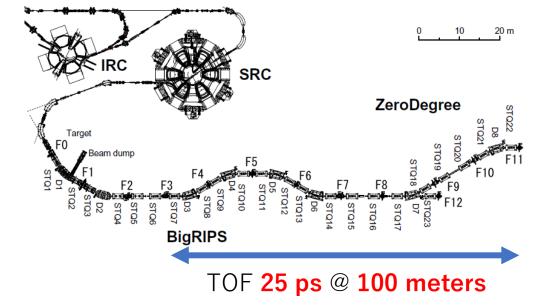

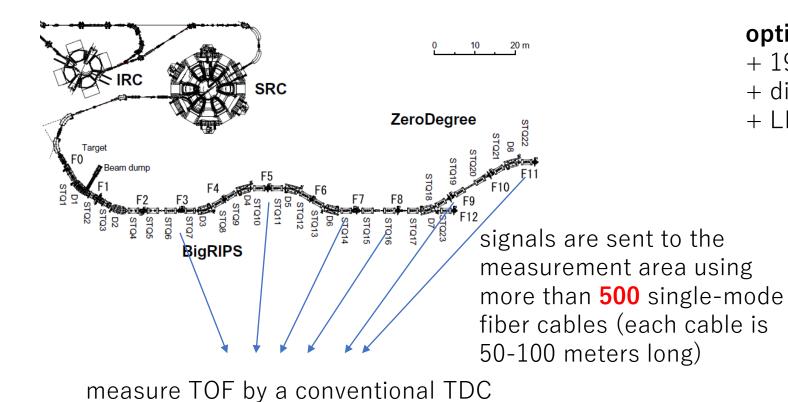

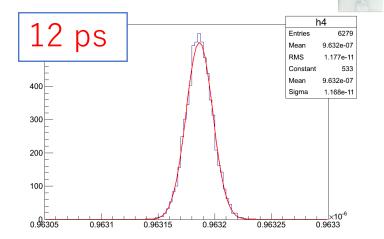

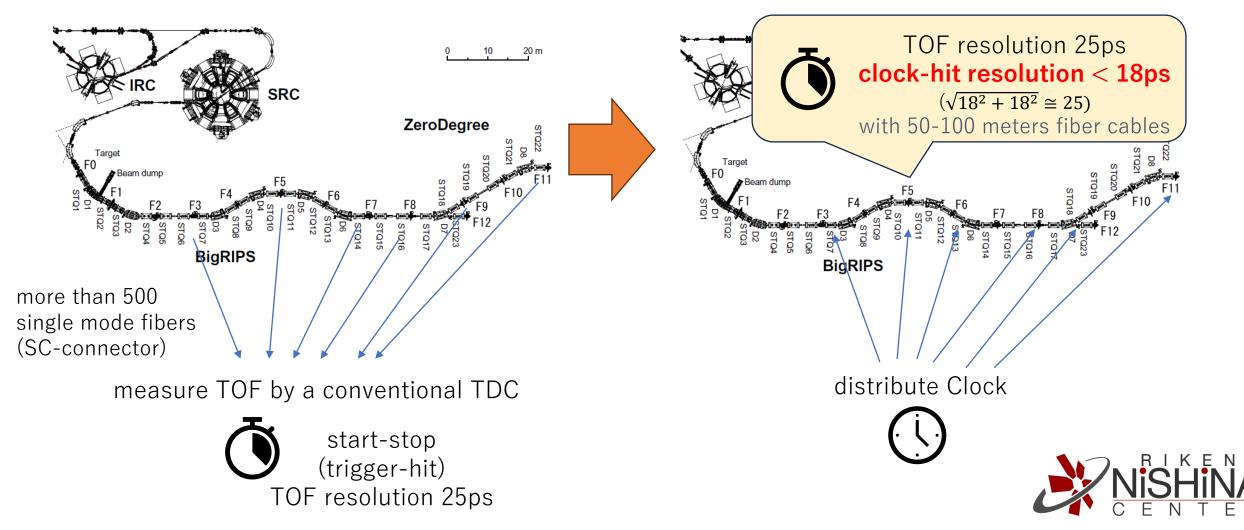

# at RIBF, 100-meters TOF 25ps ( $\sigma$ ) resolution

## Current system

start-stop

#### optical transmitter/receiver

+ 192meters single-mode fiber + discriminator + few meters coax

+ LEMO connectors

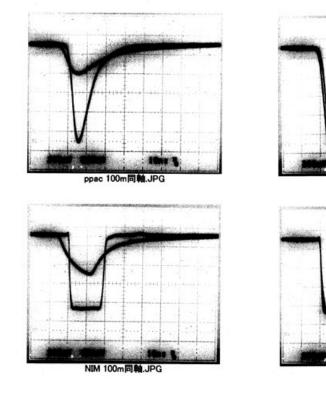

# Analog and NIM logic signal via Single-mode fiber

Metal coax. cable 100m

Optical cable 100m

ppac fiber.JPG

expensive \$2,000 / 1 link end of production (laser and photo-diode)

- NIM module (transmitter/receiver)

- Time jitter is < 5ps

- there are 2 types, analog and NIM logic

- Analog signal version

- AC couple

- NIM logic version

- DC signal can be transmitted

1.5 us Optical cable delay box

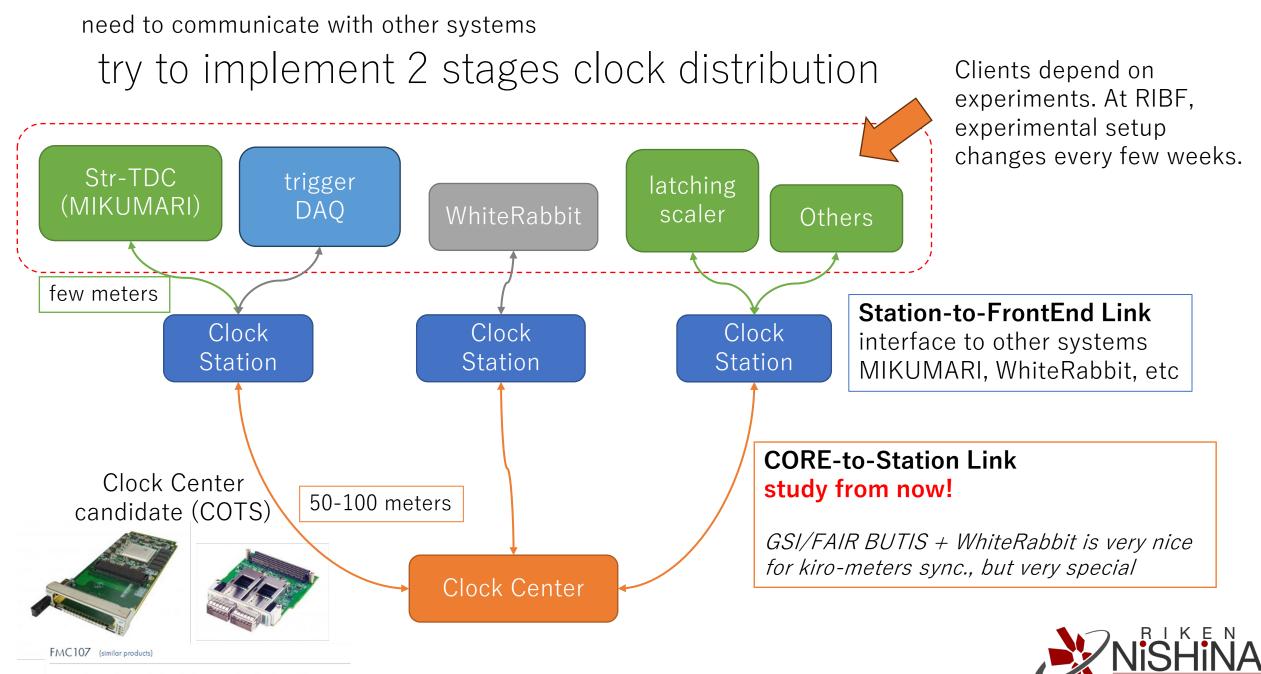

Plan = clock distribution

## Current system

Near future system

FMC Dual QSFP+ for 10 GbE/40GbE/SRIO PCIE/40Gb InfiniBand/AURORA

## Plan for Clock Station

Versatile clock transceiver based on AMD Xilinx Kria

will be delivered March 2024

## many works from now

- How to describe time?

- from EPOCH (1970)? or from arbitrary T0 (time reset)? or 20XX-Jan-01?

- correction of propagation delay change

- to get enough TOF resolution

- MIKUMARI + temperature / phase monitor

- White Rabbit + temperature / phase monitor

- H. Li et al., "Temperature Effect on White Rabbit Timing Link", IEEE TNS 62, 1021 (2015)

- some thoughts

- use single cable + WDM (same as White Rabbit)

- should have the same delay for both TX and RX

- use 2 cables (1 pair)

- 1 pair for clock+data TX/RX

- use 4 cables (2 pairs)

- 1 pair for data link (TX/RX)

- 1 pair is for clock (TX for clock distribution, RX-loop-back for monitor)

- how to implement a phase detector?

- DDMTD (WhiteRabbit)? TDC? simple XOR-based circuit?

always monitor phase changes, and put corrections somehow

# Summary

- Clock distribution

- Under consideration

- for a link layer

- we have MIKUMARI based on CDCM

- there are several candidates

- protocol

- what kind of functionalities do we need?

- we'll play with a Kria-based board

- Other topics

- we have just started some studies on real-time data processing

- HLS with AMD Xilinx Alveo

- HLS+AI with AMD Xilinx Versal-AI

- facility-to-facility fast data link

- 100Gbps IPv6 connection via SINET6 in Japan without firewall

- similar to ESnet6 in US

- will be available from 2025

- study with FPGA-based NIC (from 2024)