# Timing Synchronization System for the ePIC DAQ

J. Schambach

Oak Ridge National Laboratory

ORNL is managed by UT-Battelle LLC for the US Department of Energy

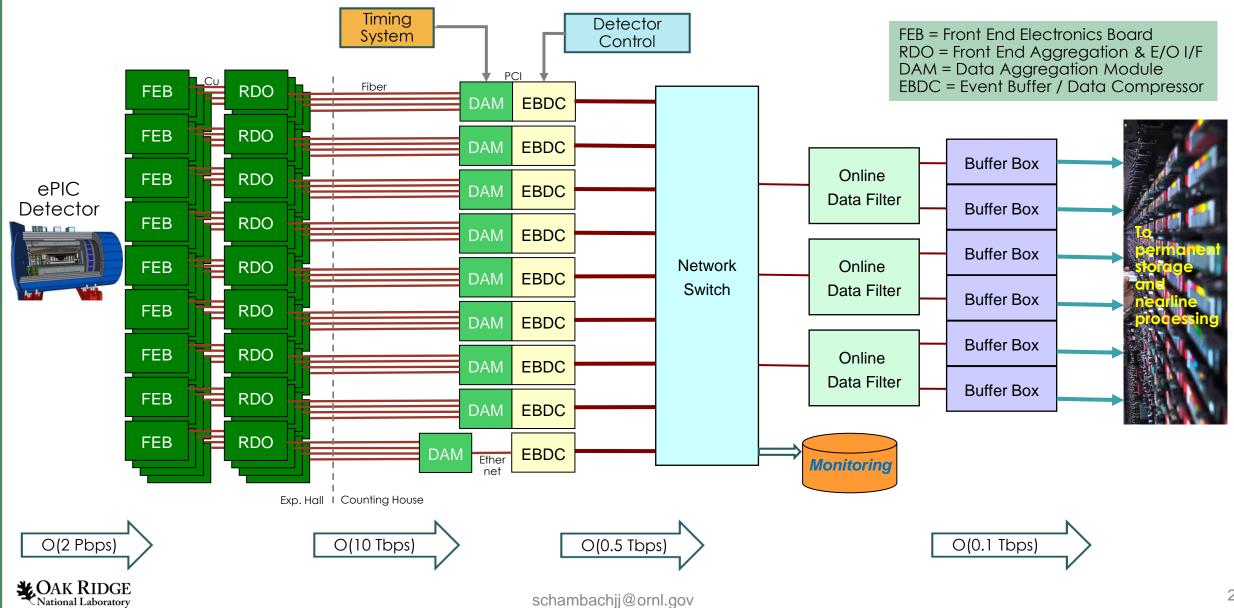

## ePIC Streaming DAQ

2

schambachjj@ornl.gov

# ePIC Timing System

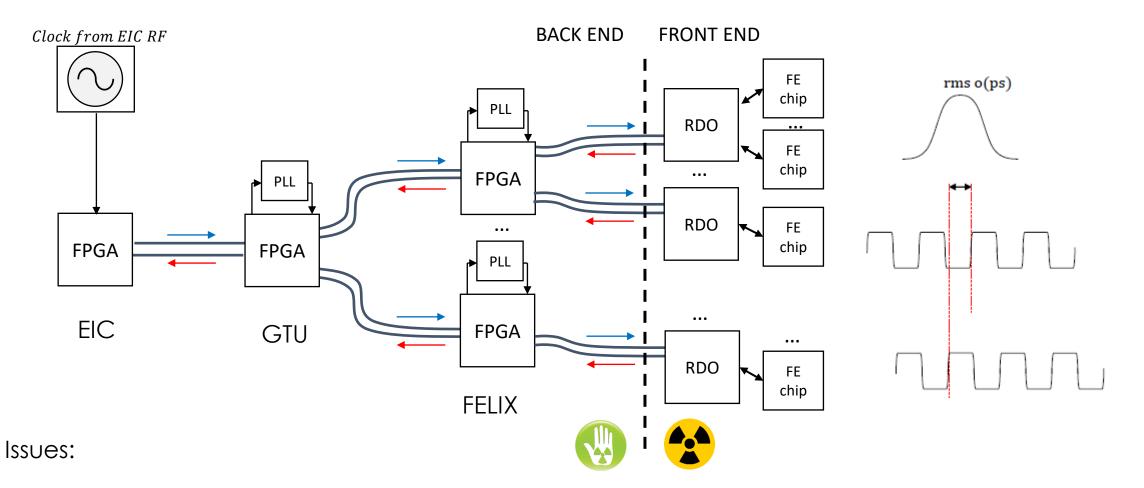

- The 'Global Timing Unit' board receives the accelerator clock plus any beam related information and fans this out via the DAM (FELIX) board

- The RDO boards use the reconstructed clock and the bunch crossing count (BX) from the transmitted data for digitization and synchronization, respectively

- Most detectors will need only a precision O(100ps), while some detectors (e.g. TOF) might need O(5ps)

• Where possible FEE ASICs should use the BX derived clock; where this is not possible, the RDO must provide sufficient information (drift measurements, phase differences, frequency differences) to allow time reporting in reference to the BX clock.

# ePIC Timing System Requirements

- Timing System must synchronize data between detectors. This requires a ~10ns resolution

- 40m far forward and backward: ~135ns to calibrate

- Need capability to set delays and monitor the synchronization

- Absolutely critical if there is any sort of software trigger or filtering of data on one detector using info from another

- Timing System must provide high resolution 20ps phase stability to actual BX persisting over power cycles

- Less than 100ps phase stability relative to EIC clock (possibly < 5ps jitter for TOF)

- Account for transitive loading due to EIC acceleration (species/energy dependent phase correction)

- Ability to set fine delays and monitor the synchronization

- Implies higher resolution O(1ps) required between components

- Timing System is the only source for "real-time" global information

- Rev-Tick (to identify bunch crossing 1 in each revolution)

- 64bit unique bunch crossing ID (equivalent to 6k years, will never roll over in the lifetime of EIC)

- Bunch structure

- Spin State

- Control zero-suppression, feature finding, AI/ML algorithms

- Flow Control (start / stop / common busy)

- Define time frames for packetization of detector data (protocol)

- Fallback for handling hardware trigger for debugging, commissioning, handling specific detector problems (dRICH?)

- FEE clock counter resets

- Possibly interleave with Slow Controls / Configuration data at DAM board level

- All detectors need potentially complex configuration

- Need real-time control for providing features like periodic raw data for checking bias

- Need to monitor, and potentially adjust configuration in real time (pedestal drifts/hot channels/tracking failing electronics)

- Automated power cycle / configuration recovery

- AI/ML control of HV settings (to control gains, timing windows, phase shifts)

# **Timing System Components**

- EIC Accelerator

- 10ns (100MHz) bunch crossing rate

- Interaction rates up to 500kHz

- EIC Clock System

- Provided by the accelerator team

- Interface to GTU board via fiber in the same room

- Global Timing Unit

- Tree of boards splitting timing from EIC to O(100) DAM boards

- Interface to DAM boards via fiber in the same room

- Reads info from EIC clock system

- Reads info from DAQ controls

- User inputs from external systems

- Transmits info to DAM boards

- Possible feedback from DAM boards for flow control

- Support for triggering (via input bits)

- DAM Boards

- Accept and transmit timing info from GTU board set

- Use timing input clock as clock for fiber transceivers

- Use downlink also for detector control

- ~5 10 Gbit/sec transfer speed

- RDOs

- Accept timing protocol

- Clock to FEE boards (ASIC) reconstructed from information stream from DAM boards

- Format Data packets in appropriate time frames

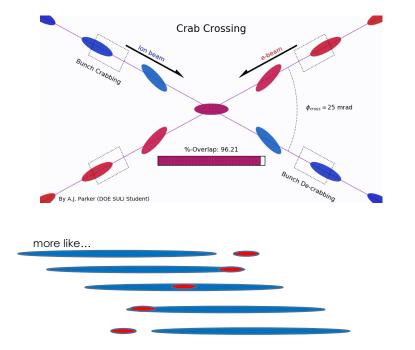

## EIC Beam Parameters (T. Satogata, JLAB/ODU):

- 1160 RF bunches, 98.5254 MHz beam crossing clock, 1015 ns gap (100 "no" bunches)

- Clock originating from accelerator RF source, routed through the accelerator site to experiment

- Clock has fixed frequency, without ramp variation

- Bunch spacing 10.150 ns

- Revolution period  $T_{rev} = 12.7886 \,\mu s$ , dominated by electrons

- Ion energies constrained to match  $T_{rev}$ , change orbit to match electron beam frequency

|                                     | ESR       | HSR           |

|-------------------------------------|-----------|---------------|

| RMS bunch length $\sigma_z$ [mm/ps] | 7-9/23-30 | 75-60/250-200 |

| RMS momentum spread [10-4]          | 5.8-10.9  | 10.3-6.8      |

| RMS horiz beam size $\sigma_x$ [um] | 100-250   |               |

| $\sigma_z/\sigma_x$ ratio [-]       | 28-90     | 240-750       |

# **Timing Distribution Concept**

- Jitter

- Wander slow phase variations (temperature, power supply stability,...)

- Phase-determinism with resets

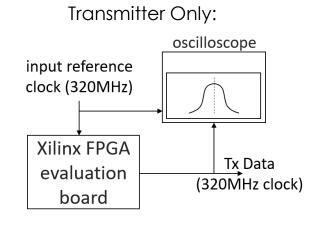

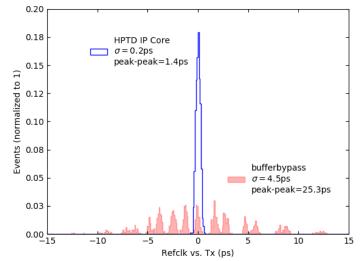

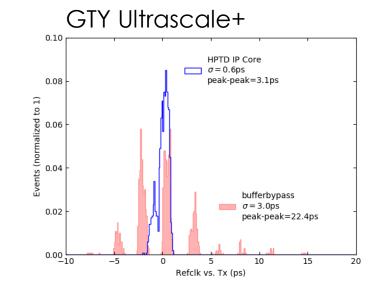

# Back-end COTS and CERN HPTD IP

- CERN started an R&D program to study the timing performance of the different components in a timing distribution system (FPGA, PLLs, LDO, ...):

- <u>H</u>igh <u>P</u>erformance <u>T</u>iming <u>D</u>istribution (HPTD) project

- Higher Phase-determinism for Xilinx Ultrascale FPGA Transmitters

Some results can be found here and IEEE TNS

#### GTH Ultrascale+

#### CAK RIDGE

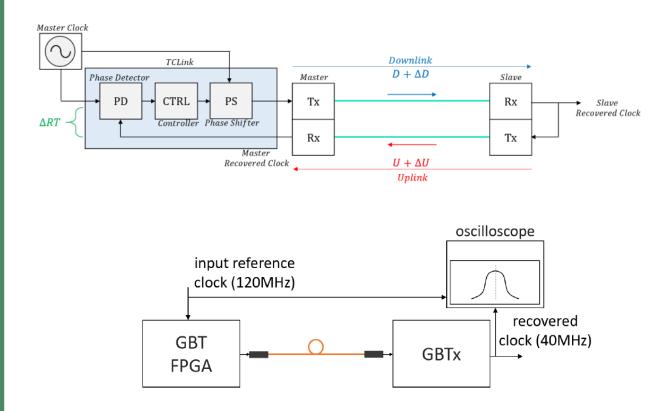

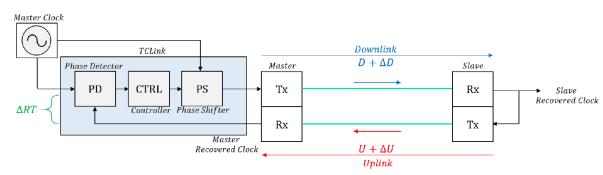

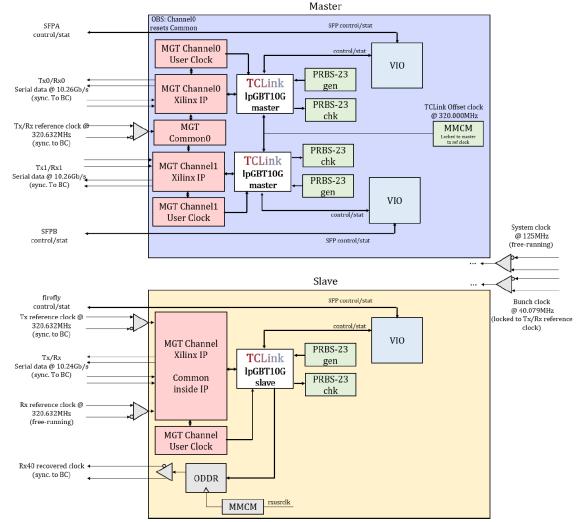

# <u>Timing</u> <u>Compensated</u> <u>Link</u> (TCLink) with GBTx

- CERN developped an FPGA-IP to implement timing monitoring and compensation in FPGA-based links

- Protocol-agnostic

- Presented in <u>TWEPP-19</u>

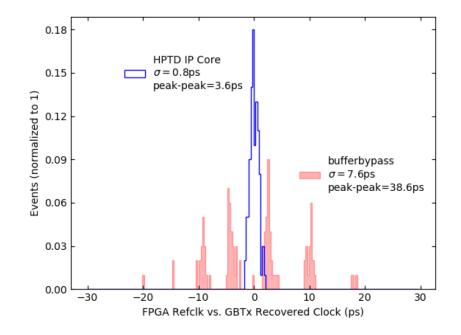

Fig. 8. Transmitter phase results for GTH Ultrascale-system tests with GBTx ASIC. Total number of events is 100.

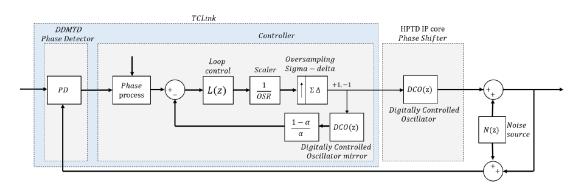

## From the (HPTD) TCLink Reference Note:

- Phase-detector: The phase-detector used is the Digital Dual Mixer Time Difference (DDMTD) core created in the CERN White-Rabbit project (https://ohwr.org/project/white-rabbit). The DDMTD relies on a heterodyne mixing in order to perform a phase-measurement. Therefore, a third clock with a small frequency offset is necessary for the phase-measurement, it is recommended to use a clock from an external PLL for the mixing clock (the example design uses an internal MMCM for those purposes to ease the usage for a first approach with the core). It can have a resolution of o(ps).

- **Controller:** Digital controller using sigma-delta modulation and capable of mirrorring the control plant in order to emulate different  $\alpha$  coefficients.

- **Phase-shifter:** The phase-shifter used is the **HPTD IP** core created by the **CERN HPTD** project (https://gitlab.cern.ch/HPTD/tx\_phase\_aligner). It can have a resolution of o(ps).

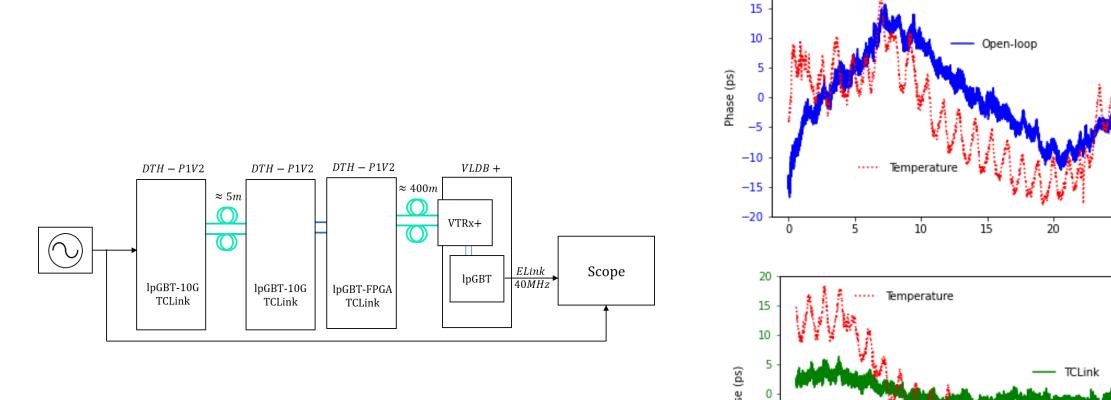

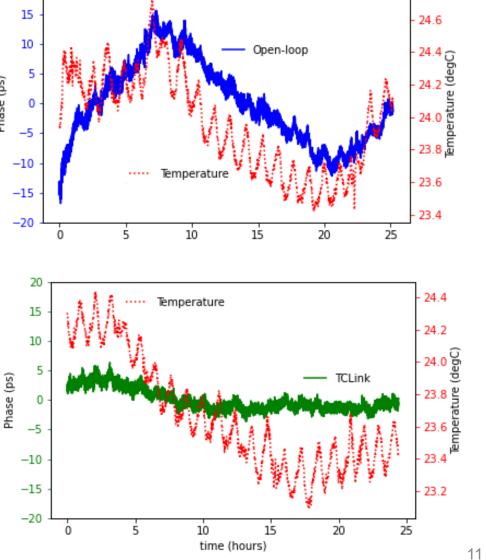

#### **TCLink Performance for cascaded links**

24.8

20

schambachjj@ornl.gov

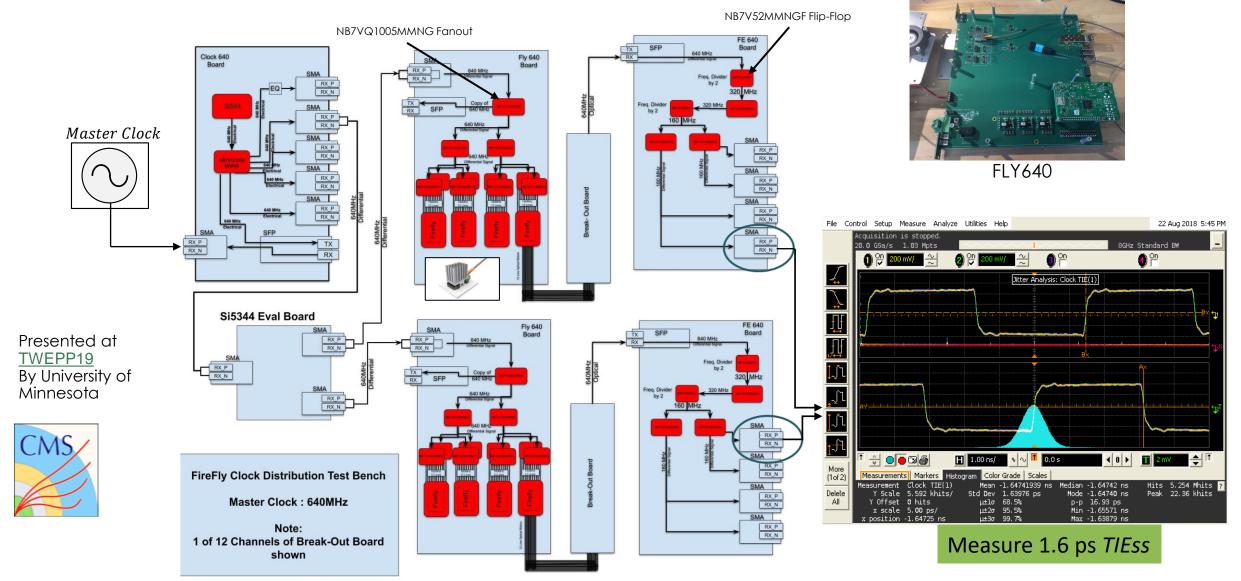

#### Alternative: Pure Timing Distribution Example

CAK RIDGE

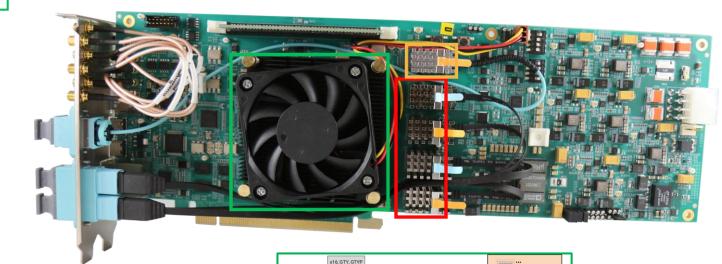

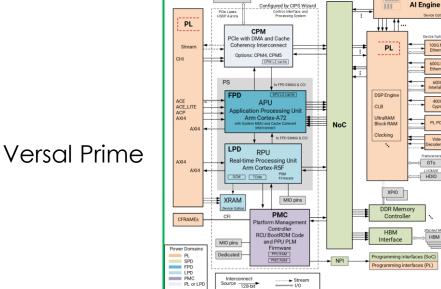

# ePIC DAM: ATLAS FELIX Phase II Run 4 hardware

#### Based on Xilinx Versal Prime VM1802

- Dual-core ARM Cortex-A72 Application Processing Unit

- Dual-core ARM Cortex-R5F Real-Time Processing Unit

- Al Engine

- Programmable Logic

- Future: Versal Premium

- 4 Samtec FireFly transceivers

- 24 bi-directional optical links (future: 48 links)

- 10 / 25 Gbps bandwidth per channel

- 1 Samtec FireFly for LTI/TTC link

- Trigger, Timing and Control (4 links)

- 100 GbE Networking

- PCIe Gen4 x16 (240Gbps)

- 2 x8 lanes bifurcated

- Future: PCIe Gen5 up to 16 lanes

#### BNL FLX-182 Prototype

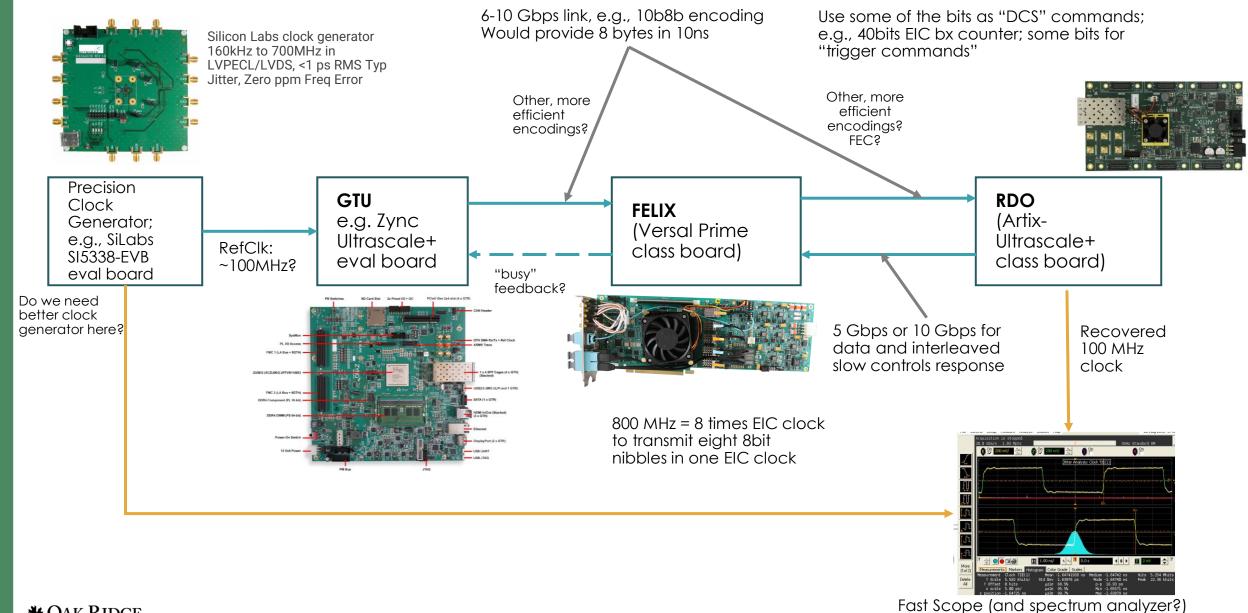

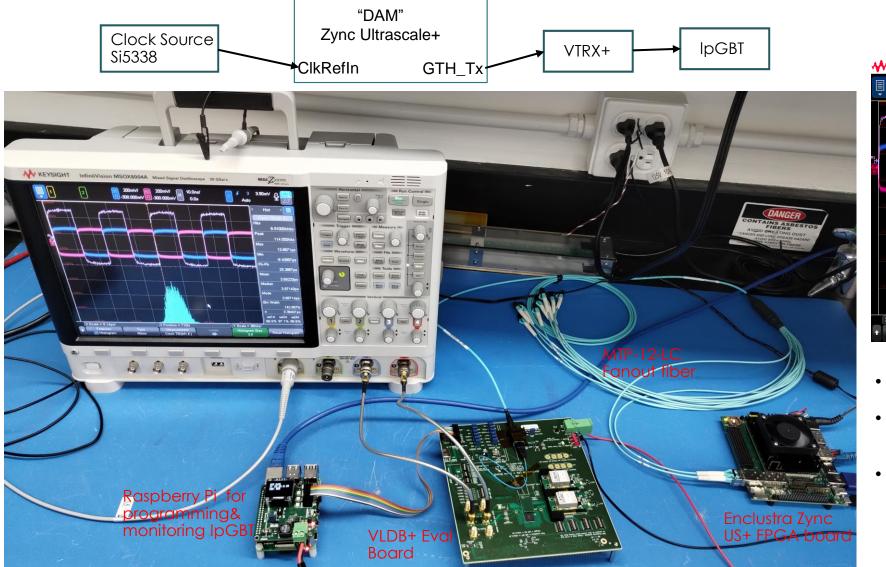

## ePIC Timing Test Setup Proposals

CAK RIDGE

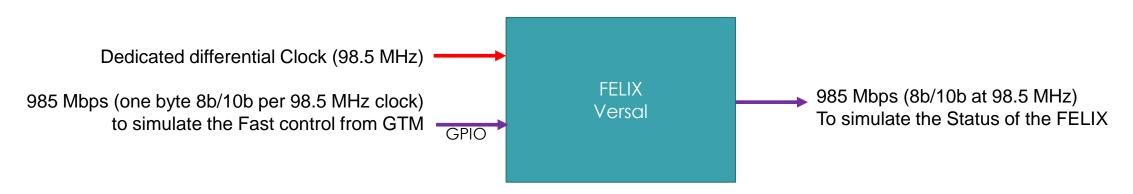

## First ePIC Timing Tests (W. Gu, Jefferson Lab)

# First Results (W. Gu, Jefferson Lab):

- Downlink Custom Protocol:

- Eight bytes (8b10b) payload per Clock (98.5 MHz)

- 7.88 Gbps line rate (6.304 Gbps payload rate)

- Clock embedded transmission via GTH transmitter

- GTY Clock recovery works OK

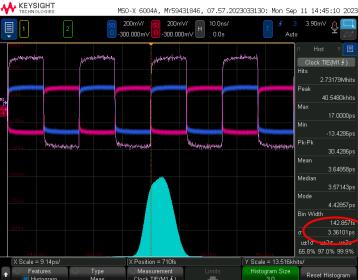

- The TIE ( $\sigma$ ) is below **4ps**

####

7.88 Gbps line rate

Eight 8b/10b payload per clock (98.5 MHz) equivalent (downlink) control words: 6.304 Gbps Control symbols as frame delimiters, BC markers, and IDLEs

- Phase is stable, recovered clock reproduces the original (GTH\_Ref) Clock

- A Clock Jitter Cleaner further improves recovered clock with a TIE ( $\sigma$ ) below 2ps

- Future Tests: Use (Versal based) FELIX prototype

# First ePIC Test with IpGBT / VTRx+ based Timing Distribution

- RefClk in: 315.27 MHz (ElC x 2 / 5)

- Phase Adjustable Clock output from IpGBT: 39.4MHz

- TIE: **3.36ps**

#### **Next Steps**

- Initial tests show that jitter for an embedded clock distribution via custom protocol or IpGBT protocol with either FPGA transceiver-based clock recovery or clock recovery in the IpGBT chip achieves the necessary jitter performance

- We need to investigate the phase determinism over power cycles

- We need to investigate the phase drift vs environmental parameters

- Investigate if the TCLink and HPTD IP methods work in the Versal FPGA considered for the FELIX

- Investigate "direct" clock distribution in a separate link with fan-out, need for jitter cleaning, ....

- Develop ePIC timing and DCS protocol (in addition to Data protocol)

- Test setups with "realistic" RDO prototypes (using ARTIX FPGA) interfaced to ASICs considered

- Test Cascaded setups (GTU -> FELIX -> RU)