# pfRICH Work Packages

#### **Engineering design oversight**

A. Eslinger (JLab)

**Vessel & mirrors: 3D printing & molding**

A. Jung (Purdue)

**Vessel: other components & assembly**

J. Datta (Stony Brook)

Mirrors: aluminum coating & QA

W. Li (Stony Brook)

**Construction coordination**

C.-J. Naim (Stony Brook), Z. Tu (BNL)

#### **HRPPD QA station**

P. Garg (Yale)

**HRPPD** test stand

A. Kiselev (BNL)

**Aerogel QA station**

M. Posik (Temple)

**MCP-PMT** test stand

R. Montgomery (Glasgow)

#### **Standalone GEANT software & modeling**

A. Kiselev (BNL)

Software support in ePIC framework

BNL NPPS group [K. Kauder]

#### **Physics modeling**

B. Page (BNL)

**DAQ** software & firmware

. . .

#### Gas system

P. Shanmuganathan (BNL)

**HV & LV systems**

T. Camarda (BNL)

#### **Cooling system**

...

#### **Light monitoring system**

F. Barbosa (Jlab)

#### **Frontend electronics**

. . .

### pfRICH is a baseline ePIC detector

### **Electron-Ion Collider Record of Decision**

| TITLE                                           | pfRICH for backward PID in ePIC                |

|-------------------------------------------------|------------------------------------------------|

| PREPARER                                        | Beni Zihlmann                                  |

| NUMBER (Supplied by SEG)                        | EIC-ROD-011                                    |

| DATE                                            | August 7, 2023                                 |

| AFFECTED WBS/PROJECT AREA                       | 06.10.04.03 mRICH/pfRICH, 06.10.08 Electronics |

| STATEMENT OF DECISION (Summary, 1-2 sentences): |                                                |

The request by the ePIC collaboration to switch from mRICH to pfRICH as solution for the backward PID is found to have minimal impact on cost and schedule for the project.

This essentially completes the mRICH -> pfRICH transition process

### HRPPD FEE update

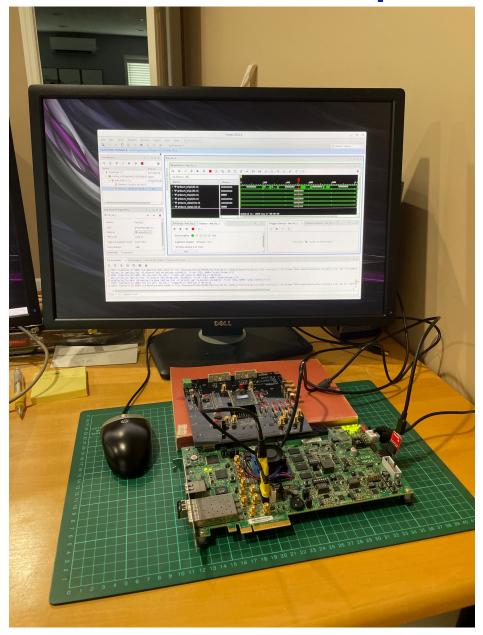

- > A small HGCROC3 installation at BNL

- Essentially a Linux-based copy of Oak Ridge setup

- KCU105 FPGA kit provided by John Kuczewski (BNL)

- Carrier board by Norbert Novitzky (ORNL)

- ➤ HGCROC3 mezzanine board by Damien Thienpont (IN2P3)

- FPGA firmware by Miklos Zeller (Debrecen)

- ➤ Should be sufficient for writing an RCDAQ driver

- First via USB, then gigabit ethernet

- Only partially functional so far

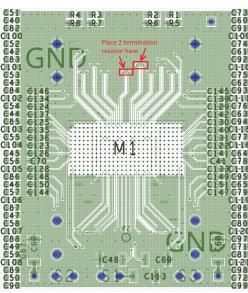

- > Issues with on-board termination

- Making use of John's expertise ...

- ... and practical advice by Norbert & Miklos

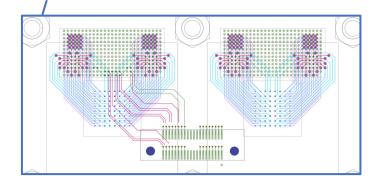

# HRPPD FEE update

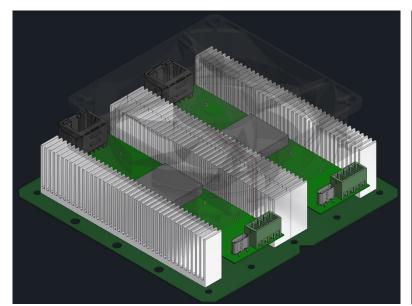

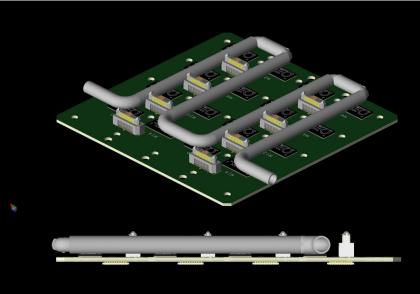

3D integration and cooling options by G. Nagy (Debrecen) and D. Cacace (BNL)

ASIC backplane design by P. Dinaucourt (IN2P3)

FRONT END BOARD 16 x BGA HGCROC HD 350 0.6mm

## pfRICH geometry update in GEANT

- Verified the latest vessel boundary conditions in ePIC geometry

- > Expansion volume got shorter by ~50mm

- Incorporated 3.8 mm thick sapphire window

- Used to be 5.0 mm thick fused silica

- > So far only chemical composition, density and RINDEX parameterization

- ➤ Incorporated a Belle II like aerogel with <n> ~ 1.040

- ➤ Used to be <n> ~ 1.045 (Belle II low refractive index aerogel)

- ➤ A linear extrapolation of RINDEX, ABSLENGTH, RAYLEIGH of <n> ~ 1.045 and <n> ~ 1.055 species

All in all, we are getting a similar performance as before