ePIC Collaboration Meeting - Jan 2024 (ANL)

#### Module Block Diagram

Manoj Jadhav Argonne National Laboratory

Jan 10, 2024

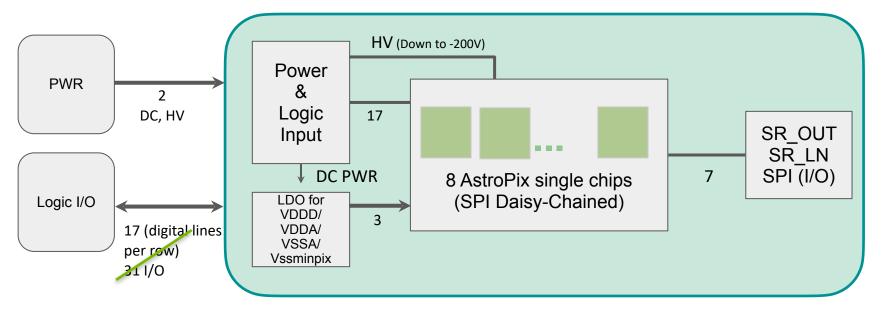

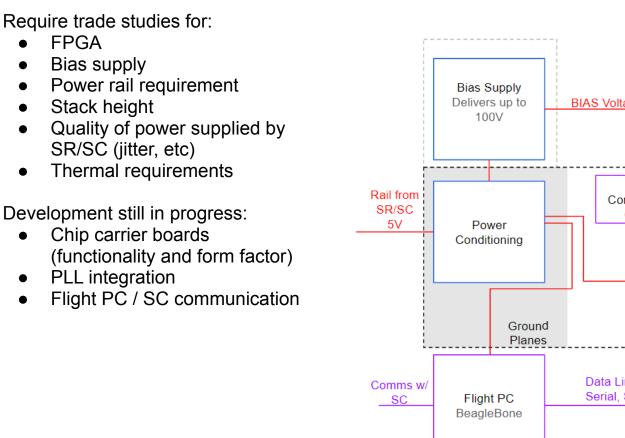

# **Block Diagram**

- 1. 8 chips are all daisy chained via SPI

- 2. WB connections through flex bus tape

- DC power -> VDDA/VDDD (1.8V), VSSA (1.2V), Vssminpix (0.7V), HV -> Do we want seprate out digital and analog?

- LDOs for DC power -> On module pcb or flex bus tape?

- SR\_OUT, SR\_LN, SPI\_XXX -> 5 SPI lines, Interrupt, 200 MHz Time-over Threshold (ToT) clock

- Each AstroPix quad-chip carrier board connector has a total of 17 digital lines which result in 31 I/Os at the FPGA after considering shared interface lines.

We don't need any digital I/O for the actual project -> only 5 SPI lines (interrupt is optional), 200 MHz is on chip in 2

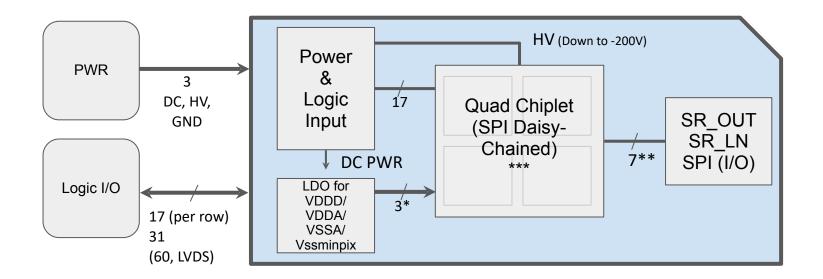

# **Block Diagram**

- DC power -> VDDA/VDDD (1.8V), VSSA (1.2V), Vssminpix (0.7V), HV -> Do we want seprate out digital and analog?

- LDOs for DC power -> On module pcb or flex bus tape?

- SR\_OUT, SR\_LN, SPI\_XXX -> 5 SPI lines, Interrupt, 200 MHz Time-over Threshold (ToT) clock

- Each AstroPix quad-chip carrier board connector has a total of 17 digital lines which result in 31 I/Os at the FPGA after considering shared interface lines.

We don't need any digital I/O for the actual project -> only 5 SPI lines (interrupt is optional), 200 MHz is on chip in V4 (differential)

Where power is coming from -> project provides power (The main power supplies in the experiment are in racks on a platform (South) and are about 20 m away. These are floating, low noise supplies, ground referenced at the detector.) These supplies have sense inputs that are wired all the way to the point of use and so compensates automatically for cable losses.

The potentials at the point of use are thus what you set/need.

Space on end-of-stave card -> we don't know 13-14 cm z-direction Magnetic field -> 2T max DC-to-DC converter

### Thank you

# **Block Diagram**

\*VDDA/VDDD (1.8V)/VSSA (1.2V)/Vssminpix (0.7V) \*\* SR\_OUT, SR\_LN, SPI\_XXX

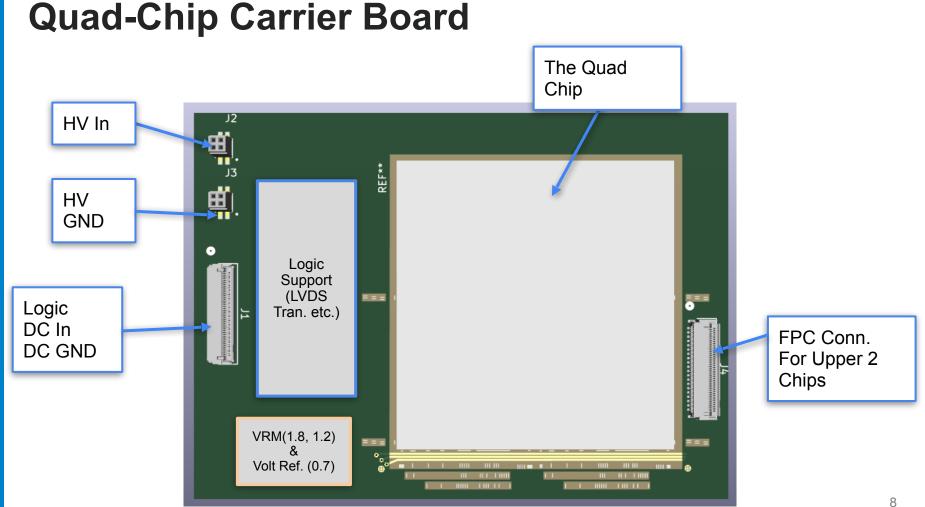

- 1. Assumed 4 chips are all daisy chained via SPI

- 2. Upper 2 chip WB connections through flex bus tape

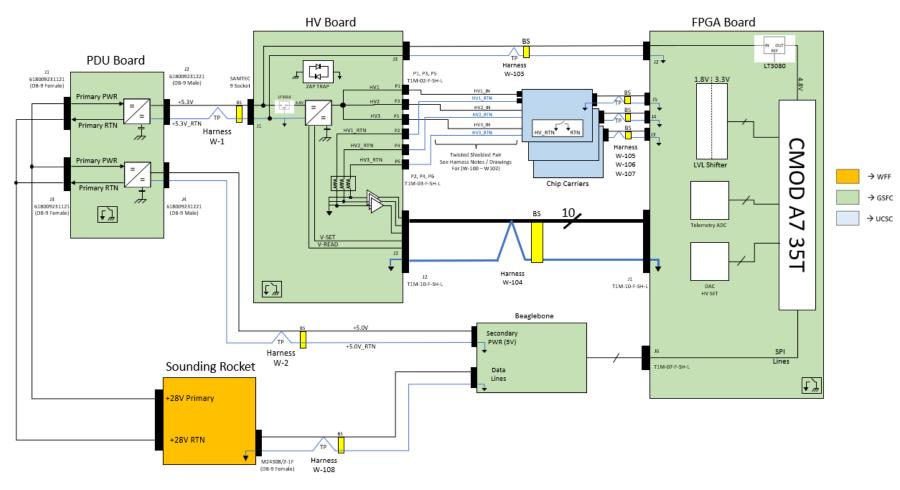

# **Block Diagram A-Step**

•

•

•

•

•

•

•

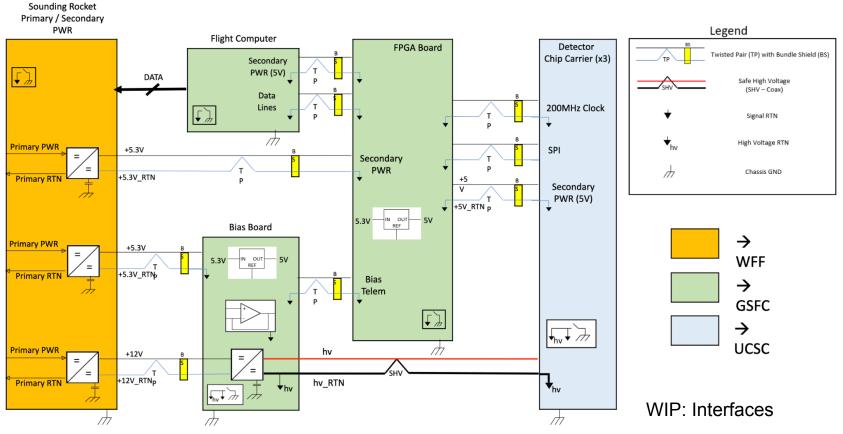

Stack depth = 3cm 7.4 cm 5.4 cm Quad Chip х3 BIAS Voltage Other Components (PLLs) FPGA Artix-7 on Cmod A7 board Data Line: USB Serial, SPI

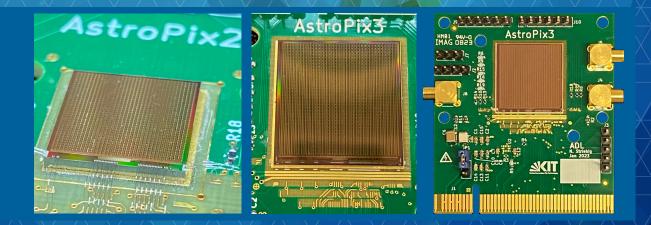

## **Quad-Chip Carrier Board**

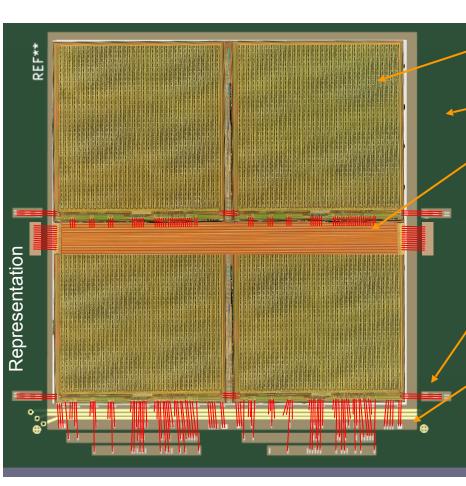

The Quad Chip (mounting representation)

Chip Carrier PCB

AstroPix V3 quad-chip

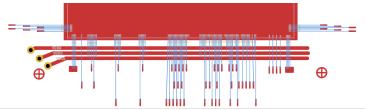

Flex bus tape glued on the top of quad chip (allows wire-bond connection to top row chip pads) Glue Recommendations: <u>SE4445-CV</u> or <u>ARALDITE 2011</u>

Daisy-chained SPI bus

Wire-bond pads

'iх

Wire-bond plan for V3 single chip

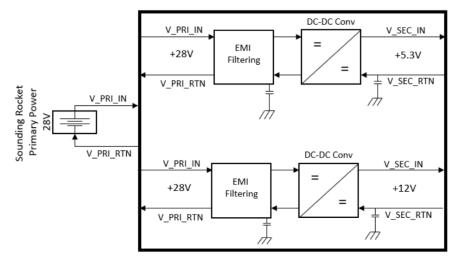

# **Grounding Configuration for Power Board**

### **Power Boards**

- Primary Power (28V) provided by sounding rocket.

- Will provide +5.3V and +12V for the instrument

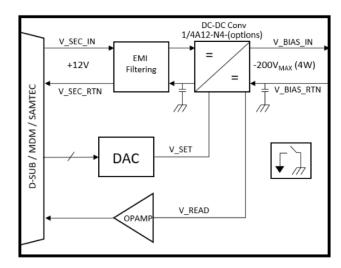

- Detector Bias Board

- Bias needs: -150V to -175V

- Max current draw is 3mA, 525mW per detector

#### **Power Boards**