# Data Acquisition in ASIC testing

Piotr Maj on behalf of ASIC group

Date 10/19/2023

# Data Acquisition

For ASIC testing

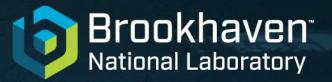

### **DAQ System Overview**

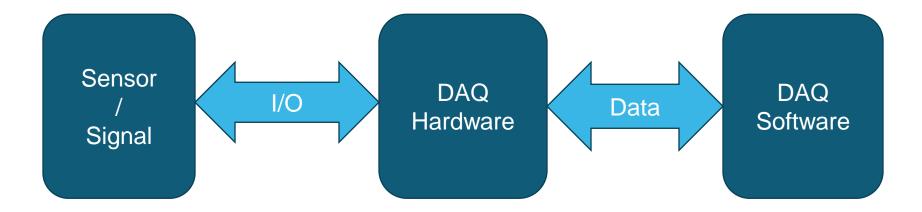

#### **Data Acquisition (DAQ)**

the automatic collection of data from sensors, instruments, and devices in a factory, laboratory, or in the field.

#### Purpose

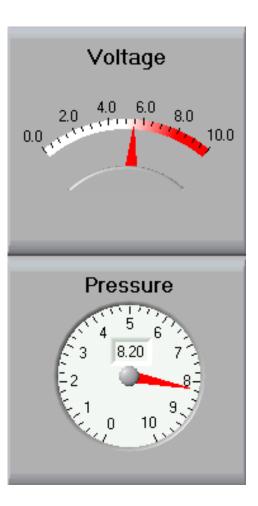

To measure an electrical or physical phenomenon such as voltage, current, temperature, pressure, or sound

### **DAQ System Overview**

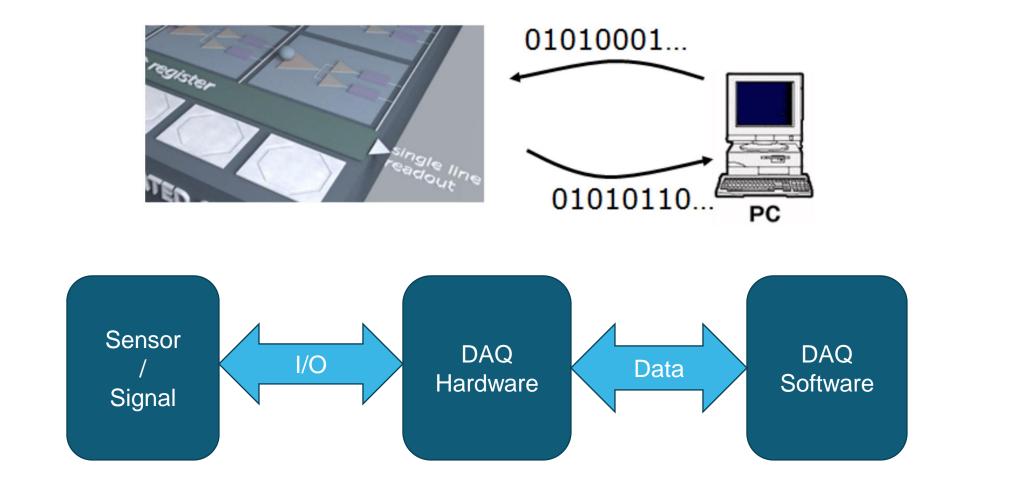

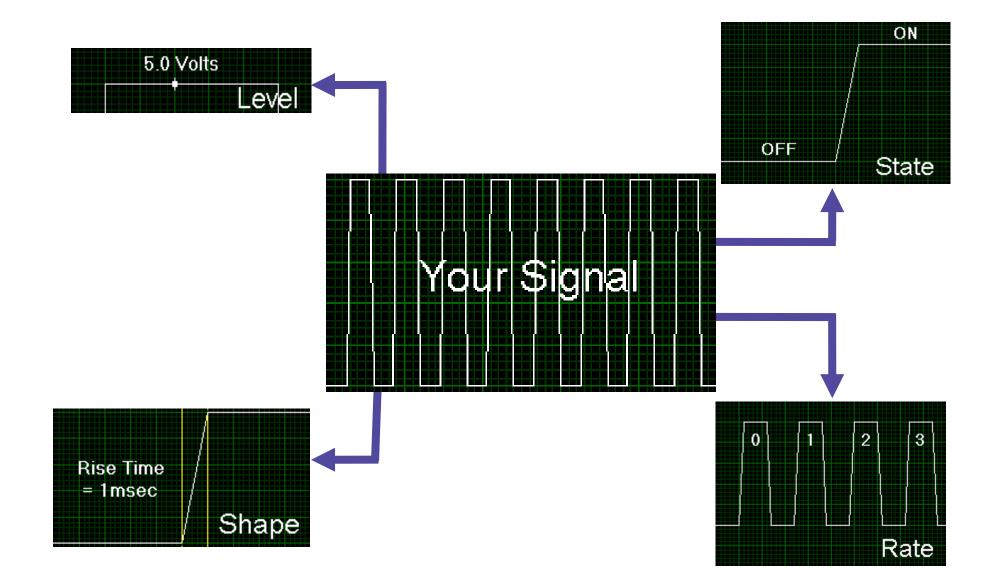

#### **Signal Classification**

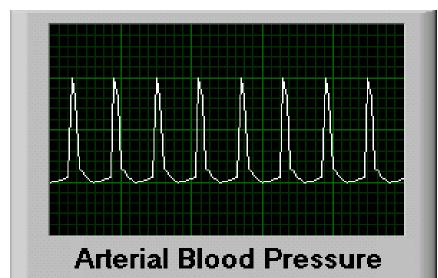

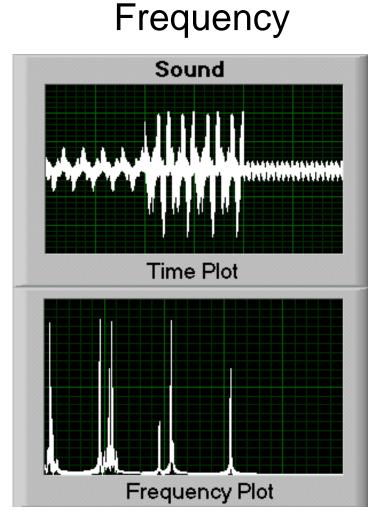

### **Analog Signals**

- Continuous signal

- Can be at any value with respect to time

- Three types of information

- Level

- Shape

- Frequency

Analog

### **Analog Signals**

level

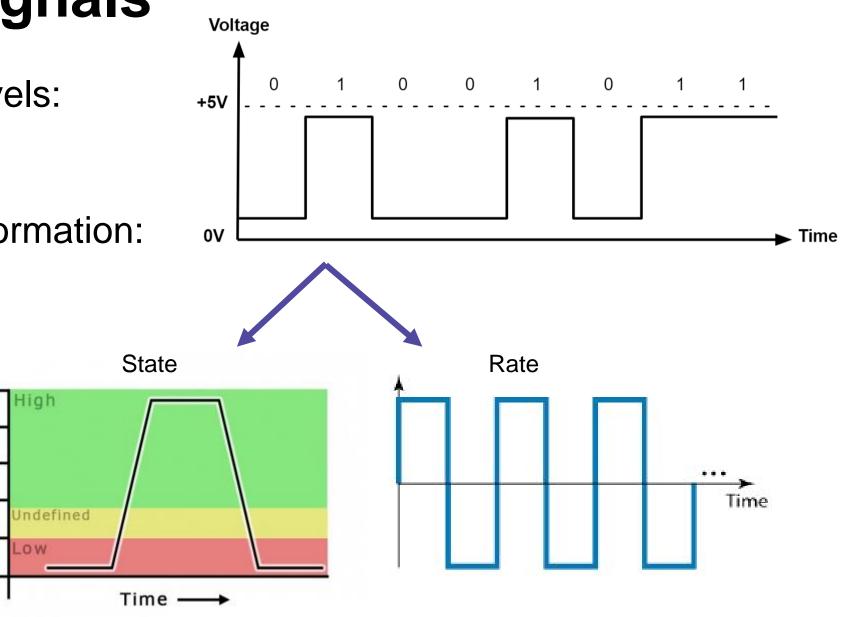

### **Digital Signals**

Two possible levels:

- High/On

- Low/Off

Two types of information:

Signal Level (Volts)

4

3

2

1

0

- State

- Rate

#### **5 Ways to Measure the Same Signal**

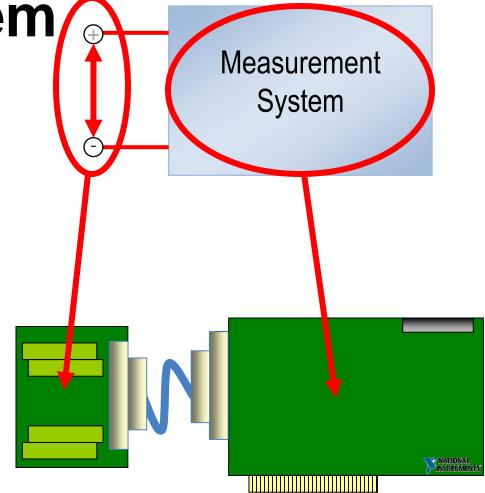

### **DAQ Hardware Overview**

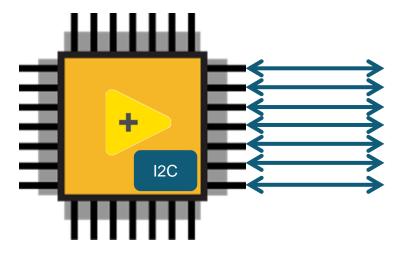

#### • DAQ hardware

- Can acquire and generate analog and digital signals

- Transfers signals to and from DAQ software through a bus (e.g. PCIe, USB)

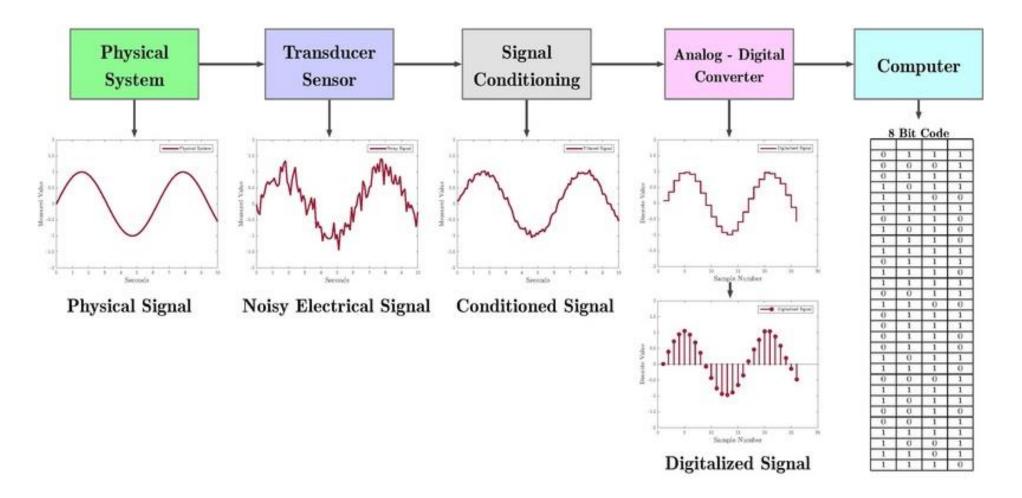

#### **Data Acquisition Hardware**

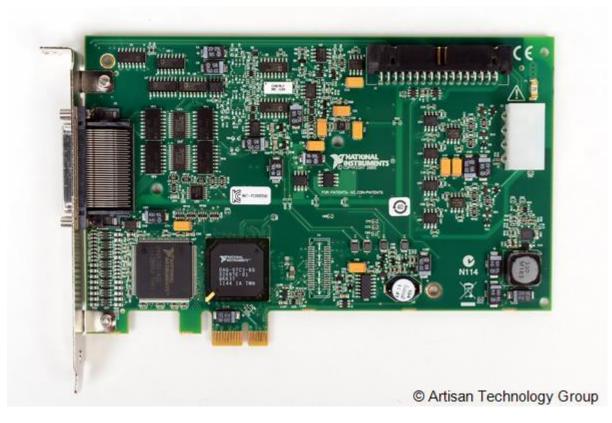

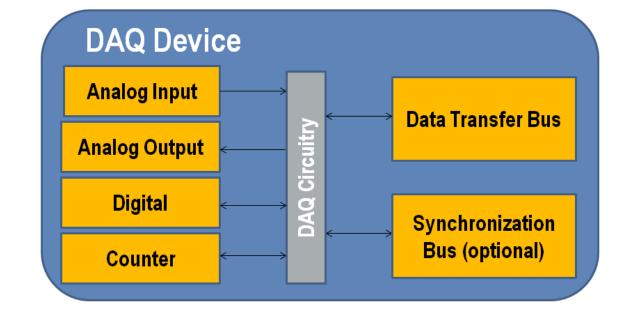

### **DAQ Device**

#### st DAQ devices have:

- Analog Input

- Analog Output

- Digital I/O

- Counters

Specialty devices exist for specific applications

- High speed digital I/O

- High speed waveform generation

- Dynamic Signal Acquisition (vibration, sonar)

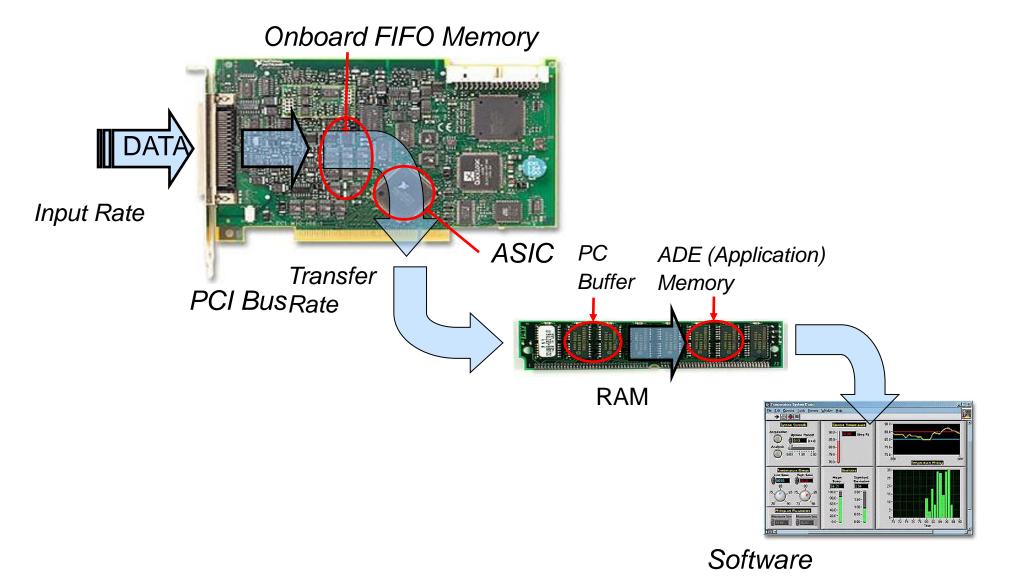

### **B.** Components of a DAQ Device

- Data Transfer Bus

- Connects the DAQ device to the computer

- Can be a variety of bus structures

- USB, PCI Express,

- Synchronization Bus

- Used to synchronize multiple DAQ devices

• Allows sharing of timing and trigger signals between devices

### C. Choosing Appropriate DAQ Hardware

- Bus Considerations

- Signal Considerations

- Accuracy Considerations

### **Bus Considerations**

- How much data will I be streaming across this bus?

- Bus bandwidth

- What are my single-point I/O requirements?

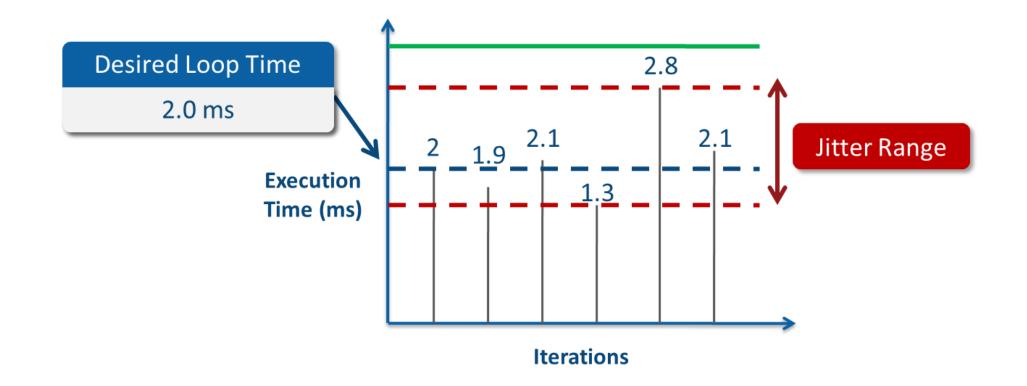

- Bus latency and determinism

- Do I need to synchronize multiple devices?

- Bus synchronization options

- How portable should this system be?

- How far will my measurements be from my computer?

### **Signal Considerations**

- How many channels?

- Choose DAQ device(s) with enough channels

- How quickly do you need to acquire/generate samples of the signal?

- Choose DAQ device with fast enough sampling rate

- What are the expected minimum and maximum measurements?

- Choose DAQ device with appropriate range

- What is the smallest change in your signal that you need to detect?

- Choose DAQ device with a small enough code width

- To calculate the code width, you must know:

- Resolution

- Device input range

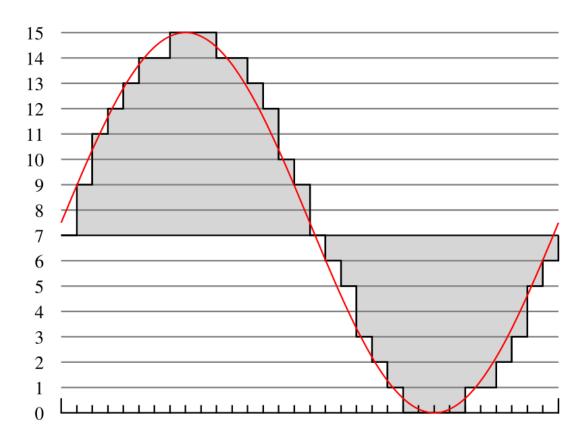

# Calculating Code Width – Resolution Example

- 4-bit resolution can represent 16 voltage levels

- 16-bit resolution can represent 65,536 voltage levels

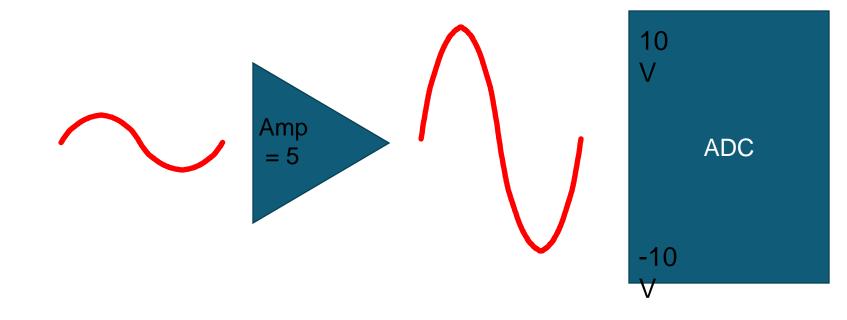

# Calculating Code Width – Amplification and Device Input Range

DAQ devices have a built-in amplifier

- Amplifies the signal to better fit the range of the ADC

- Better utilizes the ADC resolution

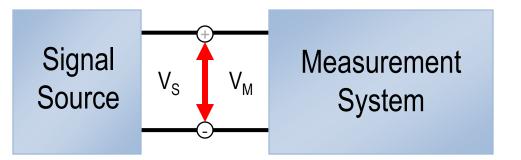

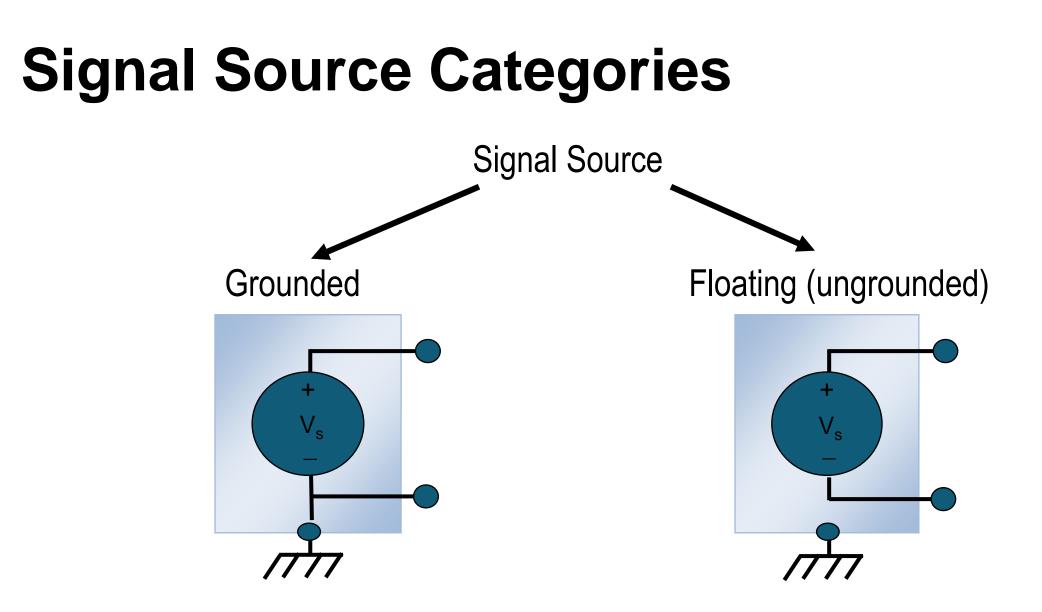

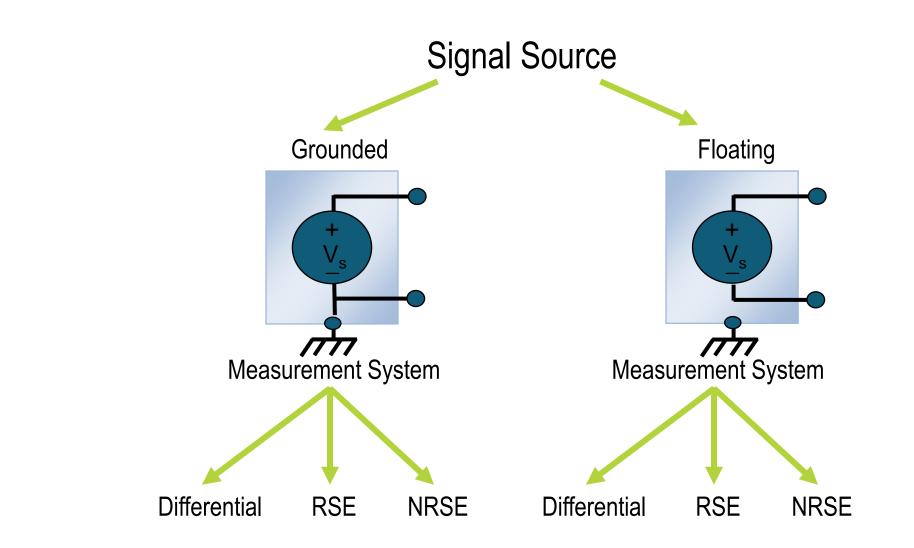

### **Grounding Issues**

- To get correct analog input measurements, you must properly ground your system

- How the signal is grounded affects how you should ground the instrumentation amplifier on the DAQ device

- Steps to proper grounding of your system:

- 1. Determine how your signal is grounded

- 2. Choose a grounding mode for your Measurement System

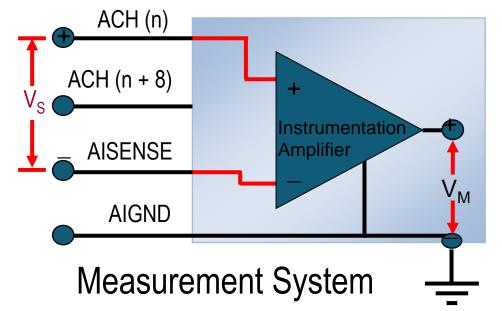

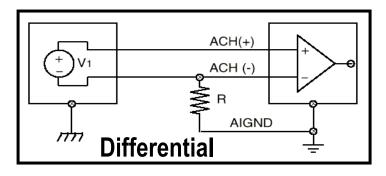

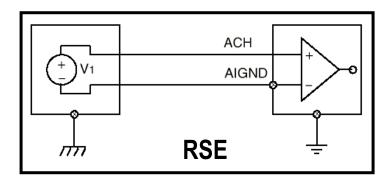

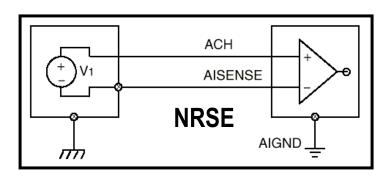

### Measurement System

- Three modes of grounding for your Measurement System

- Differential

- Referenced Single-Ended (RSE)

- Non-Referenced Single-Ended (NRSE)

- Mode you choose will depend on how your signal is grounded

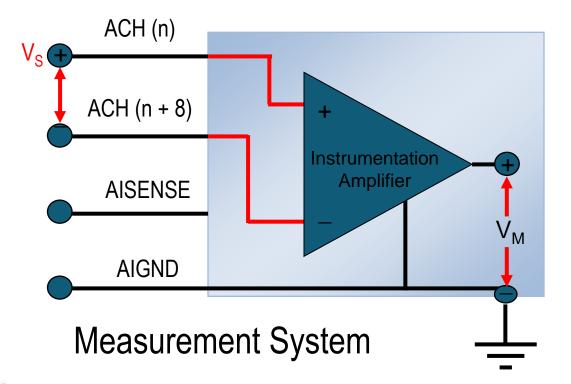

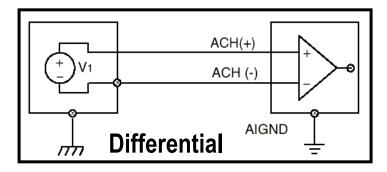

#### **Differential Mode**

- Two channels used for each signal

- Rejects common-mode voltage and common-mode noise

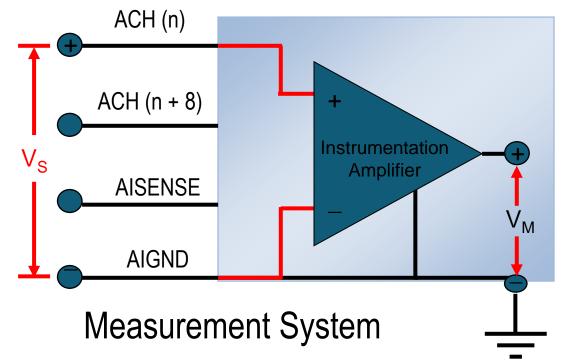

### **Referenced Single-Ended (RSE) Mode**

- Measurement made with respect to system ground

- One channel used for each signal

- Does not reject common mode voltage

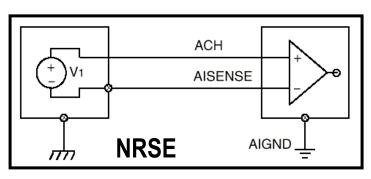

#### Non-Referenced Single-Ended (NRSE) Mode

- One channel used for each signal

- Measurement made with respect to AISENSE not system ground

- AISENSE is floating

#### **Choosing Your Measurement System**

### **Options for Grounded Signal Sources**

#### Better

+ Rejects common-mode voltage

- Cuts channel count in half

#### **Not Recommended**

Voltage difference (Vg) between the two grounds makes a ground loop that could damage the device

#### Good

- + Allows use of entire channel count

- Does not reject common-mode voltage

#### **Options for Floating Signal Sources**

#### Best

- + Rejects common-mode voltage

- Cuts channel count in half

- Needs bias resistors

#### Better

- + Allows use of entire channel count

- + Do not need bias resistors

- Does not reject common-mode voltage

#### Good

- + Allows use of entire channel count

- Needs bias resistors

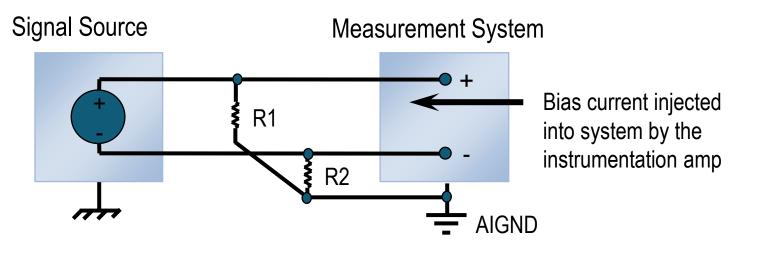

#### **Bias Resistors**

- Needed with floating signal source and floating measurement system (Differential or NRSE)

- Bias resistors provide a return path to ground for instrumentation amplifier bias currents

- Recommended value is between 10 k $\Omega$  and 100 k $\Omega$

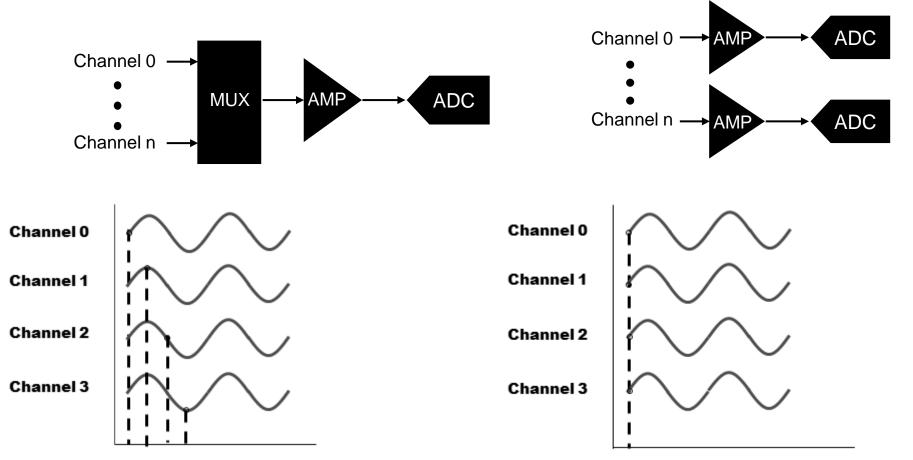

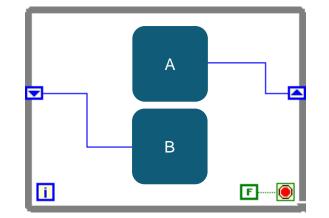

#### **Parallel sampling**

- Used when time relationship between signals is important

- to synchronize the taking of samples

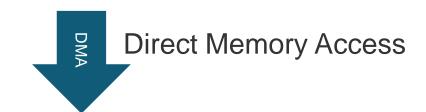

#### **Data Transfer for an Input Operation**

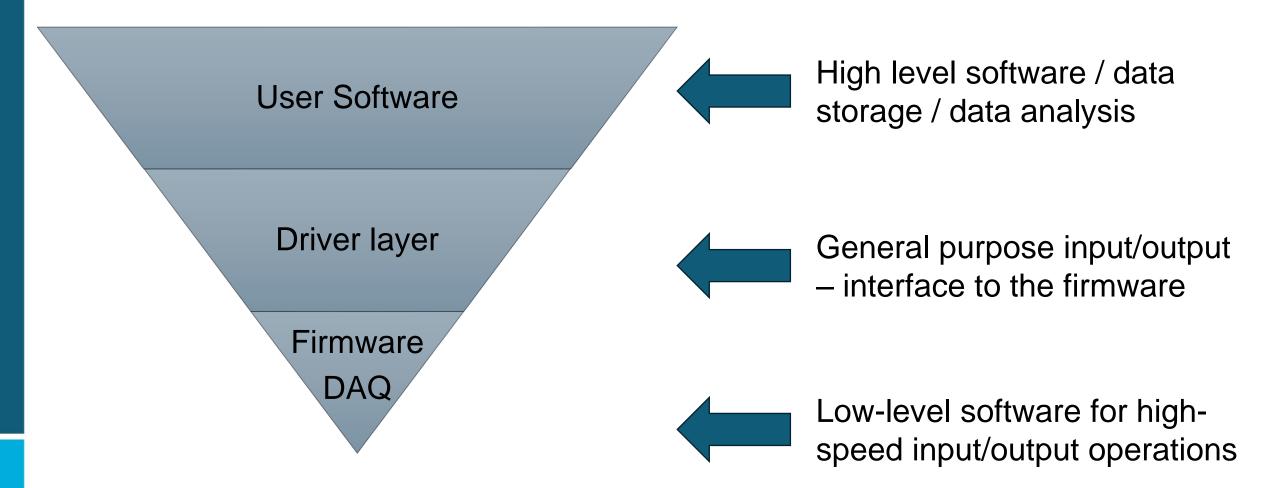

## Software for DAQ

Short introduction to graphical programming

#### **Software Architecture**

#### **High-level software**

#### Data acquisition

Instrument control

Offline analysis

Data presentation

Data Storage

Ethernet Sync.

Extensible functionality

Classical design patterns

#### LabVIEW for DAQ

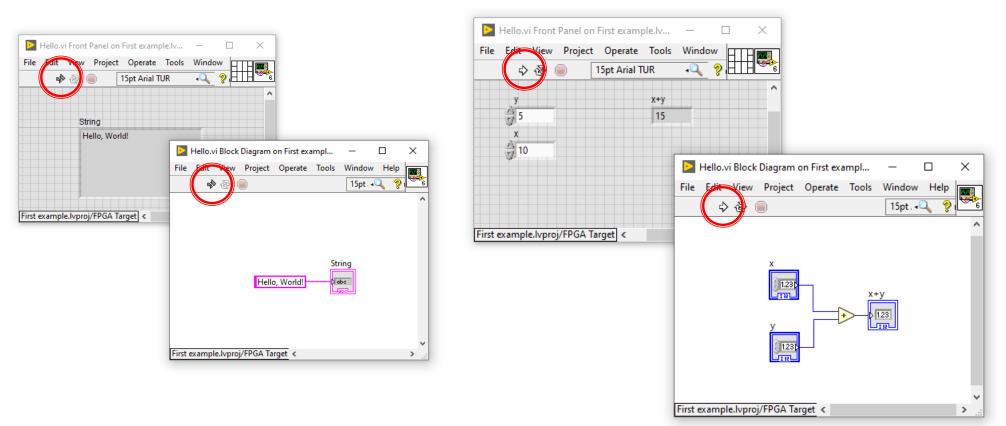

**DEMO 1 – Pr**ogram Structure

#### **DEMO 2 – Data Acquisition**

**DEMO 3 – State Machine**

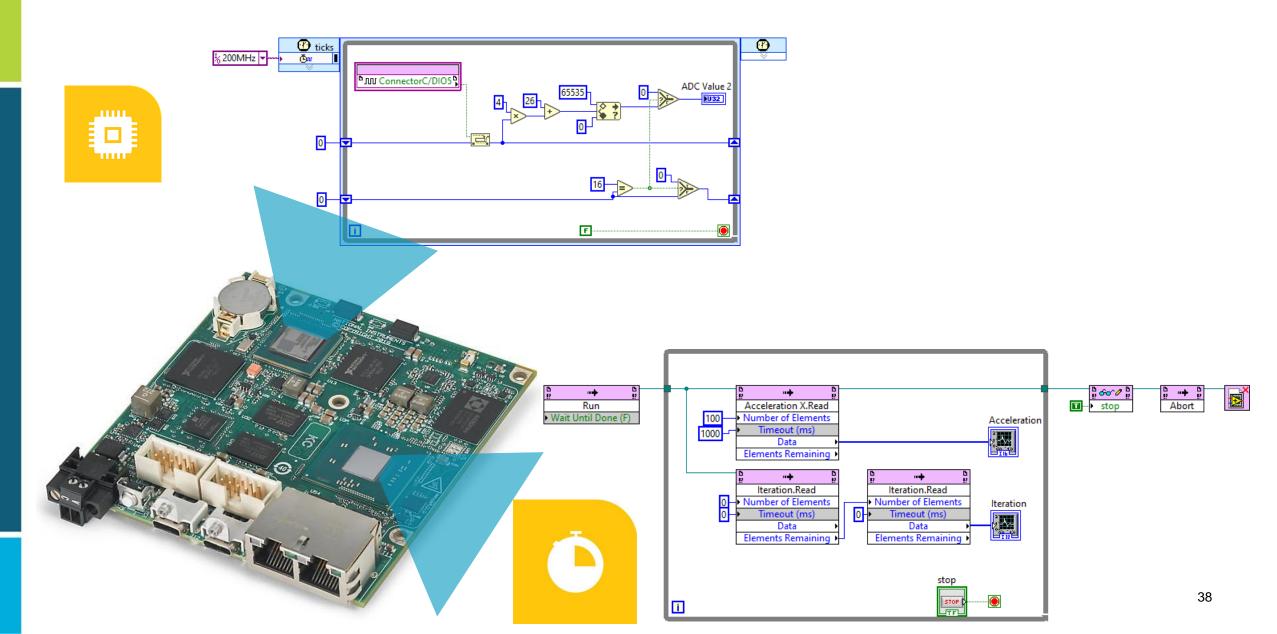

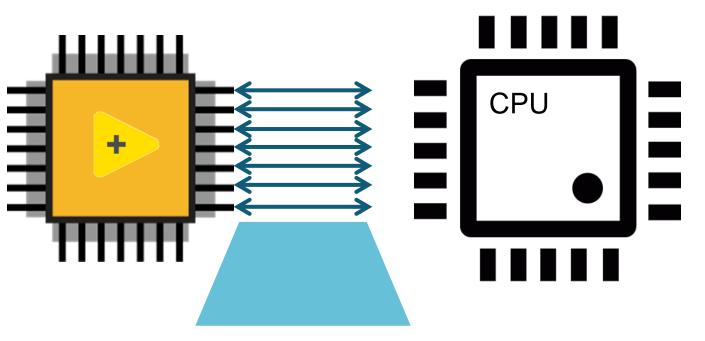

## Embedded systems programming

with LabVIEW Real-Time and FPGA

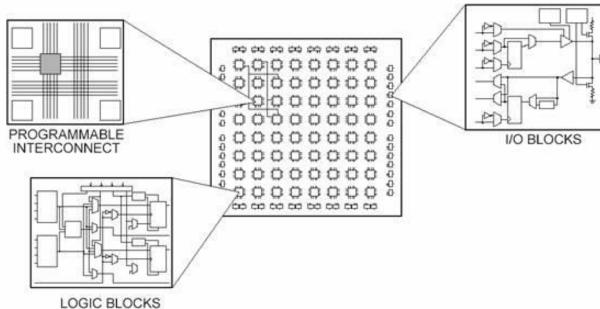

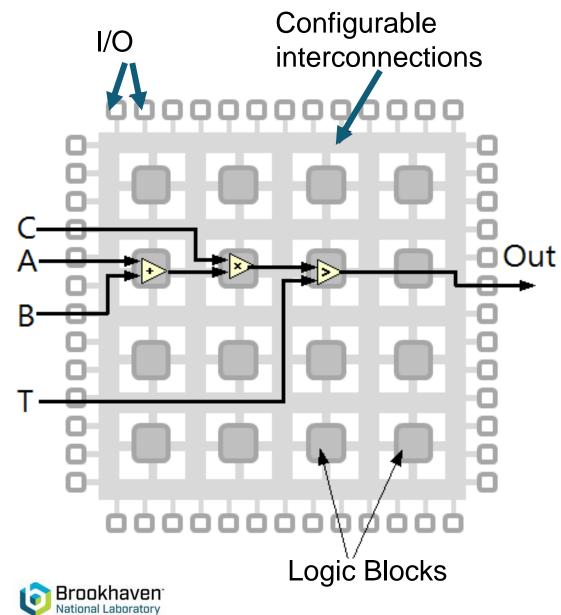

#### **FPGA**

FPGA (ang. Field Programmable Gate Arrays)

https://atadiat.com/wp-content/uploads/2020/03/fpga-chip.jpg

LOOIO BEOONO

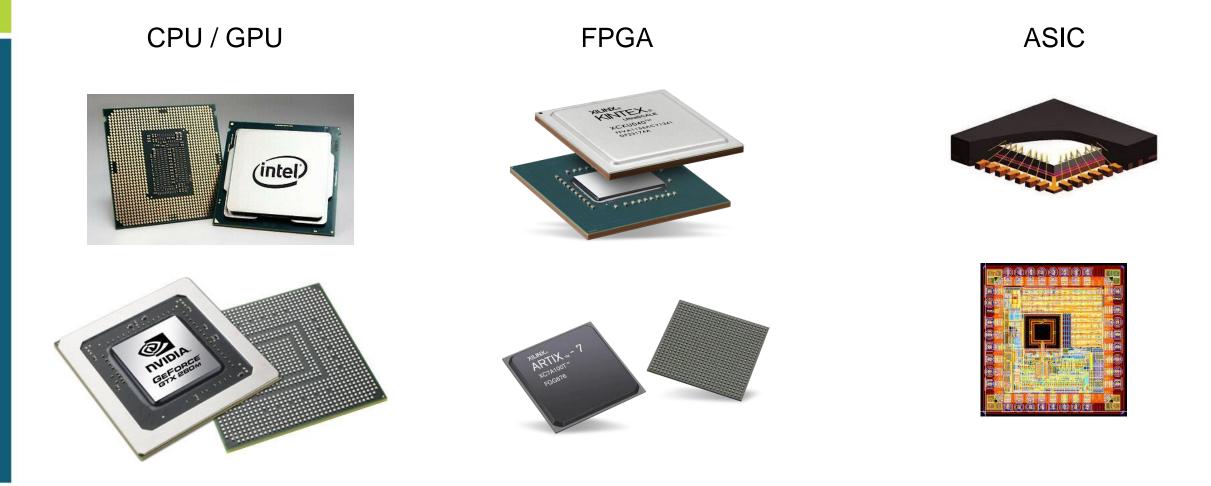

# **CPU vs FPGA vs ASIC**

# **Embedded system**

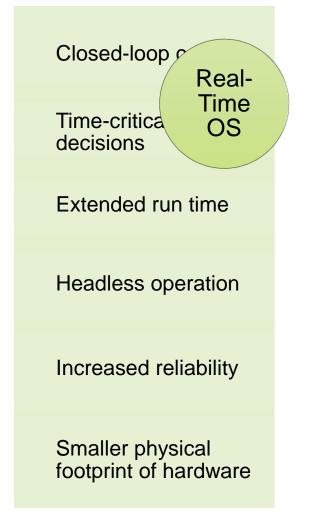

#### **RT-OS**

#### **RT-OS**

#### Hello World in FPGA

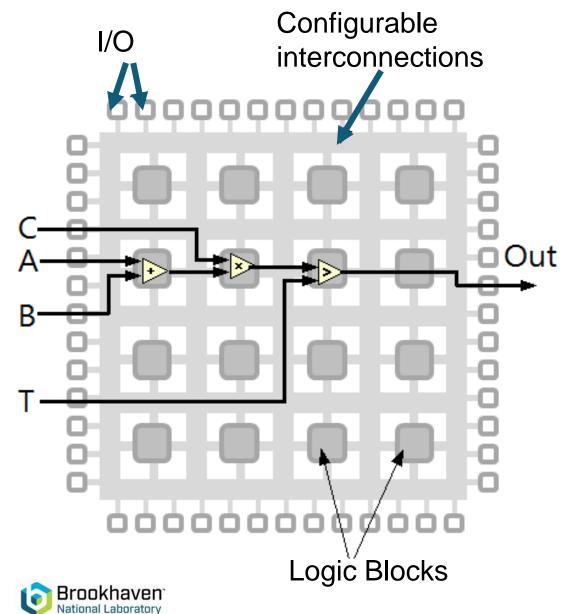

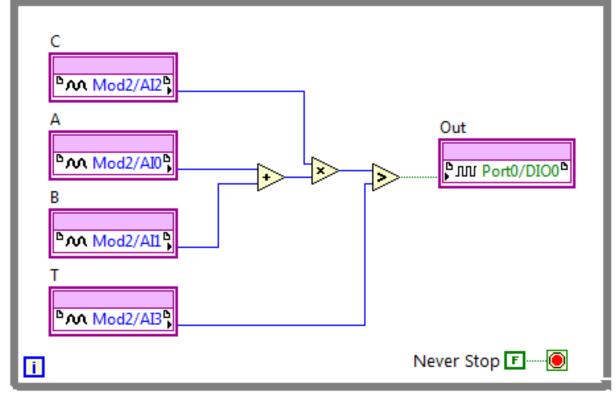

# FPGA I/O

# FPGA I/O

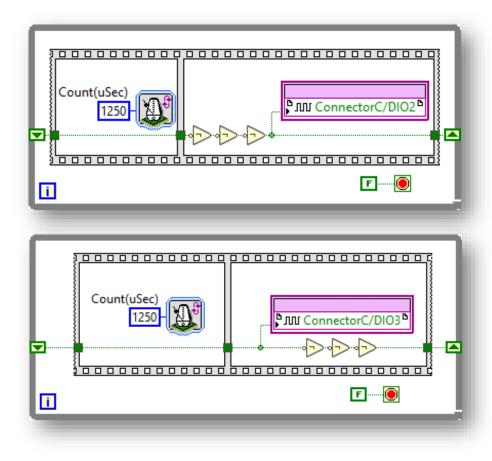

#### Simple FPGA Program in infinite loop

43

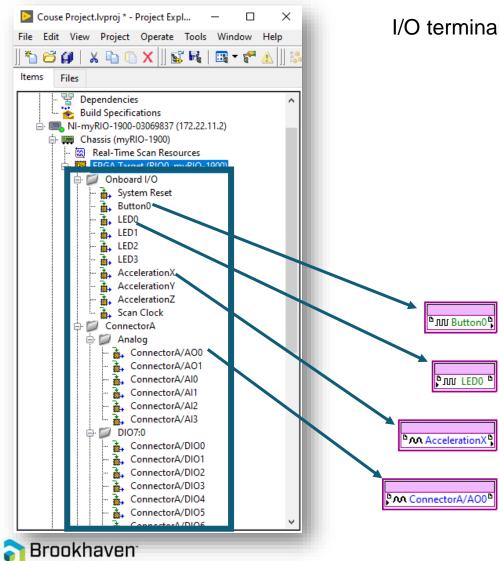

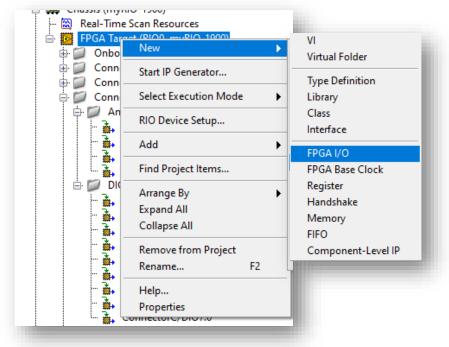

# FPGA – I/O

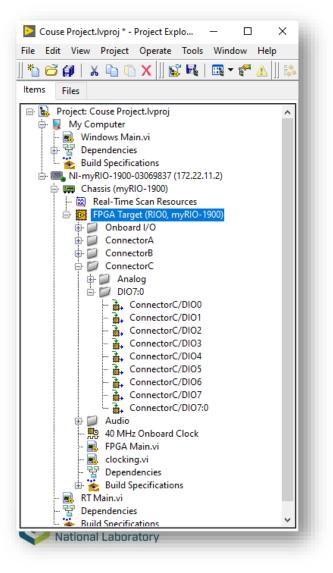

National Laboratory

I/O terminals are available in a project window

Boolean

Numeric

1.23) II

) 1.23 I III

Numeric 2

Boolean 2

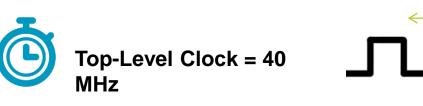

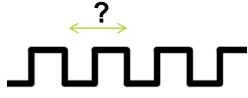

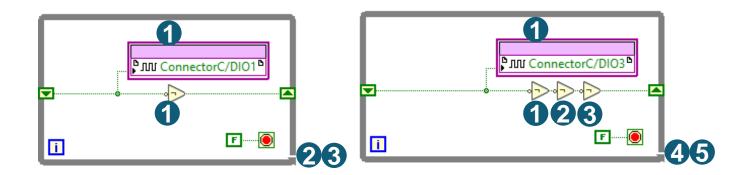

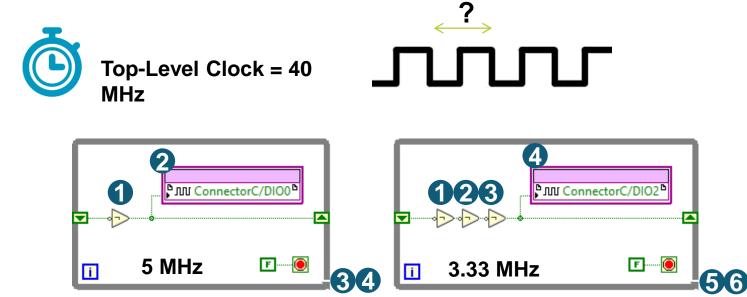

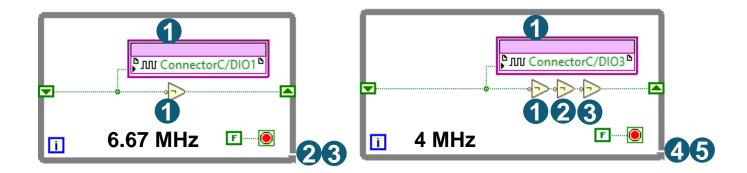

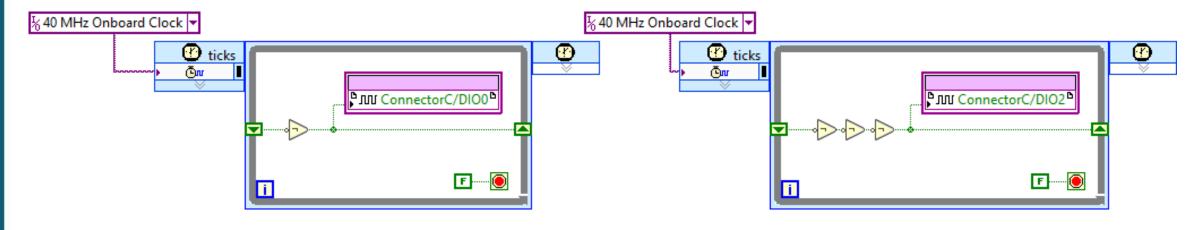

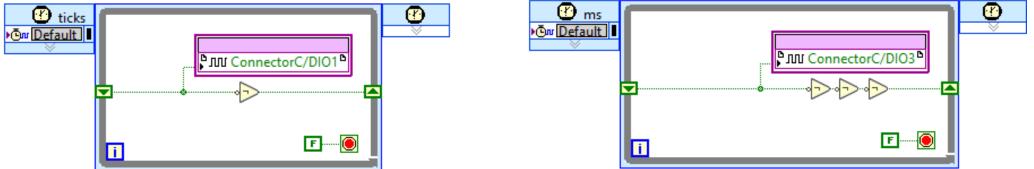

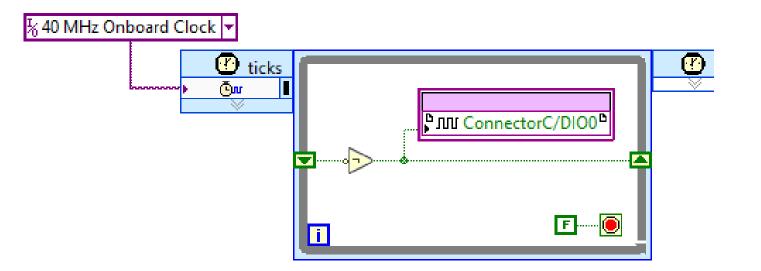

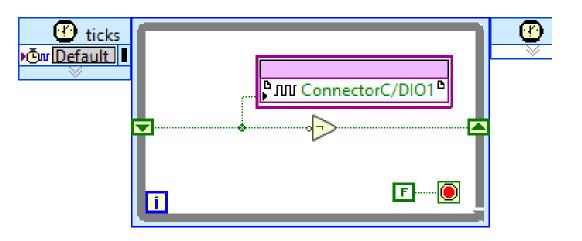

# **Single Operation Time**

5 MHz

#### What's the program speed?

| File       Edit       View       Project       Operate       Tools       Window       Help <ul> <li></li></ul> |

|----------------------------------------------------------------------------------------------------------------|

| AO MHz<br>Couse Project.lyproj/FPGA Target <                                                                   |

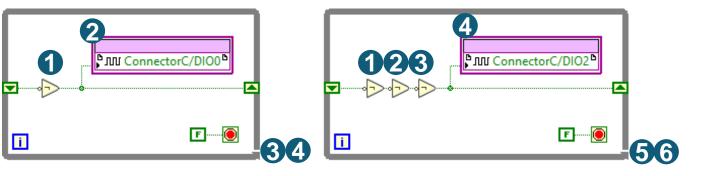

- 1. "Not" functions requires one clk cycle to execute

- 2. Outputing a value to physical pin takes one clk cycle

- 3. While Loop requires two clk cycles to execute

# What's the program speed ?

| Couse Project.Ivproj * - Project Explo — 🗆 🗙                                               |

|--------------------------------------------------------------------------------------------|

| File Edit View Project Operate Tools Window Help                                           |

| 🌇 🗃 🗿   🔏 🖻 🖺 🗙     👪 🔫   🔤 🕶 😭 🛕     🐉                                                    |

| Items Files                                                                                |

| 🖃 👪 Project: Couse Project.lvproj 🔨 🔺                                                      |

| 🖶 💂 My Computer                                                                            |

| Windows Main.vi                                                                            |

| Dependencies     Dependencies                                                              |

| Euild Specifications     Euild Specifications     E ■ NI-myRIO-1900-03069837 (172.22.11.2) |

|                                                                                            |

| Real-Time Scan Resources                                                                   |

| FPGA Target (RIO0, myRIO-1900)                                                             |

| 🖶 📁 Onboard I/O                                                                            |

| 🕀 📁 ConnectorA                                                                             |

| ⊕ 💭 ConnectorB                                                                             |

| 🖃 📁 ConnectorC                                                                             |

| 🖶 💭 Analog                                                                                 |

| 🖻 📁 DIO7:0                                                                                 |

| ConnectorC/DIO0                                                                            |

| - 👗 ConnectorC/DIO1                                                                        |

| ConnectorC/DIO2                                                                            |

| ConnectorC/DIO3                                                                            |

| - A ConnectorC/DIO4                                                                        |

| ConnectorC/DIO6                                                                            |

| ConnectorC/DI07                                                                            |

| ConnectorC/DIO7:0                                                                          |

| 🕀 📁 Audio                                                                                  |

| 膮 40 MHz Onboard Clock                                                                     |

| 🛃 FPGA Main.vi                                                                             |

| - 🔜 clocking.vi                                                                            |

| - 🚼 Dependencies                                                                           |

| 🕀 💼 Build Specifications                                                                   |

| RT Main.vi                                                                                 |

| - 'E' Dependencies                                                                         |

| Build Specifications                                                                       |

| National Laboratory                                                                        |

# What's the program speed ?

| 🔁 Couse Project.lvproj * - Project Explo — 🔲 🗙   |

|--------------------------------------------------|

| File Edit View Project Operate Tools Window Help |

| *≥ 😂 🗿   🗶 🖻 🖺 🗙     🕵 尾   🖩 ▼ 🐔 🛓     🐝         |

| Items Files                                      |

| 🖃 🗟 Project: Couse Project.lvproj 🔨              |

| 🖨 💂 My Computer                                  |

| - 🛃 Windows Main.vi                              |

| 🕀 🝟 Dependencies                                 |

| 🔤 📩 Build Specifications                         |

| ➡ ■ NI-myRIO-1900-03069837 (172.22.11.2)         |

| 🖻 🗰 Chassis (myRIO-1900)                         |

| Real-Time Scan Resources                         |

| EPGA Target (RIO0, myRIO-1900)                   |

| Onboard I/O                                      |

| ConnectorA     GonnectorB                        |

| ConnectorB                                       |

|                                                  |

|                                                  |

| ConnectorC/DIO0                                  |

| ConnectorC/DI01                                  |

| - ConnectorC/DIO2                                |

| - ConnectorC/DIO3                                |

| - ČonnectorC/DIO4                                |

| - ConnectorC/DIO5                                |

| - ConnectorC/DIO6                                |

| ConnectorC/DIO7                                  |

| ConnectorC/DIO7:0                                |

| 🕀 📁 Audio                                        |

| 膮 40 MHz Onboard Clock                           |

| 🔜 FPGA Main.vi                                   |

| 🔜 clocking.vi                                    |

| 🚼 Dependencies                                   |

| 🖶 📥 Build Specifications                         |

| - 🔜 RT Main.vi                                   |

| - 🚏 Dependencies                                 |

| Build Specifications                             |

| National Laboratory                              |

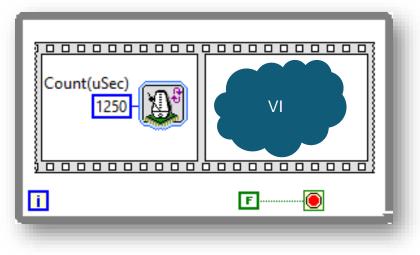

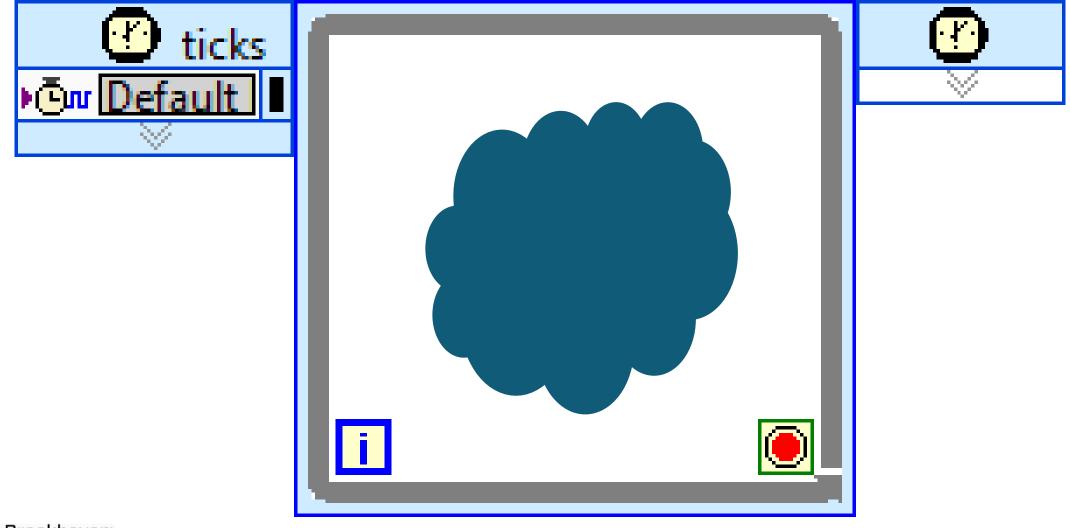

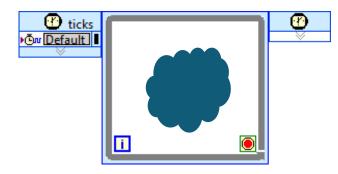

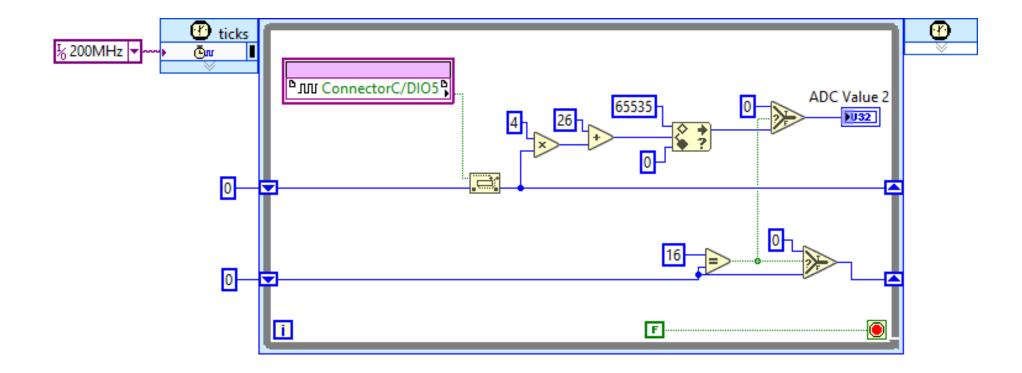

# **TIMING in FPGA**

|                          | Counter units |

|--------------------------|---------------|

| Counter units            | Ticks 🗸       |

| Ticks 🗸                  | ✓ Ticks       |

| Size of internal counter | uSec          |

| 32 Bit                   | mSec          |

| ✓ 32 Bit                 |               |

| 16 Bit                   |               |

| 8 Bit                    |               |

|                          | <b>32-</b> b  |

|                          |               |

|        | 1 do 4,294,967,296<br>tików | 1 µs do 71 minut | 1 ms do 49 dni |

|--------|-----------------------------|------------------|----------------|

| 16-bit | 1 do 65,536 tików           | 1 µs do 65 ms    | 1 ms do 65 s   |

| 8-bit  | 1 do 256 tików              | 1 µs do 256 µs   | 1 ms to 256 ms |

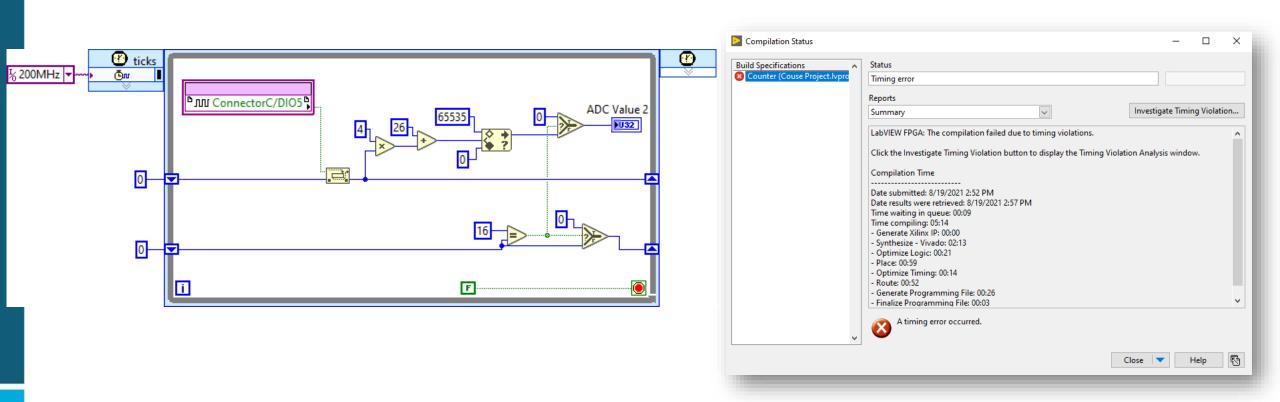

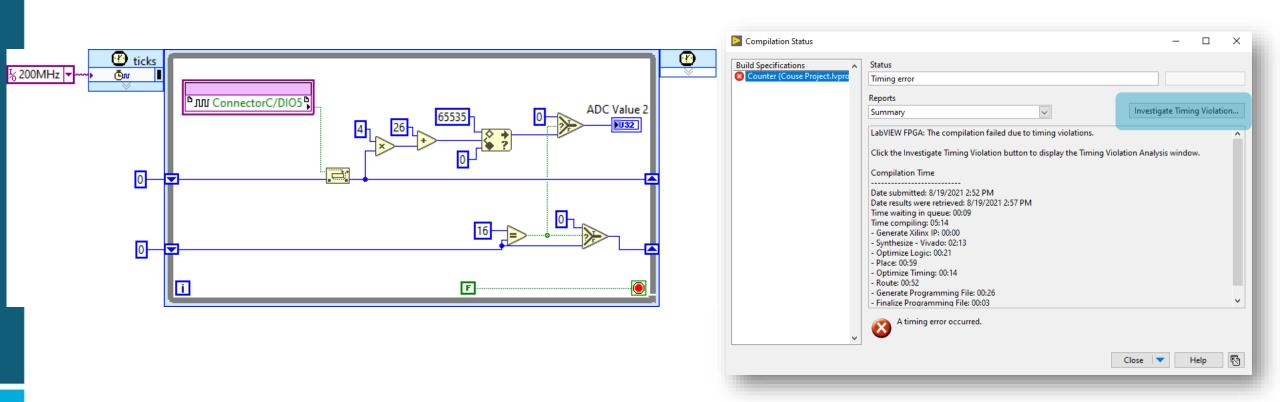

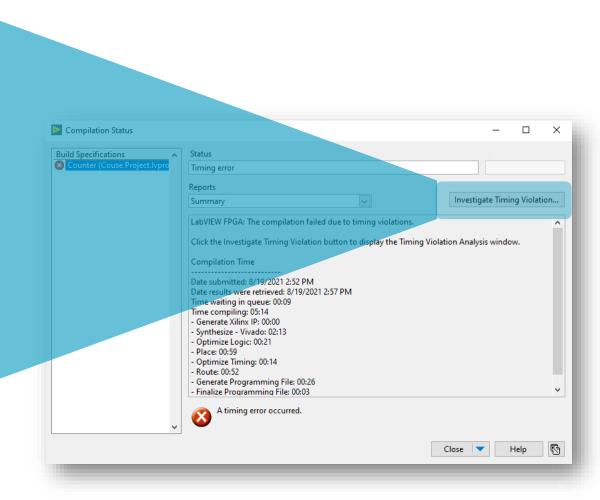

# **TIMING IN FPGA - example**

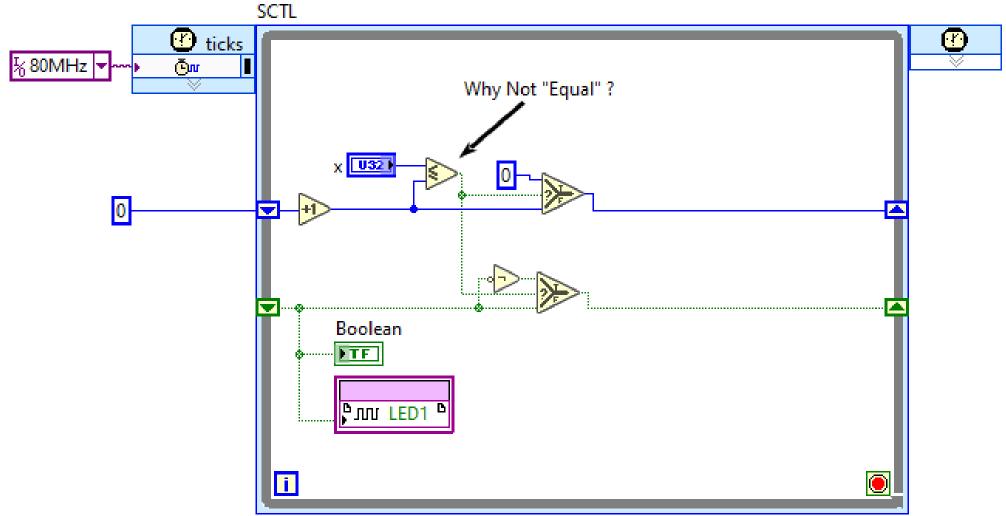

# SINGLE-CYCLE TIMED LOOP

| Paths                                                                                                                                                                             |        | Total<br>Delay                                         | Logic<br>Delay                                       | Routing<br>Delay | Max<br>Fanout                                          | ^ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------|------------------------------------------------------|------------------|--------------------------------------------------------|---|

| <ul> <li>Path 1 : Requirement 5.00ns missed by 7.</li> <li>Timed Loop<br/>Multiply<br/>Add<br/>In Range and Coerce<br/>Non-diagram component<br/>Non-diagram component</li> </ul> | 79ns   | 12.19<br>10.06<br>7.68<br>1.75<br>0.63<br>0.92<br>1.22 | 8.75<br>8.13<br>6.35<br>1.15<br>0.63<br>0.31<br>0.31 | 3.44<br>1.93     | 63.00<br>2.00<br>2.00<br>1.00<br>1.00<br>4.00<br>63.00 |   |

| Close                                                                                                                                                                             | Show E | lement                                                 | Show                                                 | Path             | Help                                                   | * |

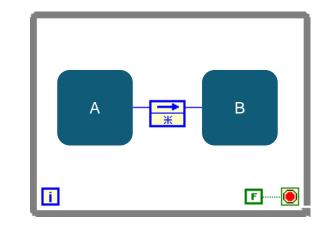

#### PIPELINE

+ easy to configure

- + similar to an array

- + doesn't require contro/indicator

+ no data copies

+ can be a type defined

- no synchronization methods

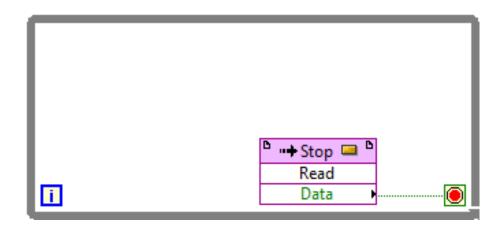

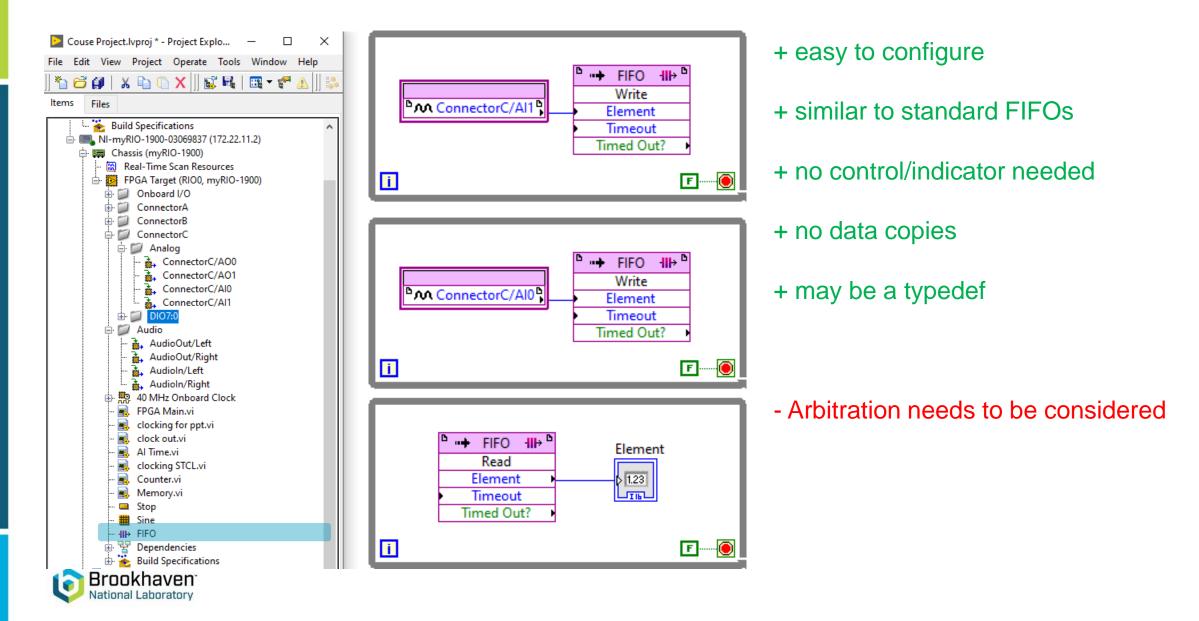

# FIFO - III →

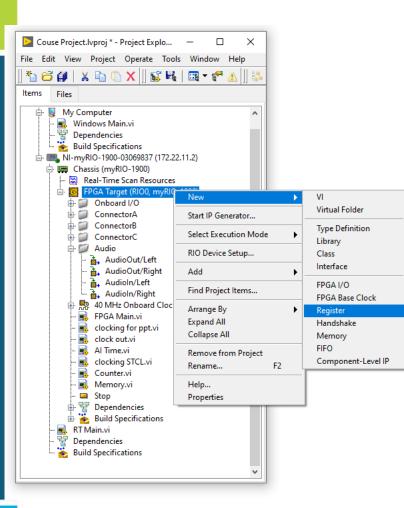

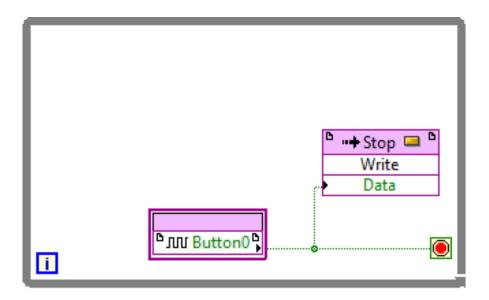

# HANDSHAKE

Couse Project.lvproj \* - Project Explo...  $\times$ File Edit View Project Operate Tools Window Help |\*`a 😂 🎒 | 🗶 🐚 🕦 🗙 || 🕵 尾 | 💷 ד 🕐 🔬 || 🐉 Items Files 🛄 🌺 Build Specifications ■ ■ NI-myRIO-1900-03069837 (172.22.11.2) 🖨 🗰 Chassis (myRIO-1900) 🕅 Real-Time Scan Resources FPGA Target (RIO0, myRIO-1900 Onboard I/O ÷ ConnectorA ConnectorB 🖨 💋 ConnectorC 🗄 📁 Analog ConnectorC/AO0 ConnectorC/A01 ConnectorC/Al0 ConnectorC/Al1 🗄 📁 DIO7:0 🖻 🗐 Audio AudioOut/Left 🚠 AudioOut/Right Audioln/Left Audioln/Right 40 MHz Onboard Clock 🛋 FPGA Main.vi clocking for ppt.vi clock out.vi 🛋 🛛 Al Time.vi clocking STCL.vi 🛋 Counter.vi 🛋 Memory.vi Stop I Sine -III+ FIFO o-o Handshake 🕎 Dependencies 🐞 Build Specifications ÷. 🛋 RT Main.vi ¥ Dependencies **Build Specifications**

| ß | •• <b>+</b> Handshake ∞-∞ <sup>D</sup> | נ |

|---|----------------------------------------|---|

|   | Write                                  |   |

|   | Data                                   |   |

| Þ | Input Valid                            |   |

|   | Ready for Input                        | Þ |

| Β, | + Han   | dshake   | <u>⊙-</u> ⊙ <sup>D</sup> |

|----|---------|----------|--------------------------|

|    | F       | Read     |                          |

|    | [       | Data     | •                        |

|    | Outp    | ut Valid | •                        |

| ŀ  | Ready f | for Outp | ut                       |

+ easy to configure

- + use as single-element FIFO

- + no control required

- + no data copy

- + may be a typedef

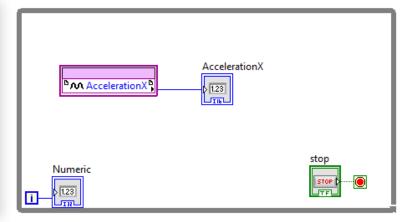

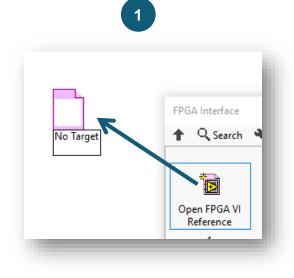

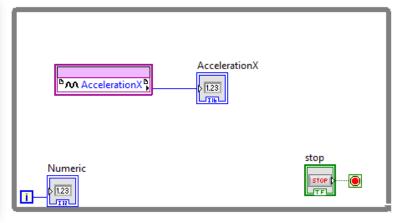

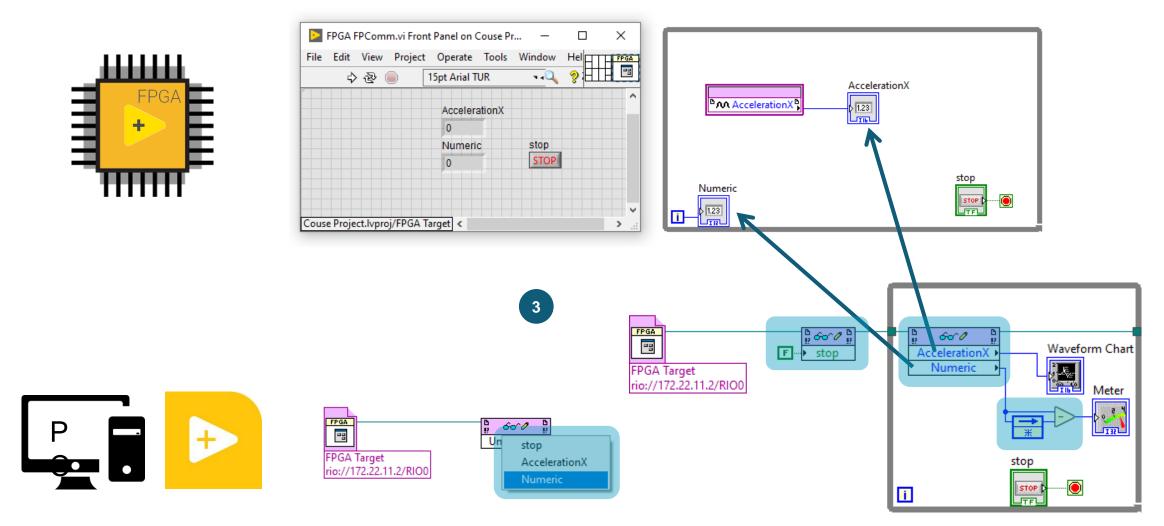

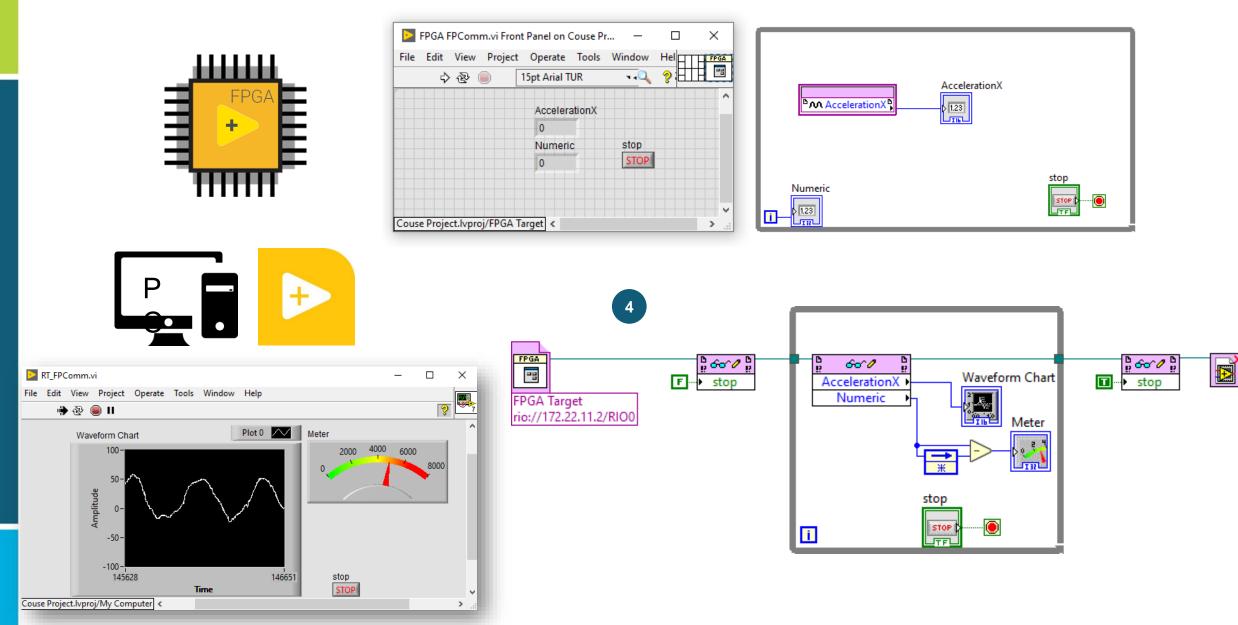

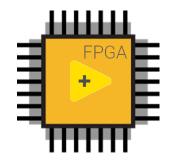

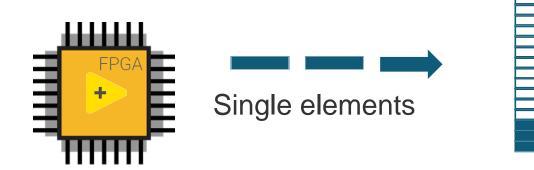

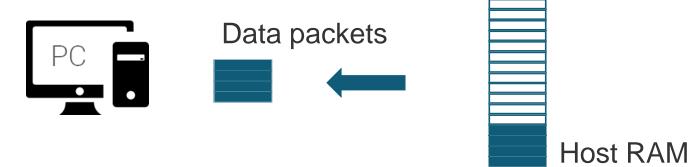

# **FPGA communication**

# $\mathsf{FPGA} \leftrightarrow \mathsf{CPU}$

#### + IP components delivered

- Front Panel Communication

- $\circ$  DMA

Brookhaven National Laboratory  $\circ$  Interruptions

| File Edit View Proje      | ct Operate Tools | Window | Hel | FPG |

|---------------------------|------------------|--------|-----|-----|

| 수 🕸 🥚                     | 15pt Arial TUR   | Q      | ?:E |     |

|                           |                  |        |     |     |

|                           | AccelerationX    |        |     |     |

|                           | 0                |        |     |     |

|                           | Numeric          | stop   |     |     |

|                           | 0                | STOP   |     |     |

|                           |                  |        |     |     |

|                           |                  |        |     |     |

|                           |                  |        |     |     |

| Couse Project.lvproj/FPGA | Target <         |        |     | >   |

| File Edit View | Project | Operate      | Tools  | Window | Hel | FPGA |

|----------------|---------|--------------|--------|--------|-----|------|

| 今昼             |         | 15pt Arial T | UR     | •••    | ?:± |      |

|                |         |              |        |        |     | ^    |

|                |         | Accelera     | ationX |        |     |      |

|                |         | 0            |        |        |     |      |

|                |         | Numeri       | с      | stop   |     |      |

|                |         | 0            |        | STOP   |     |      |

|                |         |              |        |        |     |      |

|                |         |              |        |        |     |      |

|                |         |              |        |        |     |      |

|        | 2                                |   |

|--------|----------------------------------|---|

| No Tar | Visible Items                    |   |

|        | Help                             |   |

|        | Examples                         |   |

|        | Description and Tip              |   |

|        | Breakpoint                       |   |

|        | FPGA Interface Palette           | + |

|        | Replace                          |   |

|        | Configure Open FPGA VI Reference |   |

|        | Remove and Rewire                |   |

|        | Create                           | ► |

| Configure Open FPGA VI Reference            | ×    |                                  |

|---------------------------------------------|------|----------------------------------|

| Open<br>O Build Specification               | *    |                                  |

| VI     FPGA Target\FPGA FPComm.vi           | *    |                                  |

| O Bitfile                                   |      |                                  |

| Run the FPGA VI                             |      | FPGA Target<br>rio://172.22.11.2 |

| Bind FPGA host reference to type definition |      |                                  |

| OK Cancel                                   | Help |                                  |

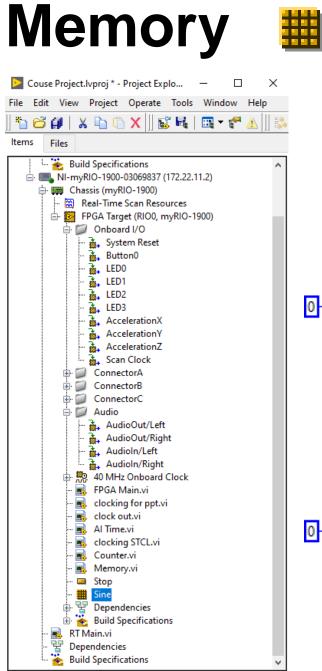

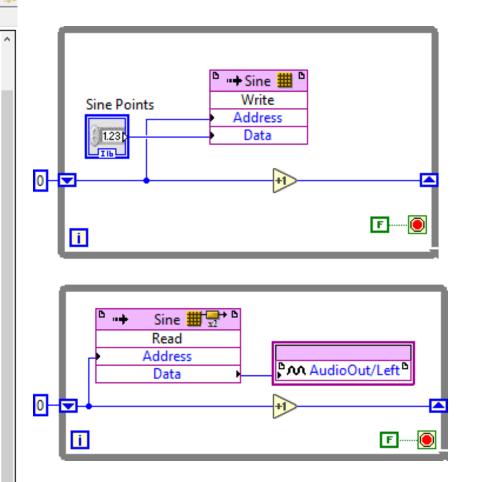

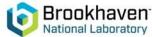

**FPGA** memory

| Type<br>Acceleration X<br>Type<br>Target to Host - DMA<br>Requested Number of Elements<br>1023<br>Implementation                                                                                                            | 2                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Acceleration X Type Target to Host - DMA Target-Scoped Host to Target - DMA Requested Number of Elements 1023                                                                                                               | 2                                                                                                               |

| Target to Host - DMA       ✓       Target-Scoped         Host to Target - DMA       ✓       Host to Target - DMA         Requested Number of Elements       ✓       Target to Host - DMA         1023       1023       1023 | 2                                                                                                               |

| Requested Number of Elements July Target to Host - DMA<br>1023                                                                                                                                                              | 9                                                                                                               |

| Requested Number of Elements V Target to Host - DMA                                                                                                                                                                         |                                                                                                                 |

| 1023                                                                                                                                                                                                                        | the second se |

| level and established                                                                                                                                                                                                       |                                                                                                                 |

| Implementation                                                                                                                                                                                                              |                                                                                                                 |

| Block Memory                                                                                                                                                                                                                |                                                                                                                 |

| Actual Number of Elements                                                                                                                                                                                                   |                                                                                                                 |

| 1023                                                                                                                                                                                                                        |                                                                                                                 |

| Control Latio                                                                                                                                                                                                               |                                                                                                                 |

| Control Logic<br>Slice Fabric                                                                                                                                                                                               |                                                                                                                 |

|                                                                                                                                                                                                                             |                                                                                                                 |

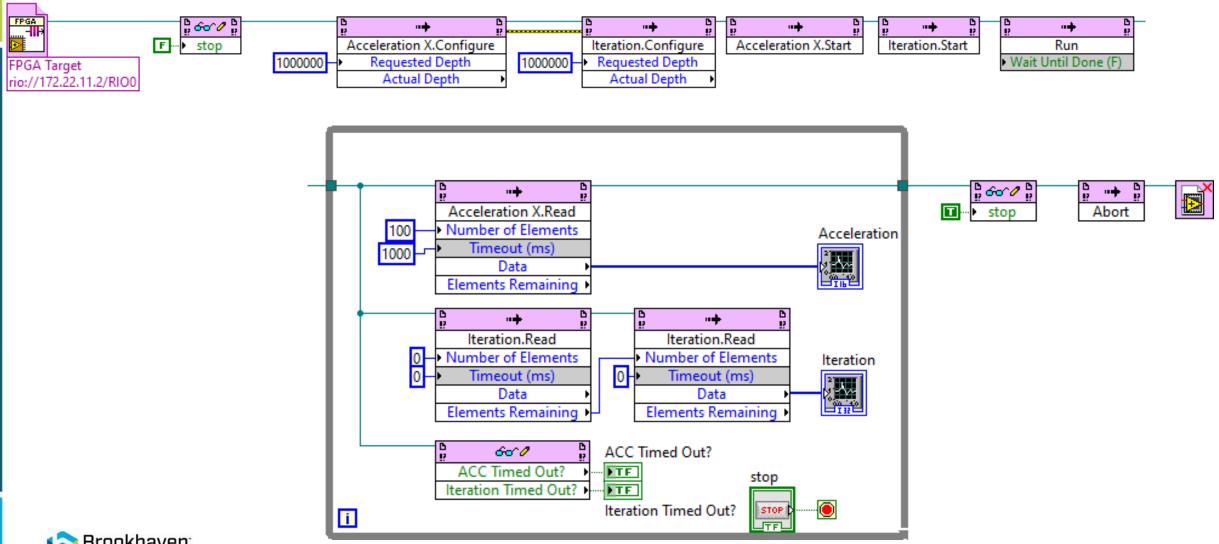

# **Counter FPGA implementation Example**

# Data Acquisition in ASIC testing

Piotr Maj on behalf of ASIC group

Date 10/19/2023