### ePIC TIC Meeting - Barrel Imaging Calorimeter (BIC)

### **BIC - AstroPix**

Manoj Jadhav HEP, Argonne National Laboratory

October 2, 2023

### AstroPix

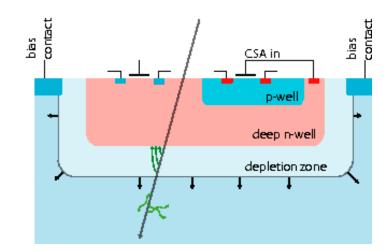

#### HV-CMOS Monolithic Active Pixel Sensor (MAPS):

- Combination of silicon pixel & Front-End ASIC

- On-pixel charge amplification and digitization

- Technology uses more typical CMOS wafer processing for cost effective mass production

- Fabrication on single wafer enables shorter design cycle

- No need to bump-bond to each pixel improves yield

#### AstroPix (based on ATLASPix3 arXiv:2109.13409)

- 180nm HV-CMOS MAPS sensor designed at KIT (also designed ATLASPix, MuPix, etc.)

- Developed for AMEGO-X GSFC/NASA mission (Upgrade to the Fermi's LAT)

- Power consumption <1.5 mW/cm<sup>2</sup>

- Energy resolution target of 2% @ 662keV

# **AstroPix Developments**

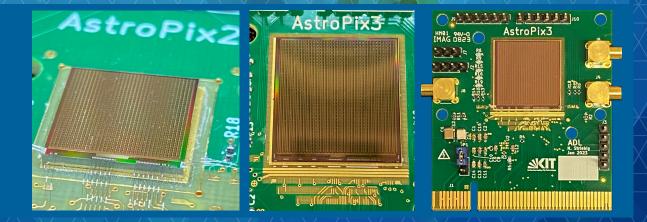

#### AstroPix v1 - January 2021

- $0.45 \times 0.45 \text{ cm}^2$  chip, 175 µm pixel pitch

- 18 × 18 pixel matrix

- Power dissipation ~14.7 mW/cm<sup>2</sup>

#### AstroPix v2 - December 2021

- $1 \times 1 \text{ cm}^2$  chip with 250 µm pixel pitch

- $35 \times 35$  pixel matrix

- Hit identification with Row/Column readout

- Power dissipation ~3.4 mW/cm<sup>2</sup>

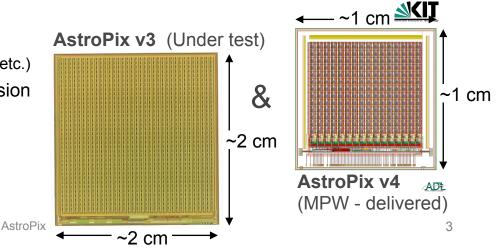

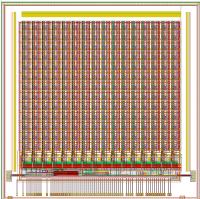

### AstroPix v3 - February 2023

- $2 \times 2 \text{ cm}^2$  chip with 500 µm pixel pitch

- Power dissipation <1 mW/cm<sup>2</sup> (targeted)

- Timestamp clock 2.5MHz, ToT 200 MHz

- 10 byte data frame per hit

(Amanda's talk) AstroPix

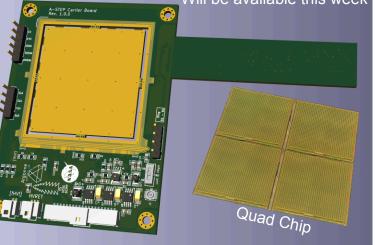

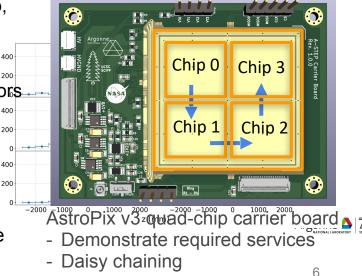

AstroPix v3 Quad-chip Carrier Board 4

### AstroPix v4/v5

#### AstroPix v4 : Final design version will small size

- Chip size 1  $\times$  1 cm<sup>2</sup>; Thickness 700  $\mu$ m, V<sub>BD</sub> ~ 400V

- Pixel pitch 500  $\mu$ m with pixel size 300  $\mu$ m, 16  $\times$  16 pixel matrix

- Individual pixel readout with individual hit buffer

- No identification issue due to ghost hits

- 3 Timestamps 2.5MHz (TS), 20 MHz (Fine TS), and 16 bit Flash TDC

- Fast ToT and Timestamp with 3.125 ns time resolution

- TuneDACs Pixel-by-pixel threshold tuning and pixel masking

- Daisy Chain readout pass hits to next chip through QSPI

- Self-triggered (reads out active hits)

#### AstroPix v5 : Full size final design

- No planned design changes

- Fix any bug from v4

- Full size chip 2  $\times$  2 cm², pixel pitch 500  $\mu m,$

- $35 \times 35$  pixel matrix  $\rightarrow 1225$  hit buffers

## **AstroPix Readout**

- 8 bytes data per hit header (chipID, payload), row/column, timestamp, ToT

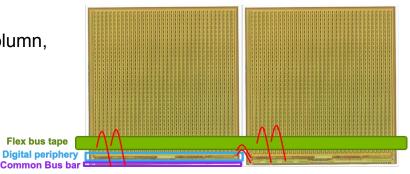

- SPI I/O daisy chained chip-to-chip signal transfer

- signals are digitized & routed out to the neighboring chip using 5 SPI lines via wire bond

- Power/Logic I/O distribution on the module (through a bus tape)

- 4 power lines (LV, HV), ~20 Logic I/O (SPI, clk, timestamp, interrupt, digital Injection, etc.)

- HV, VDDA/VDDD(1.8V), VSSA(1.2V), Vminuspix(0.7V) §

- power distribution can be controlled using voltage regulators

- mostly part of end of the stave services

- Data will be received by FPGA at the end of stave

- FPGA aggregates data before sending off-detector

- Low heat load at chip, only cooling of end of the stave card

- Operational temperature for AstroPix is at room temperature and considered to be operated at 22 °C AstroPix

# AstroPix at ePIC

#### Low Rates

- The expected hit rate for **all imaging layers together** is well below < 3 × 10<sup>7</sup> Hz

- This translates to a maximum hit rate per tracker stave (1 x 104 chips) < 36 kHz</li>

#### Zero-suppression below threshold 20 keV (4 × noise floor

well suited for EIC electromagnetic showers

Timing requirement: 3.125 ns (v4/v5) - **driven by 10 ns bunch crossing**

#### Low Ionization radiation dose and neutron flux

- The maximum ionizing radiation dose < 1 kRad/year for the barrel region

- Max neutron flux order of **10**<sup>9</sup> **n**<sub>equivalent</sub>/**cm**<sup>2</sup> **per year**

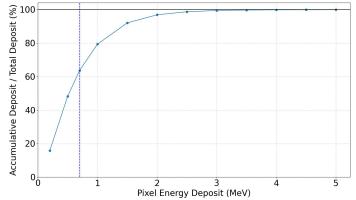

Dynamic range (see plot for 2 GeV e<sup>-</sup>) ~ **3 MeV**

Accumulative energy deposit to the total energy deposit for 2 GeV electrons.

- About 63% of the energy deposit was made through hits with deposit < 700 keV

- hits with deposit < 3 MeV contribute to 99% of the total energy deposit

## **AstroPix Assembly**

#### AstroPix v5 (Production version)

- Full size chip  $2 \times 2$  cm<sup>2</sup>, pixel pitch 500  $\mu$ m,

- $35 \times 35$  pixel matrix  $\rightarrow 1225$  hit buffers

- Fix any bug from v4

\*The designs presented on these slides are not final but for illustration only

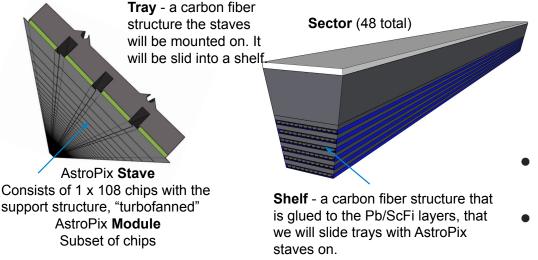

#### **Module Strategy**

- QC testing with wafer probing + Module and stave level QC testing and tuning

- "Baseline" model of Modules on Stave

- Module 8 single chips

- Stave 13 Modules 104 chips

- 12 or 14 Staves per AstroPix layer per Calorimeter Sector

- Total 249600 chips

- All staves are identical and gets combined in a separate production step

- Data transmitted to end of the Stave card using flex base tape

- Institutions ANL, GSFC/NASA, KIT ,UCSC, Korea, Oklahoma State 8

# **AstroPix Timeline and Production**

#### v3 full size chip (ongoing testing)

- Test bench characterization (ongoing)

- Testbeam performance studies

- Active and passive irradiation ~10<sup>15</sup> n<sub>equivalent</sub>/cm<sup>2</sup>

- Quad-chip readout (ready to test) for NASA's hosted payload mission (A-Step) January 2025

- Integration with Pb/SciFi FY2024 (Henry's talk)

#### v4 new features for better performance (MWP)

- **Final design version**, smaller chip (1cm × 1cm)

- Fabricated wafers delivered last week

- Chip carrier board design for bench test is ready for the PCB fabrication

#### v5 full size final chip

- Fix any bugs from v4

- v5 chips available November 2024

|                                 | FY24 |   |   |   |   |   |   |    |    |   | FY25 |    |                                                                                                                             |     |   |   |   |   |   |   |   |   |   |   |

|---------------------------------|------|---|---|---|---|---|---|----|----|---|------|----|-----------------------------------------------------------------------------------------------------------------------------|-----|---|---|---|---|---|---|---|---|---|---|

| Tasks                           | 0    | Ν | D | J | F | м | A | М  | JJ | Α | s    | 0  | Ν                                                                                                                           | D   | J | F | М | Α | М | J | J | Ą | s | ŀ |

| Full ComPair Instrument         |      |   |   |   |   |   |   | CI | DR |   |      |    |                                                                                                                             |     |   |   |   |   |   |   |   |   | P | Ĩ |

| AstroPix Tracker                |      |   |   |   |   |   |   |    |    |   |      | TI | <r-f< td=""><td>PIF</td><td>R</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>ĺ</td></r-f<> | PIF | R |   |   |   |   |   |   |   |   | ĺ |

| AstroPix v3 Quad Chip Testing   |      |   |   |   |   |   |   |    |    |   |      |    |                                                                                                                             |     |   |   |   |   |   |   |   |   |   | i |

| v3 Depletion Test               |      |   |   |   |   |   |   |    |    |   |      |    |                                                                                                                             |     |   |   |   |   |   |   |   |   |   | l |

| v3 multi-layer testing (A-STEP) |      |   |   |   |   |   |   |    |    |   |      |    |                                                                                                                             |     |   |   |   |   |   |   |   |   |   | l |

| Integrate v3 w/ proto Segment   |      |   |   |   |   |   |   |    |    |   |      |    |                                                                                                                             |     |   |   |   |   |   |   |   |   |   | ĺ |

| AstroPix v4 MPW design + fab    |      |   |   |   |   |   |   |    |    |   |      |    |                                                                                                                             |     |   |   |   |   |   |   |   |   |   | Ī |

| AstroPix v4 carrier board       |      |   |   |   |   |   |   |    |    |   |      |    |                                                                                                                             |     |   |   |   |   |   |   |   |   |   | l |

| AstroPix v4 testing             |      |   |   |   |   |   |   |    |    |   |      |    |                                                                                                                             |     |   |   |   |   |   |   |   |   |   | ĺ |

### **BIC@ePIC** Timeline

AstroPix v5 testing

v4 Depletion Test

Standard test procedure dev. AstroPix v5 testing carrier board AstroPix v5 design + fab

- Prototype R&D (v3) Ongoing till Nov 24

- Pre-Production (v5) chips starts Nov 2024 (More info in Maria's talk)

#### Production

• Fabrication by TSI - with a large production order, AMS is a backup

Deliver to ANL

#### GSFC/NASA ComPair-2 AstroPix timeline

### Thank you