### Report from the Interaction Tagger Workfest

P. Antonioli (INFN-Bologna)

### But here the short version summary

The workfest was so successfull that we agreed the title of the workfest was misleading

#### Session

Interaction Tagger Workfest

**(**) 26 Jul 2024, 13:00

### But here the short version summary

The workfest was so successfull that we agreed the title of the workfest was misleading

Session

Interaction Tagger Workfest

7 26 Jul 2024, 13:00

#### Session

dRICH Data Reduction Workfest How to tag tracks in dRICH acceptance (an interaction tagger is another thing, eh)

26 Jul 2024 @ **17:00**

# Why this workfest?

Since long time we aired the idea of a tagger able to provide a simple signal to curb dRICH data throughput

an agnostic tagger just for detecting tracks in dRICH acceptance could be built with **something specific (dTT)** and/or using also information from **other detectors** (FHCal, FEMCal, TOF, ...)

Since long time we aired the idea of smart things happening analysing quickly dRICH data (ML, pattern regognition, ....)

"data reduction algorithms integrated with SRO DAQ and computong"

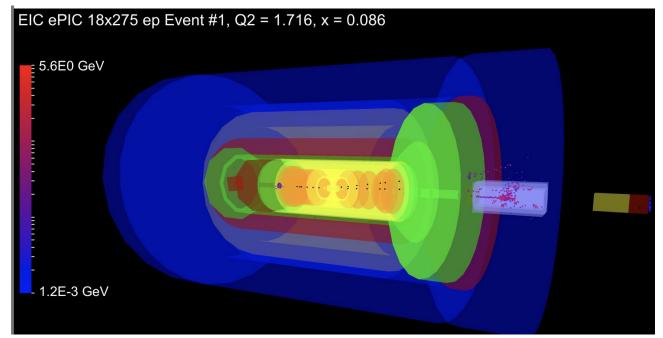

Generally speaking, an interaction tagger for ePIC (1 interaction/every 200 BC) is a good idea

This should be **unbiased minimum-bias interaction tagger**

| 13:00 | Introduction                  |                                          | Marco Contalbrigo         |  |

|-------|-------------------------------|------------------------------------------|---------------------------|--|

|       | Rm 61, Rausch Business Center |                                          | 13:00 - 13:10             |  |

|       | dRICH Data Stream             | dRICH data throughput                    | Pietro Antonioli et al. 🥝 |  |

|       | Rm 61, Rausch Business Center |                                          | 13:10 - 13:30             |  |

|       | Interaction Minbias Trigger   |                                          | Dr E. C. Aschenauer       |  |

|       | Rm 61, Rausch Business Center | unbiased minimum-bias interaction tagger | 13:30 - 13:50             |  |

|       | ePIC DAQ Scheme               | SRO DAQ and computing                    | David Lawrence et al.     |  |

| 14:00 | Rm 61, Rausch Business Center |                                          | 13:50 - 14:10             |  |

|       | dRICH Tagget                  | something specific (dTT)                 | Marco Battaglieri         |  |

|       | Rm 61, Rausch Business Center |                                          | 14:10 - 14:30             |  |

|       | dRICH Data Filter             | data reduction algorithms                | Dr Luca Pontisso et al.   |  |

|       | Rm 61, Rausch Business Center |                                          | 14:30 - 14:50             |  |

|       | Forward HCal                  |                                          | Miguel Arratia et al. 🥝   |  |

| 15:00 | Rm 61, Rausch Business Center | other detectors                          | 14:50 - 15:10             |  |

|       | Forward ECal                  |                                          | Oleg Tsai et al. 🥝        |  |

|       | Rm 61, Rausch Business Center |                                          | 15:10 - 15:30             |  |

### Interaction tagging explained with ZEUS

Construct a minimum-bias interaction tagger to cover full physics in an unbiased way is a different problem

combination of BHCAL + FHCAL to start with but...

(<u>remember</u>: @HERA hadrons went from right to left, @EIC they will go from left to right even if "forward" means always hadron direction)

The project/TIC will follow up coordinating different detectors info to build such tagger

### the dRICH data stream

#### Back to ATHENA proposal!

#### dRICH data stream at EIC day-0

| Interaction tagger reduction factor       | 1 🔻      |                    | Channel/chip 04                                                |       |

|-------------------------------------------|----------|--------------------|----------------------------------------------------------------|-------|

| Interaction tagger latency [s]            | 2,00E-03 | )                  | Shutter width (ns) 10 ▼ (i                                     |       |

| EIC parameters                            |          |                    |                                                                |       |

| EIC Clock [MHz]                           | 98,522   |                    |                                                                |       |

| Orbit efficiency (takes into account gap) | 0,92     |                    | We first learn how to calibrate the s                          | hutte |

| dRICH data stream analysis                |          | Limit              | Comments                                                       |       |

| Sensor rate per channel [kHz]             | 3,00 ▼   | 4.000,00           |                                                                |       |

| Rate post-shutter [kHz]                   | 2,70     | 800,00             |                                                                |       |

| Throughput to serializer [ Mb/s]          | 1,73     | 788,16             |                                                                |       |

| Throughput from ALCOR64 [Mb/s]            | 13,80    |                    | limit FPGA dependent: - check with RDO                         |       |

| Throughput from RDO [ Gb/s]               | 0,05     | 10,00              | based on VTRX+                                                 |       |

| Input at each DAM I [Gbps]                | 2,53     | 470,00             |                                                                |       |

| Buffering capacity at DAM I [MB]          | 0,65     |                    | to be checked but seems manageable                             |       |

| Throughput from DAM I to DAM II [Gbps]    | 2,53     | 10,00              | this might be higher (from FELIX to FELIX)                     |       |

| Output to each DAM II [Gbps]              | 68,41    | 270,00             |                                                                |       |

| Aggregated dRICH data throughput          |          | Comments           |                                                                |       |

| Total input at DAM I [ Gb/s ]             | 68,41    | This is only "insi | de" DAM, not to be transferred on PCI                          |       |

| Total input at DAM II [ Gb/s ]            | 68,41    | This is based on   | aggregation above + reduction factor of the interaction tagger |       |

| Total output from DAM II [ Gb/s ]         | 68,41    | Further reduction  | n possible to be investigated (FPGA level?)                    |       |

- Presented full parameterization of dRICH data stream

- Main three parameters are ALCOR shutter window, "tagger data reduction factor (DRF)" and DCR/sensor

- At maximum radiation damage, with DRF=1 trhoughput is 1.4 Tbps (dRICH aggregated)

- At EIC day-0 /DRF=1/no shutter just 66.6 Gbps

- DRF=200 corresponds to physics, DRF=20 would be enough...

The dRICH data stream is not an issue, it is well understood

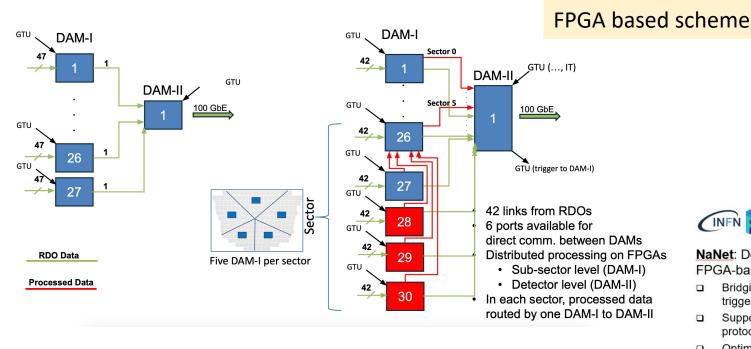

### dRICH DAQ (from RDO to DAQ servers)

Full dRICH data modeling understood: throughput will be really high only after several years of operations

- see <u>ageing modeling and annealing procedures for SiPM DCR</u> (backup and in pre-brief)

- see <u>detailed data modeling throughput</u> (backup)

- see J. Landgraf presentation

From electronics & DAQ PDR

dRICH DAQ design foresees two levels of DAMs:

I-level DAM (27)

II-level DAM (1)

FELIX

FELIX

1248

47 links to PDU

1 link to II-level DAM

1 link from central ePIC [clock/trigger]

ePIC interaction tagger signal

PDU: 1248

RDO: 1248

RDO: 1248

FEB: 4992

1 link from central ePIC [clock/trigger]

ePIC interaction tagger signal

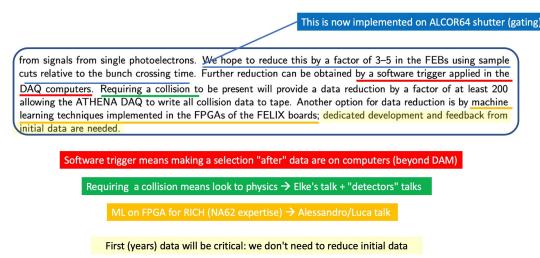

Feasibility studies for an interaction tagger are ongoing providing a factor 100-200 reduction reducing throughput out of DAM (PCI memory) to:

6,84 Gbps - 70 Mbps

A 2 ms latency requires less than 1 MB buffering capacity in each DAM

June 10, 2024

DAQ PDR

7

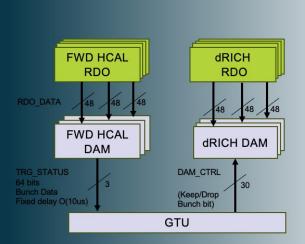

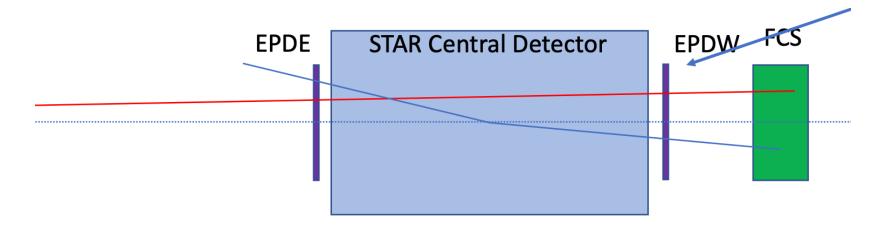

#### Trigger Example: (dRICH tag based on external detector)

Given the requirement for a backup triggered readout for RICH, it is necessary to carefully define the physics trigge rate, trigger conditions, and trigger latency in order to facilitate design of the RICH front-end.

ePIC depends upon a flexible scheme in which sufficient bandwidth is available for data to the dRICH DAM in the worst case. (> 4x safety). The selecting detectors (ex FWD HCAL) generate information characterizing beam in O(10us). The decision is made by the GTU and returned to DAM boards with fixed latency. The maximum latency is orders of magnitudes less than available buffering in DAM board memory. A hardware trigger is supported by the GTU but uses the same dRICH buffering scheme and delays as the firmware trigger option.

| Activity                      | Notes                                                                  |  |  |

|-------------------------------|------------------------------------------------------------------------|--|--|

| Data Arrives at DAMs          | <=10us from Bunch Crossing                                             |  |  |

| Data Evaluation in HCAL DAMs  | 100ns                                                                  |  |  |

| TRG_STATUS to GTU             | Data transmitted to GTU after fixed delay from source crossing O(10us) |  |  |

| Trigger Evaluation on GTU     | Fixed Latency O(100ns)                                                 |  |  |

| Keep/Drop Bit to (dRICH) DAMs | Fixed Latency O(40ns)                                                  |  |  |

| Drop data / forward data      | Drop/Forward after fixed time O(11us)                                  |  |  |

| DAM Buffer                    | 16GB                                                                   |  |  |

| Buffer Time available         | 2.6 seconds                                                            |  |  |

Ex: HCal generates trigger dRICH is triggered

Interaction Tagger Workfest

via GTU triggers info will be distributed to detectors

Example with FHCal, but the scheme is flexible:

- other detectors

- something originating from dRICH itself

- a combination (OR/AND) of the above

It does, no problem.

7/26/2024

### a dRICH track tagger?

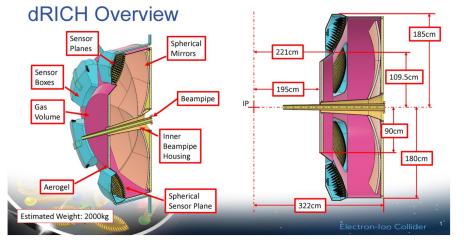

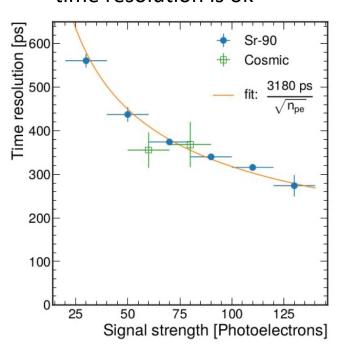

A dRICH Interaction Tagger (dIT) integrated into the dRICH based on plastic scintillators that provide a prompt and fast signal (position-sensitive) of hadrons crossing the dRICH volume

(note: in Marco's slides this proposal is called dRICH Interaxtion Tagger but during the meeting we rebaptized it dRICH Track Tagger = dTT)

Just in front of aerogel window within dRICH envelope, using dRICH readout

#### dIT preliminary design

- Presented estimates of background (it seems manageable)

- similar to STAR/sPHENIX event plane detector (speak with Rosi!)

- Simulation + miniprototypes tests + tiles/fiber optimization + engineering checks neeeded

- Results by ePIC July 2025 (option could be mentioned in pre-TDR)

promising idea, obvioulys must be validated by studies. DAQ likes it "seems robust and close the thing")

- The signal/bg rate is not uniform on dRICH front face (larger in the central region)

- Preliminary ideas include:

- a grid of V and H SciFi at 90°

- a grid of diagonal 60 ° SciFi

- small (~1x1 cm<sup>2</sup>) in the central region and large (~10x10 cm<sup>2</sup>) in the peripheral region plastic scintillator tiles

- 2 layers, 1000 SciFi, 2 m long, and 0.5 cm ∅;

- SciFi:

- attenuation length ~ 4 m

- time rising edge ~ 100 ps

- hit duration ~ 10-20 ns

- SciFi optical coupled with SiPMs cabled to RDOs;

- Two-sides readout → 4k SiPMs & 4k channels (dRICH 320k channels)

- 256 channels for RDO → need to add 16 RDOs

- Cost estimate: ~ \$150k

dRICH Interaction Tagger (dIT)

## dRICH data filtering

### Design Ideas for an Online Data Reduction System for the ePIC dRICH Detector

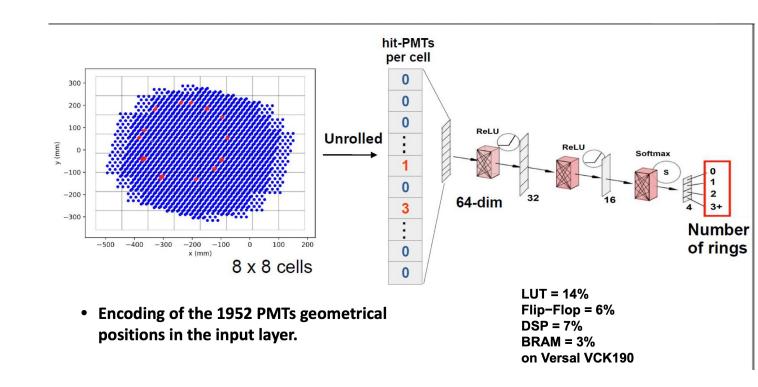

Extensive experience from INFN RM and INFN RM-TV on algorithms deployed on FPGA and GPU RICH know-how from NA62 pattern recognition (NN on FPGA)

The groups are working on simulated dRICH data, a tagger signal would complement their work (as extra-input to seed reconstruction

# dRICH data filtering (2)

#### dRICH Data Reduction Stage on FPGA: example deployment

100 GbE+GPU based scheme

#### From HPC to HEP: NaNet Project

NaNet architecture

NaNet: Design and implementation of a family of FPGA-based PCIe Network Interface Cards:

- Bridging the front-end electronics and the software trigger computing nodes.

- Supporting multiple link technologies and network protocols.

- Optimizing data transfers with GPU accelerators.

- Enabling a low and stable communication latency.

- Having a high bandwidth.

- Processing data streams from detectors on the fly (data compression/decompression and re-formatting, coalescing of event fragments, ...).

| Physical Link   APPlint   THE   General   Ge   | PCIe                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Router To limit St State Curry To St | APEnet+  CPU Chaper — GPU GPU MXX |

| PCIe X8 Gen2 core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |

| CPU+GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   |

| CDII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PICH gaparated primitives         |

|                          | NAG2 A               | <b>○</b> KM3NeT     | NAG2 A              |                     |

|--------------------------|----------------------|---------------------|---------------------|---------------------|

| 1                        | NaNet-1              | NaNet <sup>3</sup>  | NaNet-10            | NaNet-40            |

| Year                     | Q3 - 2013            | Q1 - 2015           | Q2 - 2016           | Q3 - 2019           |

| Device Family            | Altera<br>Stratix IV | Altera<br>Stratix V | Altera<br>Stratix V | Altera<br>Stratix V |

| Channel Technology       | 1 GbE                | KM3link             | 10 GbE              | 40 GbE              |

| Transmission Protocol    | UDP                  | TDM                 | UDP                 | UDP                 |

| Number of Channel        | 1                    | 4                   | 4*                  | 2                   |

| PCle                     | Gen2 x8              | Gen2 x8             | Gen3 x8**           | Gen3 x8             |

| SoC                      | NO                   | NO                  | NO                  | NO                  |

| High Level Synthesis     | NO                   | NO                  | NO                  | YES                 |

| nVIDIA GPUDIrect<br>RDMA | YES                  | YES                 | YES                 | YES                 |

| Real-time                | Da                   | Da                  | Decomp.             | 2                   |

Studies with simulated data critical to define best solution to deploy

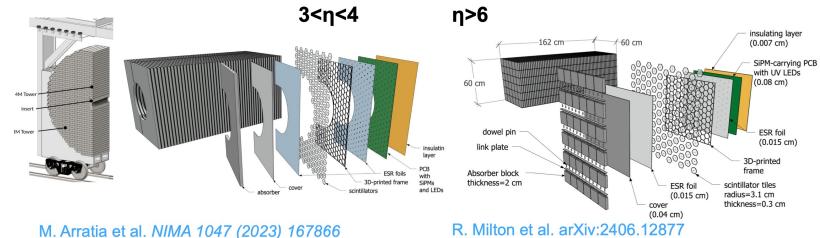

R. Milton et al. arXiv:2406.12877

FHCAL could detect tracks (at MIP level) with high efficiency for dRICH

#### time resolution is ok

FHCAL can play role for both:

- "dRICH track tagging"

- minimum bias interaction trigger

# dRICH track tagger using FEMcal

Talk based on STAR experience (trigger based) and FCS experience Stressed importance of EPD (Event Plane Detector @ STAR/sPHENIX) – dTT has similar design

re-use EPD from STAR not possibile (Elke) but dTT can offer that ("West") FEMCal cannot distinguish between electrons and photons, but still can tag electrons not reaching FHCal

FEMCall can provide further complementing information for dRICH track tagging We will certainly speak with EPD experts to share know how/design ideas tetc.

# Conclusions/Action points

- ✓ No data reduction need at EIC day-0. We will use NONE of all these tools immediately, we will tune taggers and data filtering with real data during EIC first years of operation.

- ✓ The dRICH data throughput is something understood, manageable and we have an array of solutions to handle it

- ✓ an unbiased minimum-bias interaction tagger for ePIC is a wider problem

- get estimates of radiation load during "early EIC Science Program"

- dTT proposal needs to make obviousl scientific due diligence to proof the concept

→ 1 year/in time for TDR

- FHCal / FEMCal need to be quantitative on what they can provide at DAM level to GTU

- data filtering: test algorithms, understand between FPGA / GPU solutions

- we couldn't hear from AC-LGAD TOF due to concurrent TOF workfest. But we will do (note for organizers: FPGA and GPU can work in a highly parallelized way, human beings not.