# dRICH RDO "VTRx+ needs for dRICH"

P. Antonioli for the dRICH sub-system INFN Bologna

Reference: major update about dRICH DAQ at recent last 15 November

## **Outline**

- RDO Overview

- Design elements and miscellanea updates VTRx+ (and RDO) relevant

- VTRx+ update

- Inputs from CMS Padova and ePIC DAQ

- SEU rates + FPGA choice and baseline selections

- Baseline RDO design: VTRx+ integration

- Back-end information & plans

#### RDO: where is inside dRICH?

### **RDO Overview**

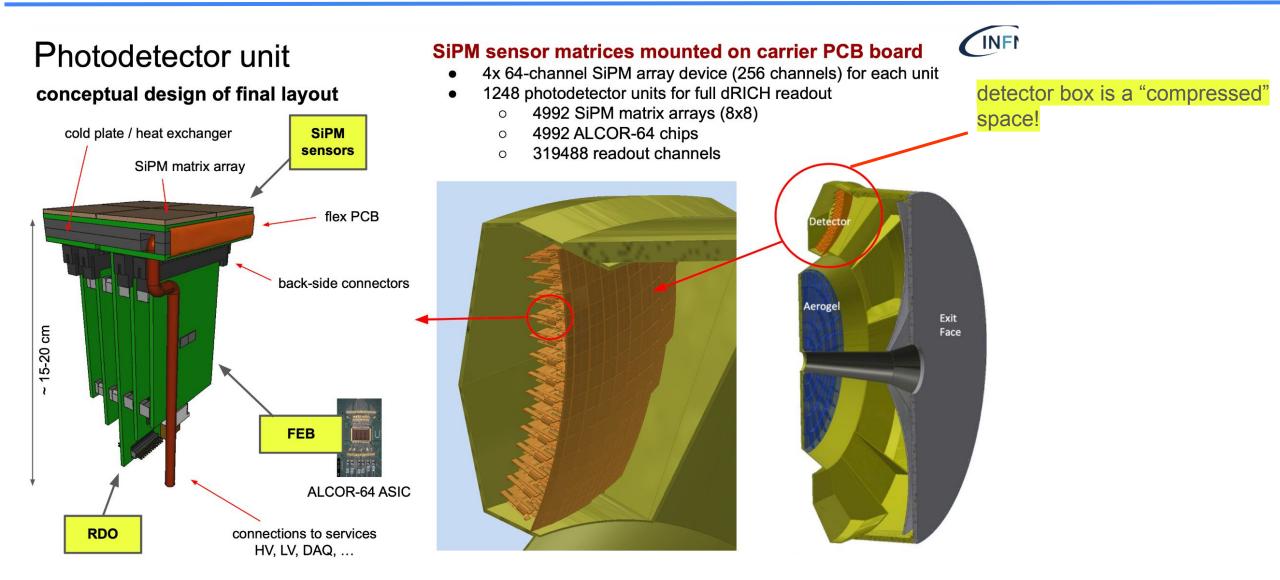

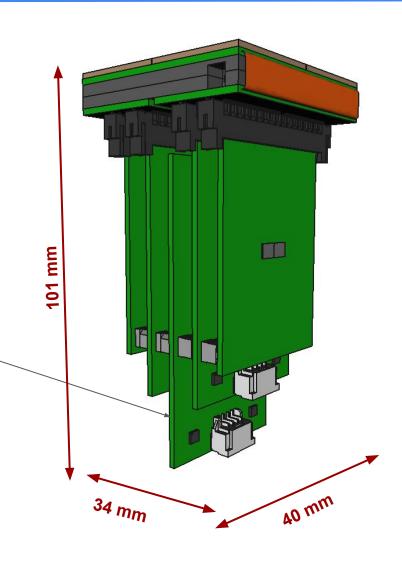

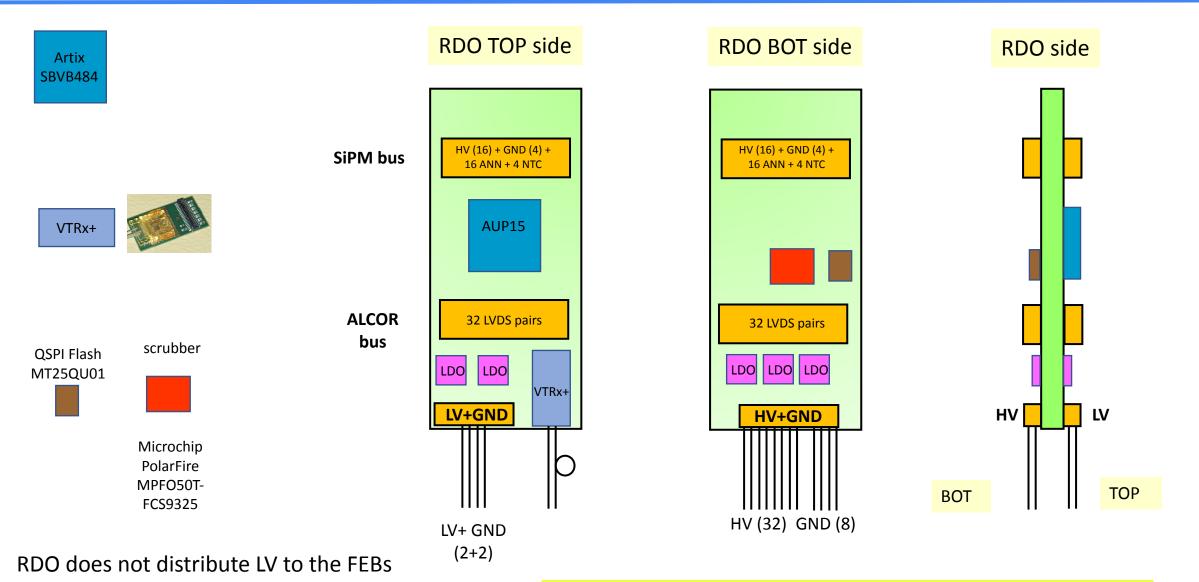

#### RDO is as a component of dRICH PDU

#### basic RDO specs/numbers:

- provide interface to ePIC DAQ

- provide readout/config to 4 ALCOR64

- route HV to SiPM via FEB

- 1 optical link (TX/RX)

- "control" annealing (MOSFET setup)

- services (T sensors, current monitor, ...)

- 4x9 cm<sup>2</sup> surface available

# VTRx+ update

- remember: VTRx+ has a "compact, low-power and rad-tolerant" optical transceiver

- bandwidth: 10 Gbps TX, 2.5 Gbps RX

- requested ePIC/EIC project to prebook 1500 VTRx+ for dRICH: this is total + 20% spares

- ordered via CERN/ALICE 20 VTRx+ for 2024/5 pre-production (pigtail 40 cm length with MTP connector)

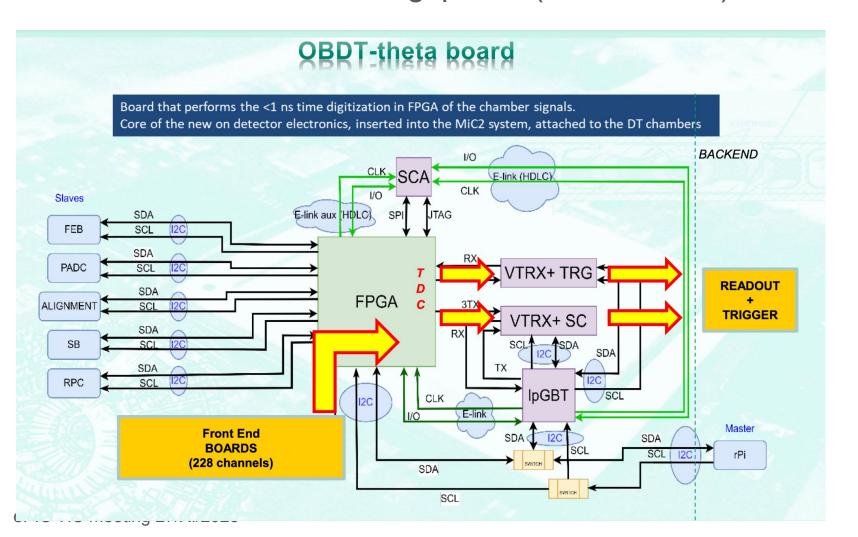

# Input from CMS Padova

CMS Padova realized for Drift Tube chambers readout a card with a Polarfire FPGA without using IpGBT (to send data)

- no problem connecting directly FPGA serializer to VTRX+

- however clock still reconstructed via lpGBT

clock recovery on PolarFire might be challenging

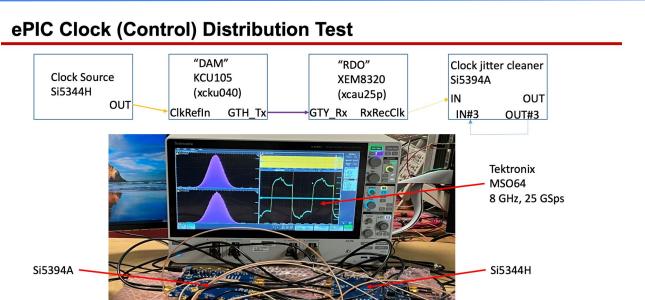

# Input from ePIC timing subgroup

Context: ePIC timing subgroup is a subset of DAQ&Electronics WG

XEM8320

William GU Jefferson Lab

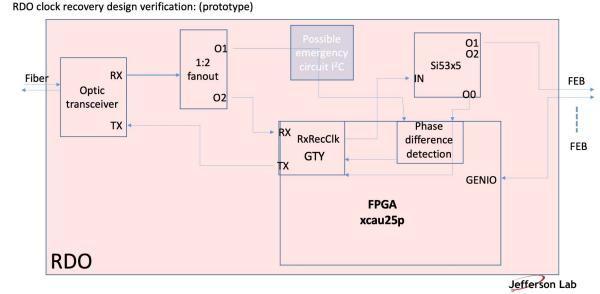

- First tests from W. Gu (JLab)

- J. Schombach (ORNL) testing lpGBT+VTRx+ clock transmissions

- Jo presented recently results using lpGBT+VTRx+ using a frequency equal to % f<sub>FIC</sub> (39.42 MHz)

- ePIC link protocol not yet defined

- default RDO should have ARTIX UltraScale+

- clock multiplier from 98 MHz to 396 MHz to be studied with care

KCU105

## SEU rates + FPGA selection

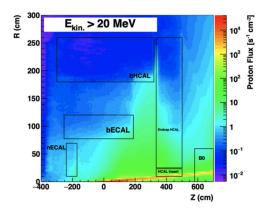

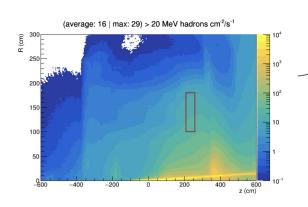

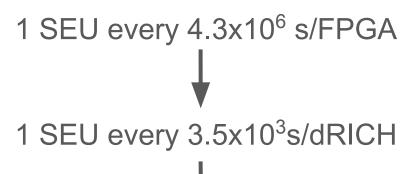

Xilinx <u>declares</u>  $2.67 \times 10^{-16}$  cm<sup>2</sup>/bit cross-section for CRAM bits AUP15 has  $42.8 \times 10^{+6}$  configuration bits dRICH flux (hadrons > 20 MeV): 20 cm<sup>-2</sup>s<sup>-1</sup>

1 SEU every hour in whole dRICH

- SEU rate if confirmed seems manageable

- A scrubber might not be strictly needed

- RDO final design to be validated with a full irradiation test

- Artix Ultrascale+ AU15P-SBVB484 (see backup) good compromise between physical size 1.9x1.9 cm<sup>2</sup>, resources (5.1 Mb RAM), I/O pins (204)

- Smallest available Polarfire (MPF050T) as rad-tolerant scrubber seems effective choice (see later)

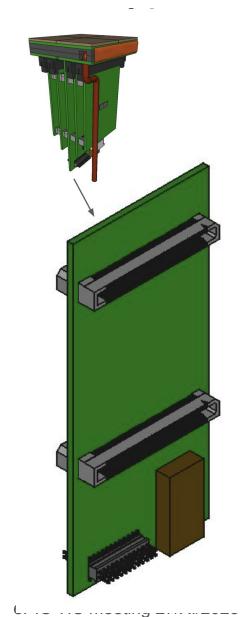

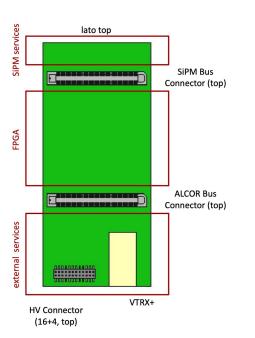

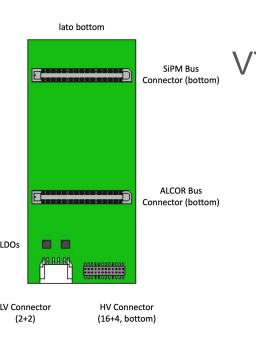

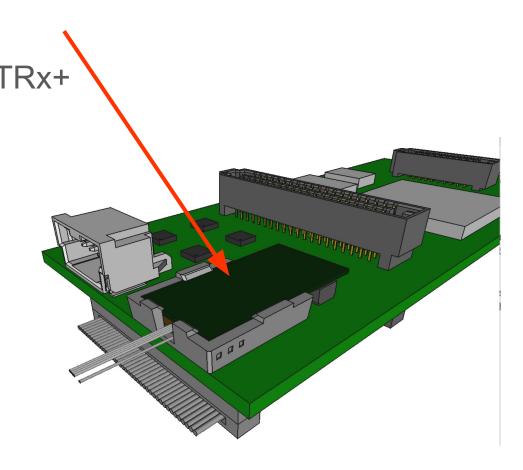

# RDO and VTRx+: how they could look like (I)

# RDO and VTRx+: how they could look like... (II)

- VTRx+ pigtail length and cabling to detector box to be discussed with DAQ group (see talk by <u>J. Huang at DAQ meeting 2 Nov</u>)

- TOF group is developing in 2024 a RDO prototype too. We are in touch and plan is to share expertise (and possibly IP...;-))

### RDO and ePIC DAQ

# dRICH has largest number of RDOs in ePIC

#### **EPIC Detector Scale and Technology Summary:**

| Detector System                                                                                                                                      | Channels                                                                                             | RDO                                         | Gb/s (RDO) | Gb/s (Tape) | DAM Boards | Readout Technology                                                                                                                 | Notes                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|-------------|------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Si Tracking: 3 vertex layers,<br>2 sagitta layers,<br>5 backward disks,<br>5 forward disks                                                           | 7 m^2<br>36B pixels<br>5,200 MAPS sensors                                                            | 400                                         | 26         | 26          | 17         | MAPS:<br>Several flavors:<br>curved its-3 sensors for vertex<br>Its-2 staves / w improvements                                      | Fiber count limited by Artix Transceivers                                                                                                                                                                                                                                             |

| MPGD tracking: Electron Endcap<br>Hadron Endcap<br>Inner Barrel<br>Outer Barrel                                                                      | 16k<br>16k<br>30k<br>140k                                                                            | 8<br>8<br>30<br>72                          | 1          | .2          | 5          | uRWELL / SALSA<br>uRWELL / SALSA<br>MicroMegas / SALSA<br>uRWELL / SALSA                                                           | 64 Channels/Salsa, up to 8 Salsa / FEB&RDO  256 ch/FEB for MM 512 ch/FEB for uRWELL                                                                                                                                                                                                   |

| Forward Calorimeters: LFHCAL HCAL insert* ECAL W/SciFi Barrel Calorimeters: HCAL ECAL SciFi/PB ECAL ASTROPIX Backward Calorimeters: NHCAL ECAL (PWO) | 63,280<br>8k<br>16,000<br>7680<br>5,760<br>500M pixels<br>3,256<br>2852                              | 74<br>9<br>64<br>9<br>32<br>230<br>18<br>12 | 502        | 28          | 19         | SiPM / HG2CROC SiPM / HG2CROC SiPM / Discrete SiPM / HG2CROC SiPM / HG2CROC Astropix SiPM / HG2CROC SiPM / HG2CROC SiPM / Discrete | Assume HGCROC 56 ch * 16 ASIC/RDO = 896 ch/RDO  32 ch/FEB, 16 FEB/RDO estimate, 8 FEB/RDO conserve. HCAL 1536x5  *HCAL insert not in baseline Assume similar structure to its-2 but with sensors with 250k pixels for RDO calculation. 24 ch/feb, 8 RDO estimate, 23 RDO conservative |

| Far Forward: B0: 3 MAPS layers 1 or 2 AC-LGAD layer 2 Roman Pots 2 Off Momentum ZDC: Crystal Calorimeter 32 Silicon pad layer                        | 300M pixel<br>1M<br>1M (4 x 135k layers x 2 dets)<br>640k (4 x 80k layers x 2 dets)<br>400<br>11,520 | 10<br>30<br>64<br>42<br>10                  | 15         | 8           | 8          | MAPS AC-LGAG / EICROC AC-LGAD / EICROC AC-LGAD / EICROC APD HGCROC as per ALICE FoCal-E                                            | 3x20cmx20cm 600^cm layers (1 or 2 layers) 13 x 26cm layers 9.6 x 22.4cm layers There are alternatives for AC-LGAD using MAPS and low channel count DC-LGAD timing layers                                                                                                              |

| 4 silicon pixel layers<br>2 boxes scintillator                                                                                                       | 160k<br>72 <b>WO</b> Ck                                                                              | (a                                          | lmost      | ) done      | e comi     | municating o                                                                                                                       | IRICH numerology i                                                                                                                                                                                                                                                                    |

| Far Backward: Low Q Tagger 1 Low Q Tagger 2 Low Q Tagger 1+2 Cal 2 x Lumi PS Calorimeter Lumi PS tracker                                             | 1.3M pixels<br>480k pixels<br>700<br>1425/75<br>80M pixels                                           | 12<br>12<br>1<br>1<br>24                    | 150        | 1           | 4          | Timepix4 Timepix4 (SiPM/HG2CROC) / (PMT/FLASH) Timepix4                                                                            |                                                                                                                                                                                                                                                                                       |

| PID-TOF: Barrel<br>Endcap                                                                                                                            | 2.2M<br>5.6 M                                                                                        | 288<br>212                                  | 31         | 1           | 17         | AC-LGAD / EICROC (strip)<br>AC-LGAD / EICROC (pixel)                                                                               | bTOF 128 ch/ASIC, 64 ASIC/RDO<br>eTOF 1024 pixel/ASIC, 24-48 ASIC/RDO (41 ave)                                                                                                                                                                                                        |

| PID-Cherenkov: dRICH                                                                                                                                 | 317,952                                                                                              | 1242                                        | 1240       | 13.5        | 28         | SiPM / ALCOR                                                                                                                       | Worse case after radiation. Includes 30% timing window. Requires further data volume reduction                                                                                                                                                                                        |

| pfRICH<br>DIRC                                                                                                                                       | 69,632<br>69,632                                                                                     | 17<br>24                                    | 24<br>11   | 12.5<br>6   | 1          | HRPPD / EICROC (strip or pixel)<br>HRPPD / EICROC (strip or pixel)                                                                 | software trigger                                                                                                                                                                                                                                                                      |

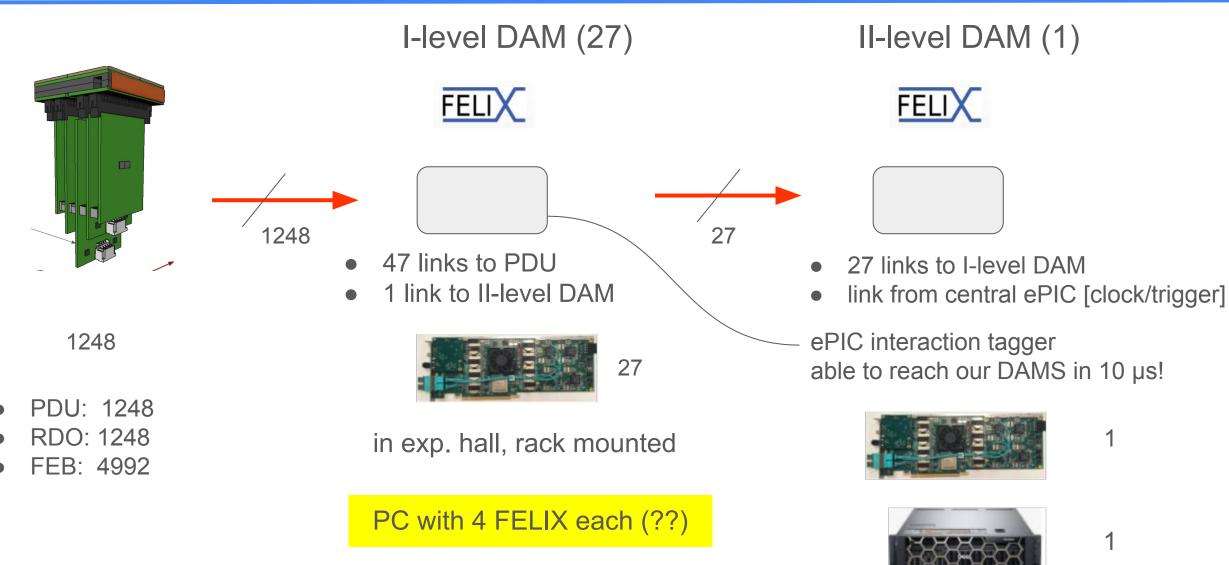

# The big dRICH DAQ plan

| 2024                                                                                                                                                                                                                                                      | 2025                                                                                                                                                                                                                                      | 2026                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>hardware effort</li> <li>RDO prototype as close as possible to final</li> <li>RDO readout of old FEB32 / VTRx+         implementation</li> <li>initial ePIC link test with RDO (clock)</li> <li>input to TDR</li> <li>radiation tests</li> </ul> | <ul> <li>integration with ALCOR64 in the PDU</li> <li>readout with VC709 &amp; ePIC link (including clock)</li> <li>RDO rev. 2 final components</li> <li>possibly test in detector box</li> <li>(likely radiation tests again)</li> </ul> | <ul> <li>FELIX available in ePIC to groups</li> <li>use of DAM (FELIX2)</li> <li>crucial firmware development L1-DAM / L2-DAM</li> </ul> |

| 2027       | 2028     | 2029                                            |

|------------|----------|-------------------------------------------------|

| production | assembly | assembly in-situ DAM deployment + commissioning |

#### in parallel:

- someone has to think/build ePIC interaction tagger

- data reduction/calibration through L2-DAM FPGA or SRO to be integrated

## Conclusions

- ongoing effort toward specifications/requirements for RDO (at 60/70%)

- defined number of VTRX+ needed (1500) [ total + 20% spares ]

- secured VTRx+ sample (20) for early prototypes and defined FPGA baseline

- good liaisons with relevant ePIC "corners" (DAQ group, timing DAQ sub-group, other subsystems working on RDO prototypes...)

- With respect to ePIC, our asks (somehow RDO, VTRx+ and DAQ related)

- ★ need of a final word about securing this pre-booking with CERN

- ★ common mitigation strategy for SEU in RDO Artix Ultrascale+ based?

- ★ RDO design and dRICH DAQ is sustainable as long as we will have an interaction tagger (to be at least partially described in the TDR...)