# Flexible Printed Circuits (FPCs) for ePIC-SVT: An initial configuration

**WP3: Electrical interfaces**

## Objective & outline

#### Objective:

To capture an initial configuration of the Flexible Printed Circuits (FPCs), based on the existing concepts of staves and disks.

The initial configuration will follow the iterations related to the evolutionary development of the SVT.

#### Outline:

- Material budget

- Stave and disk configurations

- Bill of materials

- Layout

- Conclusions

## **Material budget**

| IB | r [mm] | I [mm] | X/X0 % |

|----|--------|--------|--------|

| L0 | 36     | 270    | 0.05   |

| L1 | 48     | 270    | 0.05   |

| L2 | 120    | 270    | 0.05   |

| AS T5 | BARREL  | r [mm] | l [mm] | X/X0 % |

|-------|---------|--------|--------|--------|

|       | Layer 3 | 270    | 540    | 0.25   |

|       | Layer 4 | 420    | 840    | 0.55   |

| DISKS  | +z [mm] | -z [mm] | r_out [mm] | X/X0 % |

|--------|---------|---------|------------|--------|

| Disk 0 | 250     | -250    | 240        | 0.25   |

| Disk 1 | 450     | -450    | 420        | 0.25   |

| Disk 2 | 700     | -650    | 420        | 0.25   |

| Disk 3 | 1000    | -850    | 420        | 0.25   |

| Disk 4 | 1350    | -1050   | 420        | 0.25   |

J. Glover Current and future tracking and vertexing detectors

7 Nov 2023

Table 4.1: Estimated contributions of the Inner Layer Stave to the material budget.

| Stave element | Component             | Material      | Thickness $(\mu m)$ | $X_0$ (cm) | $X_0$ $(\%)$ |

|---------------|-----------------------|---------------|---------------------|------------|--------------|

| HIC           | FPC Metal layers      | Aluminium     | 50                  | 8.896      | 0.056        |

|               | FPC Insulating layers | Polyimide     | 100                 | 28.41      | 0.035        |

|               | Pixel Chip            | Silicon       | 50                  | 9.369      | 0.053        |

| Cold Plate    |                       | Carbon fleece | 40                  | 106.80     | 0.004        |

|               |                       | Carbon paper  | 30                  | 26.56      | 0.011        |

|               | Cooling tube wall     | Polyimide     | 25                  | 28.41      | 0.003        |

|               | Cooling fluid         | Water         |                     | 35.76      | 0.032        |

|               | Carbon plate          | Carbon fibre  | 70                  | 26.08      | 0.027        |

|               | Glue                  | Eccobond 45   | 100                 | 44.37      | 0.023        |

| Space Frame   |                       | Carbon rowing |                     |            | 0.018        |

| Total         |                       |               |                     |            | 0.262        |

ITS2 IB stave length ~270mm, width ~1.5cm, ALPIDE PWR <40m W/cm2

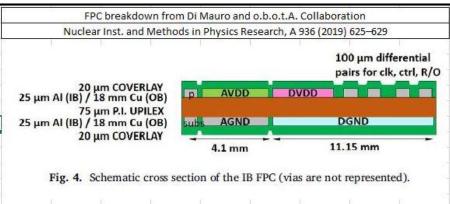

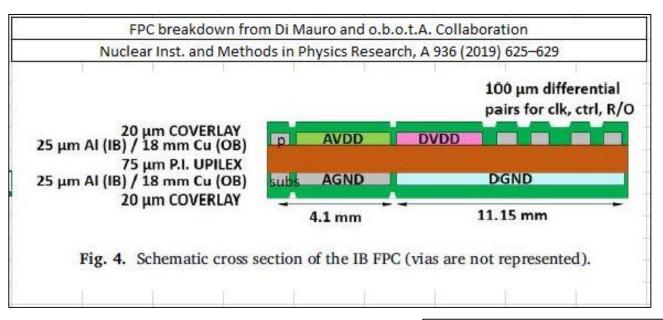

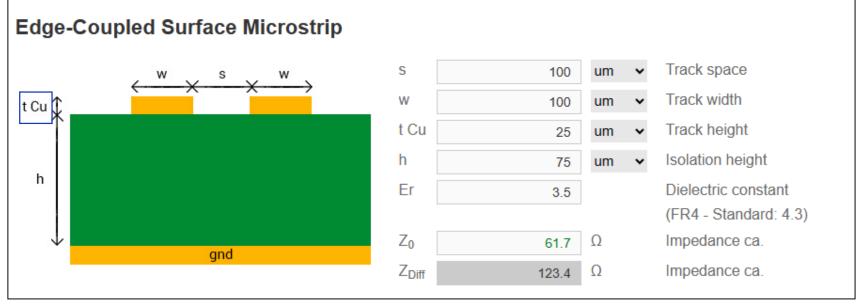

Two layers FPC, w Al tracks, w impedance matched tracks

## Material budget & impedance matching

Sanity check on impedance

OK ~100 ohm impedance for 100um diff pairs

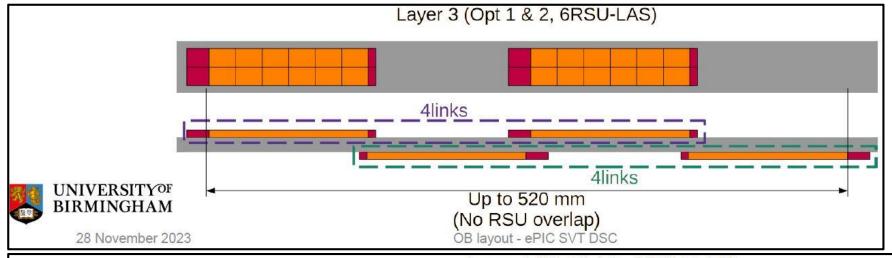

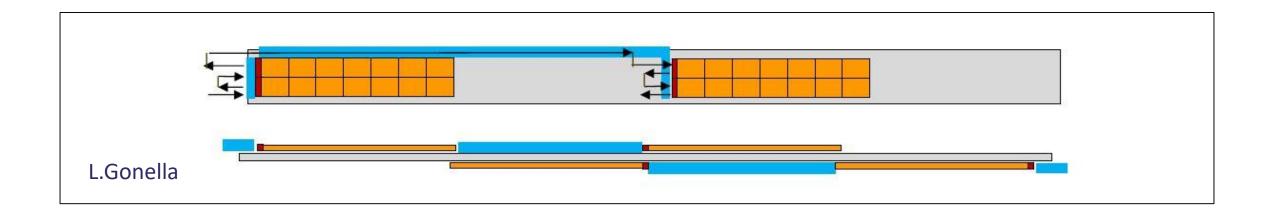

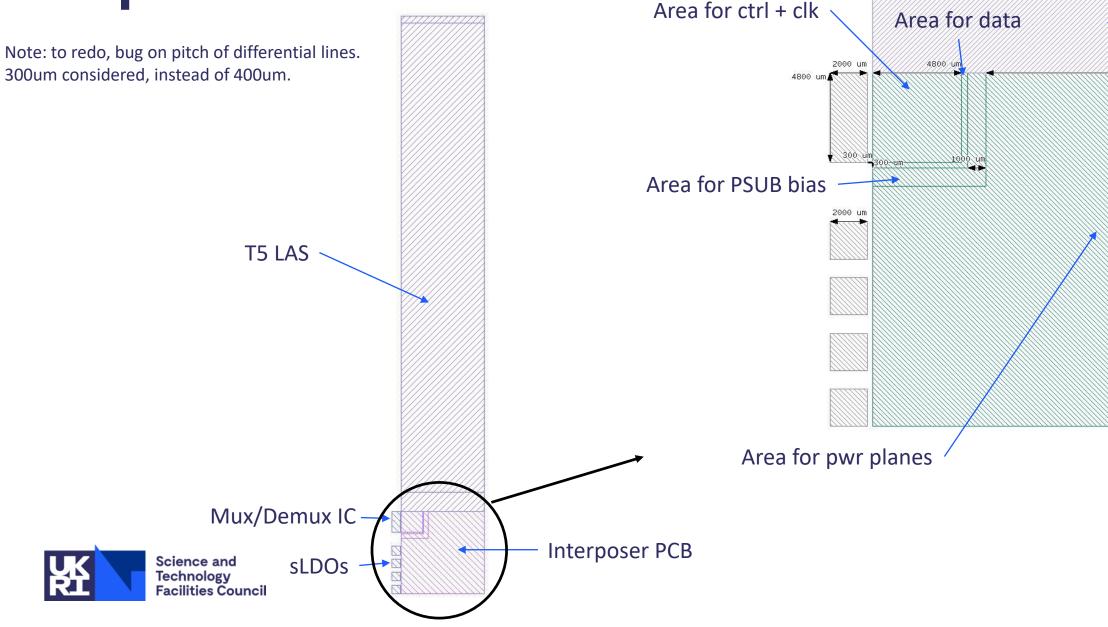

## Stave configuration

#### Assumptions:

- Sensor mounted on top and bottom of cold plate;

- LEC overlaps REC;

- Services from left and right sides of staves

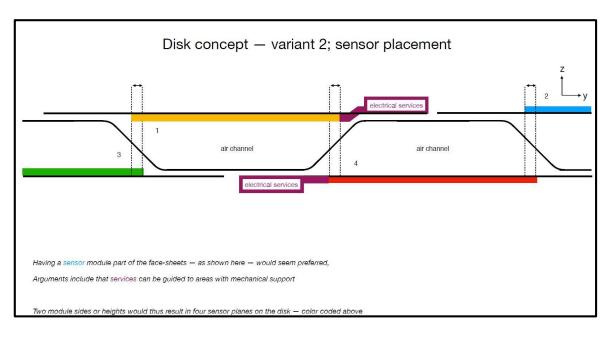

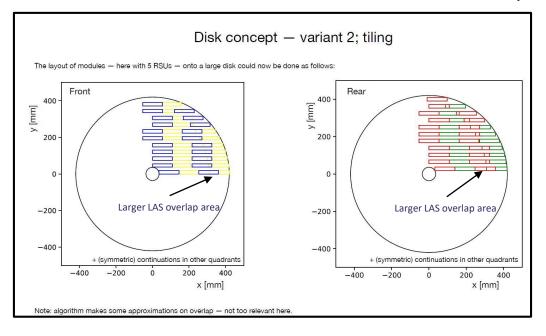

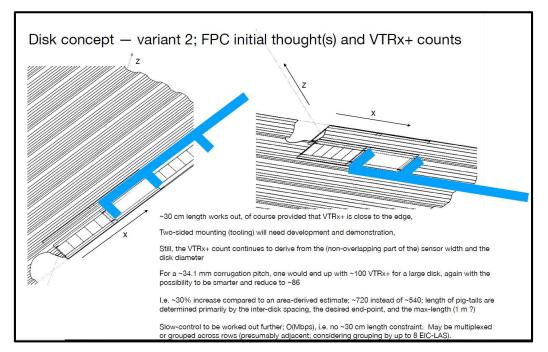

## Disk configuration

#### Note:

Only T5 LAS considered for tiling disks;

LEC overlaps REC like in barrels to increase hermeticity;

#### Credit E.Sichtermann, N.Apadula

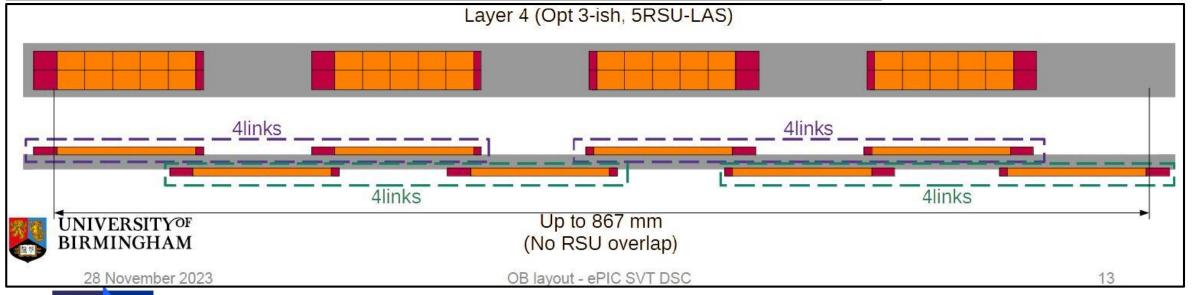

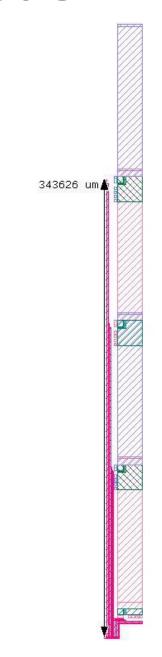

## Case study: OB L4 half stave

OB L4 half stave:

A sequence of 4 T5 LAS, the longest chain of sensors in SVT

This layout is similar and inspired to that of disks.

## BOM (so far)

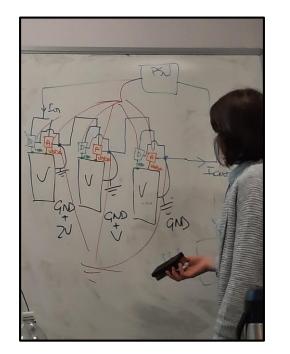

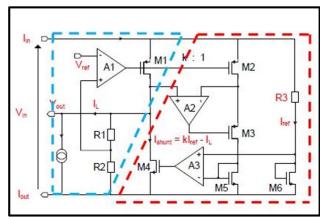

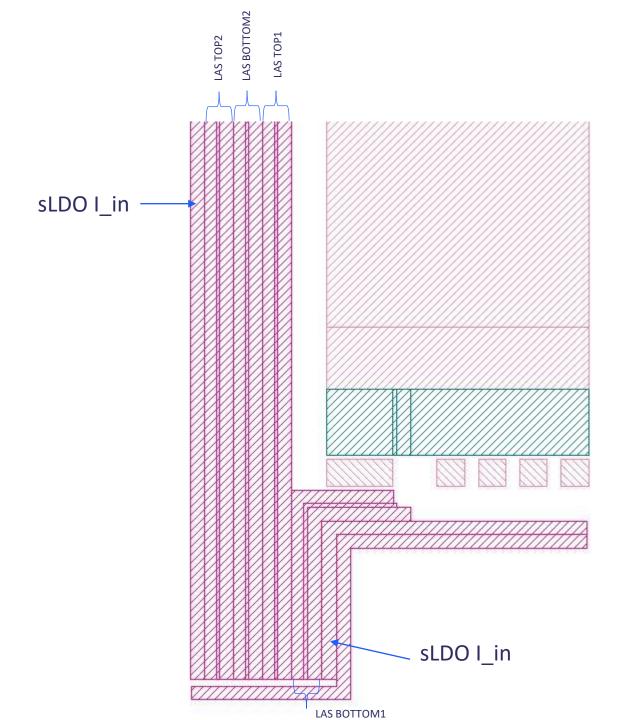

## sLDO: notes

#### "My datasheet

Pin-out description

|      | Signal |        |                                                                                                                                                                                                                     |

|------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | I_in   | input  | 2.5 A (or 1.7 A) (Id+ Ia) worst case scenario                                                                                                                                                                       |

|      | I_out  | input  | 2.5 A (or 1.7 A) (Id+ Ia) worst case scenario                                                                                                                                                                       |

| SLDO | Vout   | output | 4 options:  SDVDD/SDVSS = 1.2 to 1.32 V (services) (227mA)  GAVDD/GAVSS = 1.2 to 1.32 V (global analogue) (540mA)  GDVDD/GDVSS = 1.2 to 1.32 V (global digital) (1369mA)  TXVDD/TXVSS = 1.8 V (serialisers) (200mA) |

|      |        |        | Note: PSUB -1.2 to 0 V not included                                                                                                                                                                                 |

#### Physical layout

| I_in       |         | I_out |

|------------|---------|-------|

|            |         |       |

|            |         | Vout  |

|            |         |       |

| foot print | 2mmx2mm |       |

#### Assuming 4 sLDOs need per LAS

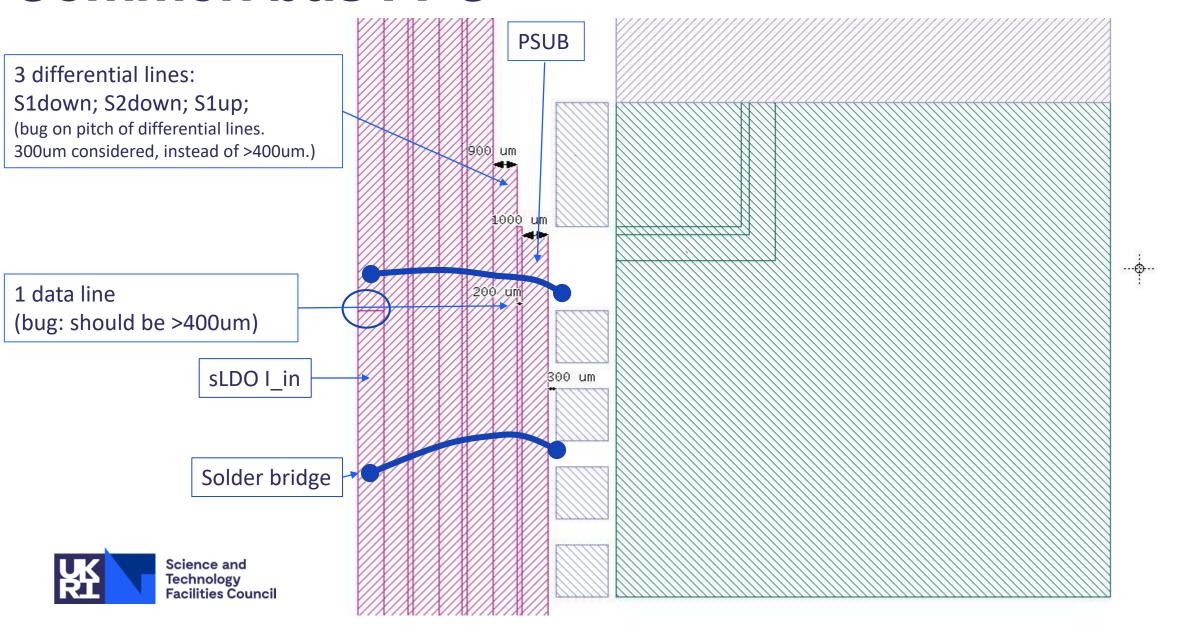

## Mux/Demux IC: notes

Assuming 1 Mux/Demux IC need per LAS

Assuming that it is Pwr'd via one of the existing sLDOs

#### "My datasheet"

#### Pin-out description

|              | S1down+            | Input            | down     | 1 CONTROL link (down) carries MUX'd:<br>(PMWR, SCWR, RST, SYNC) |

|--------------|--------------------|------------------|----------|-----------------------------------------------------------------|

|              | S1down-            | Input            | down     | (FIVIVIR, SCWIR, RST, STIVE)                                    |

|              | 31dOWII-           | IIIput           | uowii    | 1 link for GCLK                                                 |

|              | S2down+            | Input            | down     | Assuming that global clock gets buffered                        |

|              | S2down-            | Input            | down     | Assuming that global clock gets burrered                        |

|              | 3200W11-           | IIIput           | uowii    | 1 Ctrl link (up) carries MUX'd                                  |

|              | C1                 | Outnut           |          | PMRD(up) and SCRD(up)                                           |

|              | S1up+<br>S1up-     | Output<br>Output | up<br>up | PIVIKD(up) and SCRD(up)                                         |

|              | S GLCK+            | Output           | down     | 160MHz (or 320MHz)                                              |

|              | _                  |                  | down     | 100IVINZ (OT 320IVINZ)                                          |

|              | S_GLCK-<br>S_PMWR+ | Output           | down     | EMbas (10Mbas)                                                  |

|              | _                  | Output           |          | 5Mbps (10Mbps)                                                  |

|              | S_PMWR-            | Output           | down     | 58 db (408 db)                                                  |

| slowCtrlChip | S_PMRD+            | Input            | up       | 5Mbps (10Mbps)                                                  |

| siowctriciip | _                  | Input            | up       | F8 dl (4 O8 dl )                                                |

|              | S_SCWR+            | Output           | down     | 5Mbps (10Mbps)                                                  |

|              | S_SCWR-            | Output           | down     |                                                                 |

|              | S_SCRD+            | Input            | up       | 5Mbps (10Mbps)                                                  |

|              | S_SCRD-            | Input            | up       |                                                                 |

|              | S_GRST+            | Output           | down     |                                                                 |

|              | S_GRST-            | Output           | down     |                                                                 |

|              | G_SYNC+            | Output           | down     |                                                                 |

|              | G_SYNC-            | Output           | down     |                                                                 |

|              | G_RESERVE+         | N/A              | N/A      |                                                                 |

|              | G_RESERVE-         | N/A              | N/A      |                                                                 |

|              |                    |                  |          | supplied locally from sLDO                                      |

|              |                    |                  |          | multiple pads                                                   |

|              | VDD                | Input            |          | Supply voltage and power?                                       |

|              | GND                | Input            |          |                                                                 |

#### Physical layout

|                  | To/From IpGBP | T                 | To/From LAS |

|------------------|---------------|-------------------|-------------|

|                  | S1down+       |                   | S_GLCK+     |

|                  | S1down-       |                   | S_GLCK-     |

|                  | S2down+       |                   | S_PMWR+     |

|                  | S2down-       |                   | S_PMWR-     |

|                  | S1up+         |                   | S_PMRD+     |

|                  | S1up-         | 4                 | S_PMRD-     |

| From local sLDO  | VDD           |                   | S_SCWR+     |

| FIOIIIIOCAI SEDO | GND           |                   | S_SCWR-     |

|                  |               |                   | S_SCRD+     |

|                  |               |                   | S_SCRD-     |

|                  |               |                   | S_GRST+     |

|                  |               |                   | S_GRST-     |

|                  |               |                   | S_SYNC+     |

|                  |               |                   | S_SYNC-     |

|                  | foot print    | 4800 mm x 2000 mm |             |

## LAS: notes

Assuming LAS is T5 only

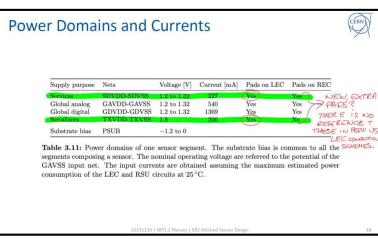

#### **Power Domains and Currents**

| Nets        | Voltage [V]                                              | Current [mA] | Pads on LEC                                                                                                                                                                                            | Pads                                                                                                                                                                                                                                                   | on REC                                                                                                                                                                                                                                                                                                |

|-------------|----------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDVDD-SDVSS | 1.2 to 1.32                                              | 227          | Yes                                                                                                                                                                                                    | Yes                                                                                                                                                                                                                                                    | NEW, EXTRE                                                                                                                                                                                                                                                                                            |

| GAVDD-GAVSS | 1.2 to 1.32                                              | 540          | Yes                                                                                                                                                                                                    | Yes                                                                                                                                                                                                                                                    | >7 PAPS?                                                                                                                                                                                                                                                                                              |

| GDVDD-GDVSS | 1.2 to 1.32                                              | 1369         | Yes                                                                                                                                                                                                    | Yes                                                                                                                                                                                                                                                    | THERE IS NO                                                                                                                                                                                                                                                                                           |

| TXVDD-TXVSS | 1.8                                                      | 200          | Yes                                                                                                                                                                                                    | No                                                                                                                                                                                                                                                     | RETERENCE T                                                                                                                                                                                                                                                                                           |

| PSUB        | -1.2  to  0                                              |              | _                                                                                                                                                                                                      |                                                                                                                                                                                                                                                        | THESE IN PREVIOU                                                                                                                                                                                                                                                                                      |

|             | SDVDD-SDVSS<br>GAVDD-GAVSS<br>GDVDD-GDVSS<br>TXVDD-TXVSS | SDVDD-SDVSS  | SDVDD-SDVSS         1,2 to 1,32         227           GAVDD-GAVSS         1,2 to 1,32         540           GDVDD-GDVSS         1,2 to 1,32         1369           TXVDD-TXVSS         1,8         200 | SDVDD-SDVSS         1.2 to 1.32         227         Yes           GAVDD-GAVSS         1.2 to 1.32         540         Yes           GDVDD-GDVSS         1.2 to 1.32         1369         Yes           TXVDD-TXVSS         1.8         200         Yes | SDVDD-SDVSS         1.2 to 1.32         227         Yes         Yes           GAVDD-GAVSS         1.2 to 1.32         540         Yes         Yes           GDVDD-GDVSS         1.2 to 1.32         1369         Yes         Yes           TXVDD-TXVSS         1.8         200         Yes         No |

Table 3.11: Power domains of one sensor segment. The substrate bias is common to all the SCHEMES. segments composing a sensor. The nominal operating voltage are referred to the potential of the GAVSS input net. The input currents are obtained assuming the maximum estimated power consumption of the LEC and RSU circuits at 25 °C.

20231120 | WP1.2 Plenary | ER2 Stitched Sensor Design

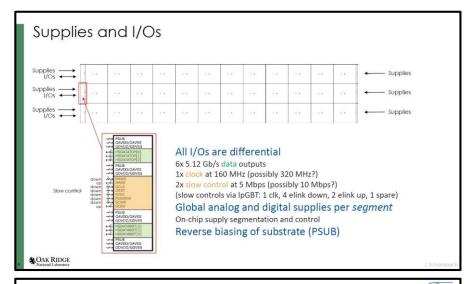

#### "My datasheet"

#### Pin-out description

|     | S_GLCK+    | Input  | down | 160MHz (or 320MHz)                      | Clk         |

|-----|------------|--------|------|-----------------------------------------|-------------|

|     | S_GLCK-    | Input  | down |                                         | CIK         |

|     | S_PMWR+    | Input  | down | 5Mbps (10Mbps)                          |             |

|     | S_PMWR-    | Input  | down |                                         |             |

|     | S_PMRD+    | Output | up   | 5Mbps (10Mbps)                          |             |

|     | S_PMRD-    | Output | up   |                                         |             |

|     | S_SCWR+    | Input  | down | 5Mbps (10Mbps)                          |             |

|     | S_SCWR-    | Input  | down |                                         | Slow ctrl   |

|     | S_SCRD+    | Output | up   | 5Mbps (10Mbps)                          | 310W CUI    |

|     | S_SCRD-    | Output | up   |                                         |             |

|     | S_GRST+    | Input  | down |                                         |             |

|     | S_GRST-    | Input  | down |                                         |             |

|     | G_SYNC+    | Input  | down |                                         |             |

| LAS | G_SYNC-    | Input  | down |                                         |             |

|     | G_RESERVE+ | N/A    |      |                                         |             |

|     | G_RESERVE- | N/A    |      |                                         |             |

|     | HSDATA+    | Output | up   | 5.12 Gb/s                               | Data        |

|     | HSDATA-    | Output | up   |                                         | Data        |

|     | SDVDD      | Input  |      | 1.2 to 1.32 V (services) (227mA)        |             |

|     | SDVSS      | Input  |      |                                         |             |

|     | GAVDDS     | Input  |      | 1.2 to 1.32 V (global analogue) (540mA) |             |

|     | GAVSS      | Input  |      |                                         | Pwr         |

|     | GDVDD      | Input  |      | 1.2 to 1.32 V (global digital) (1369mA) | PWI         |

|     | GDVSS      | Input  |      |                                         |             |

|     | TXVDD      | Input  |      | 1.8 V (serialisers) (200mA)             |             |

|     | TXVSS      | Input  |      |                                         |             |

|     | PSUB       | Input  |      |                                         | Sensor bias |

#### Physical layout

|        | l (mm)  | w (mm) |

|--------|---------|--------|

| RSU    | 21.666  | 19.564 |

| LEC    | 4.5     | 19.564 |

| REC    | 1.5     | 19.564 |

| T5 LAS | 114.33  | 19.564 |

| T6 LAS | 135.996 | 19.564 |

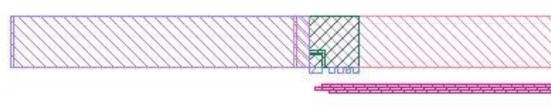

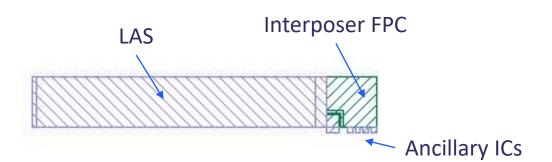

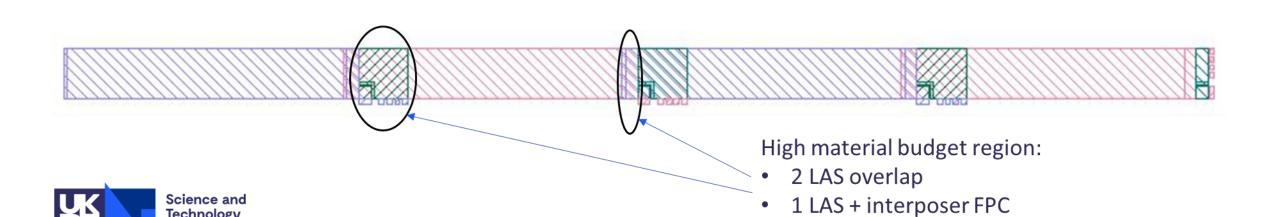

# Layout

## Layout into

Sensors: top only

Sensors: top and bottom

High material budget region:

- 2 LAS overlap

- 1 LAS + interposer FPC

Interposer FPC

**LEC**

12900 um 4500 um

## Interposer FPC: material budget

Technology Facilities Council

|     | Components              | Thickness (um)     | Material      | X0 (cm)                               | X0 (%) | Comment                                             |

|-----|-------------------------|--------------------|---------------|---------------------------------------|--------|-----------------------------------------------------|

|     | FPC metal layers        | 50                 | Al            | 8.897                                 | 0.056  | 25um/layer x 2 layers = 50um                        |

|     | FPC insulating layers 1 | 75                 | UPILEX-S75    | 28.57                                 | 0.026  | UPILEX-S75 is a type of polyimide                   |

| HIC | FPC insulating layers 2 | 40                 | Coverlay      | 28.57                                 | 0.014  | 20um/layer x 2 layers = 40um, coverlay is polyimide |

|     | Pixel Chip              | 50                 | Si            | 9.37                                  | 0.053  |                                                     |

|     | Glue                    | 50                 | Araldite 2011 | 39.07                                 | 0.0128 | ATLAS assumes phenol epoxy C6 H6 O                  |

|     | Total (FPC -            | Pixel chip + glue  |               | 0.163                                 |        |                                                     |

|     | Total w/o glu           | ue (FPC + Pixel ch |               | 0.150                                 |        |                                                     |

|     |                         |                    |               | consider Si interposer as option:     |        |                                                     |

|     | Tot                     | al FPC only        | 0.096         | Si 50um thin equates to X0 (%) 0.053. |        |                                                     |

|     |                         |                    |               |                                       |        | N.B. ~50% saving in material budget                 |

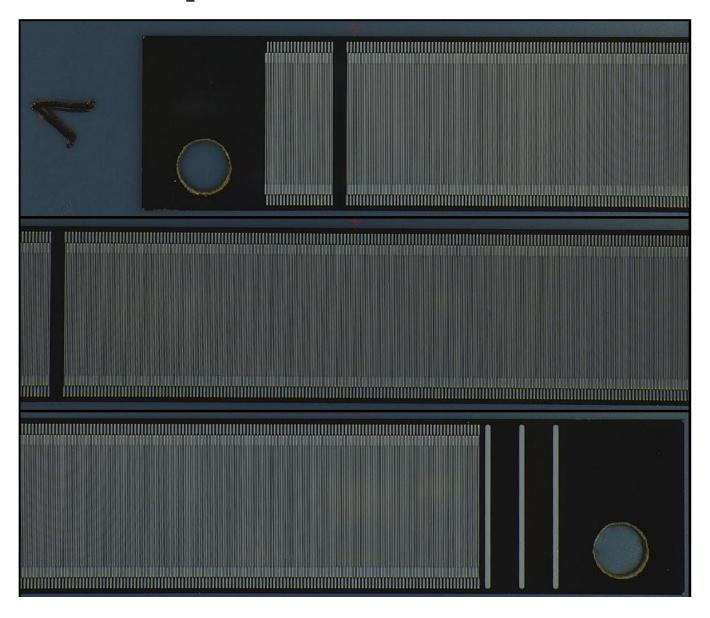

## Si interposer (1 layer): examples

## Common bus FPC

Science and Technology Facilities Council

## Common bus FPC

### Conclusion

• An initial FPC layout has been captured.

L4 half stave configuration was used a case study, representative for disks and staves.

- Improvements required e.g.

- Definition of LAS layout on staves.

## Thank you

**Facebook:** Science and Technology Facilities Council

Twitter: @STFC\_matters

**YouTube:** Science and Technology Facilities Council