## News -12/12/2023

- Incremental Design and Safety Review on ePIC PID detectors conducted on July 5-6:

- Presentations; Review report; answers in prepation (p2/3)

- EIC Project Detector R&D

- FY24 proposals; Decision (p4); contracts in progress

- ePIC TOF Project Engineering Design

- Mechanical engineering: support structure and cooling submitted on June 27: Mechanical PED

- BTOF module prototyping and FBK sensor production in preparation

- ePIC TOF DSC

- Working on schedule and cost, identify institutional responsibilities and L5/L6 contacts (p6-10)

- BTOF: Mathew Gignac/Satoshi Yano/Zhenyu Ye, FTOF: Mathieu Benoit/Wei Li, Common System: Andreas Jung/Zhangbu Xu

- ePIC TOF Simulation

- Updated geometry database on 9/29 Zhenyu: updated in DD4HEP #564 (p11)

- TOF in tracking Nicolas: Re-check FTOF material budget impact

- TOF PID reconstruction Oskar/Zhenyu: reconstruction, validation plots

- TOF digitization Souvik/Adam: charge sharing and detector noise

- TOF service in simulation TBD: implement the missing material for mechanical support structure, cooling and cabling

- ePIC Collaboration meeting at ANL on January 9-13, 2024

- AC-LGAD parallel session (Jan 9-10): <a href="https://indico.bnl.gov/event/20473">https://indico.bnl.gov/event/20473</a>

## News

• Incremental Design and Safety Review on ePIC PID detectors conducted on July 5-6: Review presentations; Final review report

# Detector

## • (AC-LGAD) 35ps Barrel/ 25ps FW timing resolution seems to be almost the best performance without safety margin. Under these circumstances, a bias voltage scheme should be more flexible than only one pair of cables for each board, because the temperature gradient and the position-dependent radiation fluence require different operation voltages.

- Fluence: Wei/XiaoPower for Service

- Hybrid: Tonko/Wei

- Thermal: Yi/Andy

- (AC-LGAD) The type of interconnection to the sensors (like wire bonding or bump bonding) must be clearly specified. If a detector uses a bump bonding connection, we would advise to start testing the flip-chipping process since it takes longer to develop a stable procedure.

- eRD109: ORNL

- eRD112: UIC

- The initial requirements for the EICROC were specified mostly for the Roman Pot detector and not for all detectors which use EICROC. We advise summarizing the BTOF: requirements for all detectors and making a single EICROC specification before FTOF: submitting further prototype chips.

- A specification on the tolerable clock drift and the robustness to phase irregularities should be defined and will help to ensure that these parameters are measured and controlled in the architecture from the beginning of the design phase. The DAQ design should include a backup solution for a directly distributed clock to the RDO boards to provide the clock precision required by each subsystem.

Zhenyu Ye @ UIC

- ✓ Tonko: 5ps jitter

Electronics

12/12/23

## News

• Incremental Design and Safety Review on ePIC PID detectors conducted on July 5-6: Review presentations; Final review report

# Tracking

- Recent progress has been made in ePIC's cross-cutting PID WG to understand tracking requirements for PID detectors. Requirements documents should capture the bi-directional interface between tracking and PID detectors: e.g., translation between extrapolated track impact point and angle resolution requirements for PID detectors. It could be evaluated where the PID subdetectors can contribute to improving the tracking performance and how in the reconstruction algorithms this could be integrated.

- Encouraging track momentum resolution improvement was achieved by including the AC-LGAD in reconstruction. The reviewers suggest extending this study to understand the impact on the extrapolated track impact point and angle at the radius of the DIRC.

#### **Recommendations**

1. Capture the bi-directional interface between tracking and PID detectors: e.g., translation between position and angular resolution requirements for PID detectors.

## AC-LGAD FY24 R&D Proposal

- Optimized sensor design and final prototypes that meet ePIC requirements, including timing and spatial resolution, irradiation tolerance, and reasonably large size for module assembly

- Prototypes of interposer for mechanical/electrical connections between strip sensor and ASIC

- Prototypes of light-weight module mechanical structures for forward TOF

- Prototypes of frontend ASICs

- Functional and full size low-mass Kapton PCB

- Low-cost interconnect for sensor-ASIC hybridization

- Service hybrid prototype

#### eRD112 (414k->286k\$)

- Sensor R&D (346k->261k\$)

- BNL, HPK<del>/FBK</del> productions

- TCAD, lab/beam/irradiation tests

- Sensor/ASIC integration (15k\$)

- Interposer

- Mechanical structure (\$53k)

- Light-weight structure w. cooling

#### eRD109 (435k->390k\$)

- Frontend ASICs

- EICROC (85k\$)

- FCFD (40k\$)

- 3<sup>rd</sup> Party ASICs (45k\$)

- Frontend electronics

- Low-mass Kapton PCB (30k\$)

- Low-cost hybridization (15k)

- Service hybrid (220k)

#### **EPIC Simulation**

- Geometry model, digitization and reconstruction

- Requirements on spatial, timing resolutions, and material budget

#### **Project Engineering Design**

- Engineering design for pre-TDR

- Integration & services

### Sensor Electronics Sensor-ASIC integration Mechanics

8/28/2023 Zhenyu for eRD112

## FY24 Plan

- Simulation

- R&D:

- Sensor: new BNL+HPK production and Characterization, simulation, irradiation

- Sensor-ASIC integration: interposer for BTOF, hybridization for FTOF pixel sensor-ASIC

- ASIC: EICROC0/EICROC1, FCFDv1/v2

- Module PCB: Low-mass flexible Kapton for BTOF

- Module structure: Low-mass CF structure for BTOF module

- Service Hybrid: RDO + Power board

- PED:

- BTOF and FTOF  $(5\%X_0)$  support structure

- BTOF module and FBK production in preparation

- TDR

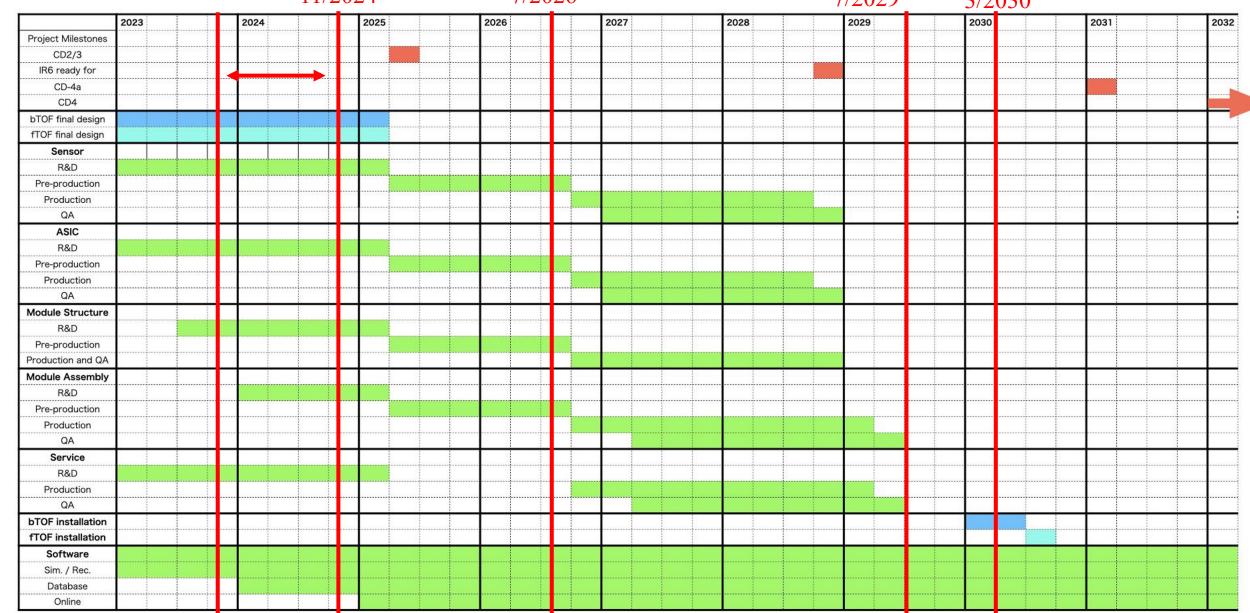

## **Schedule and Timeline**

Prelim Design (70%) Final Design Construction Completed Installation 11/2024 7/2026 7/2029 3/2030

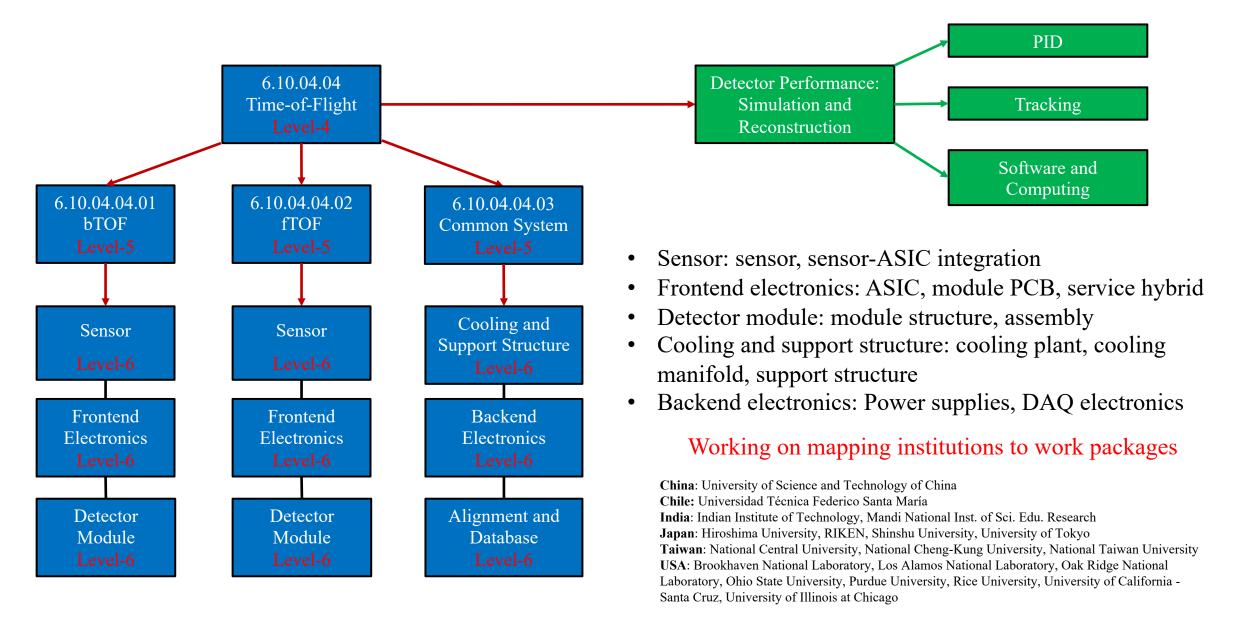

## **Proposed Working Package Structure**

12/12/23 Zhenyu Ye @ UIC

## **Barrel TOF**

| Package                     | Coordinator(s) | Institutions                                    |

|-----------------------------|----------------|-------------------------------------------------|

| Sensor                      |                | UCSC, Hiroshima+Shinshu, (BNL-HEP/IO, UIC/FNAL) |

| Sensor-ASIC integration     |                | UCSC, (ORNL, Hiroshima, UIC)                    |

| Frontend ASIC               |                | (IJCLab/Omega, FNAL), BNL, Hiroshima, (UIC)     |

| Flex Module PCB             |                | ORNL                                            |

| Service Hybrid              |                | BNL, (Rice, UIC)                                |

| Module Mechanical Structure |                | Purdue, NCKU                                    |

| Module Assembly             |                | UCSC. (BNL-HEP/IO. RIKEN)                       |

## **Forward TOF**

| Package                     | Coordinator(s) | Institutions              |

|-----------------------------|----------------|---------------------------|

| Sensor                      |                | ORNL, SCNU                |

| Sensor-ASIC integration     |                | ORNL, (SCNU)              |

| Frontend ASIC               |                | (IJCLab/Omega), BNL, ORNL |

| Flex Module PCB             |                | Rice, ORNL                |

| Service Hybrid              |                | Rice                      |

| Module Mechanical Structure |                | Purdue, NCKU              |

| Module Assembly             |                | LANL, ORNL, (RIKEN)       |

## **Common System**

| Package                      | Coordinator(s)                     | Institutions     |

|------------------------------|------------------------------------|------------------|

| Support Structure            |                                    | Purdue, NCKU     |

| Cooling System and Manifolds |                                    |                  |

| Patch Panel and Cables       | Zhangbu Xu + Tim Camarda (BNL/KSU) | EIC project, KSU |

| LV Power Supplies            | Zhangbu Xu + Tim Camarda (BNL/KSU) | EIC project, KSU |

| HV Power Supplies            | Zhangbu Xu (BNL/KSU)               | EIC project, KSU |

| Timing/DAQ System            | Tonko Ljubicic (BNL)               | EIC project, BNL |

| Alignment and Database       |                                    |                  |

## Change in TOF Geometries

https://github.com/eic/epic/issues/564

- BTOF

- Envelope in geometry DB: R=(56, 63), z=(-117.5, 171.5) cm

- DD4HEP old: R=(63, 66), Z=(-120, 120) cm

- DD4HEP new: R = (60, 63), Z = (-117.5, 162.5) cm

- FTOF

- Envelope in geometry DB: R=(8, 60), z=(180, 195) cm

- DD4HEP old: R=(8, 67), Z=(180, 195) cm

- DD4HEP new: R = (8, 57.5), Z = (180, 195) cm