### dRICH DAQ Short summary for SRO meeting

<u>P. Antonioli</u> for the dRICH DSC, INFN Bologna

Reference: DAQ update at dRICH meeting was last 15 Nov

Outline

- Brief dRICH RDO overview in dRICH PDU

- Baseline RDO design

- DAQ throughput modelling

Trying to give some additional input/info following discussions @ANL

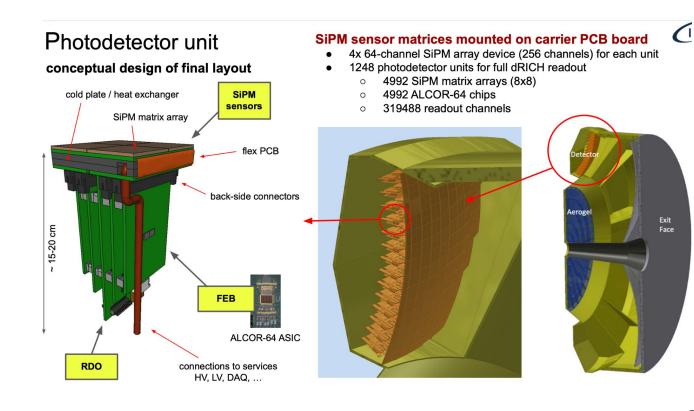

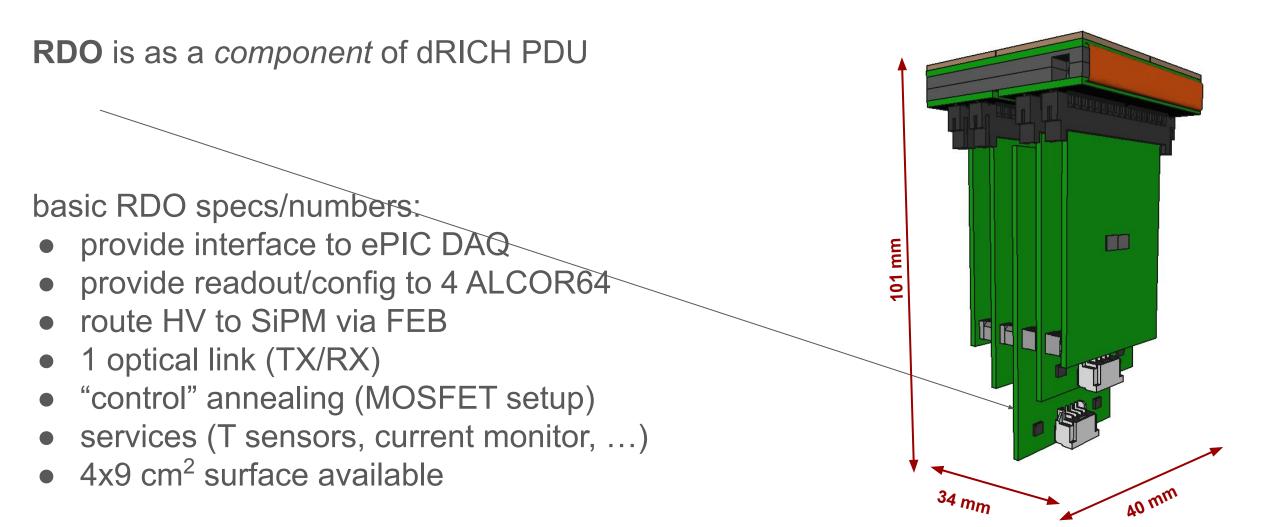

# dRICH RDO Overview

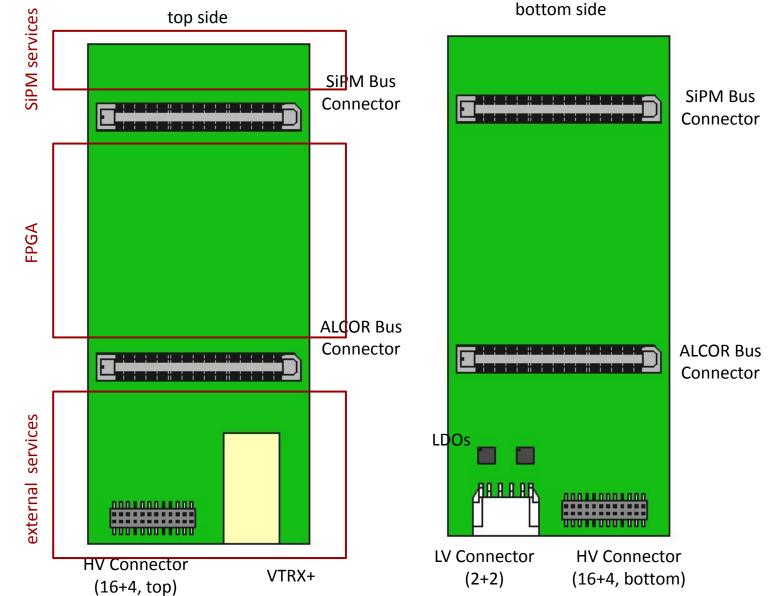

Need of high integration with challenging space constraints→ "custom" RDO

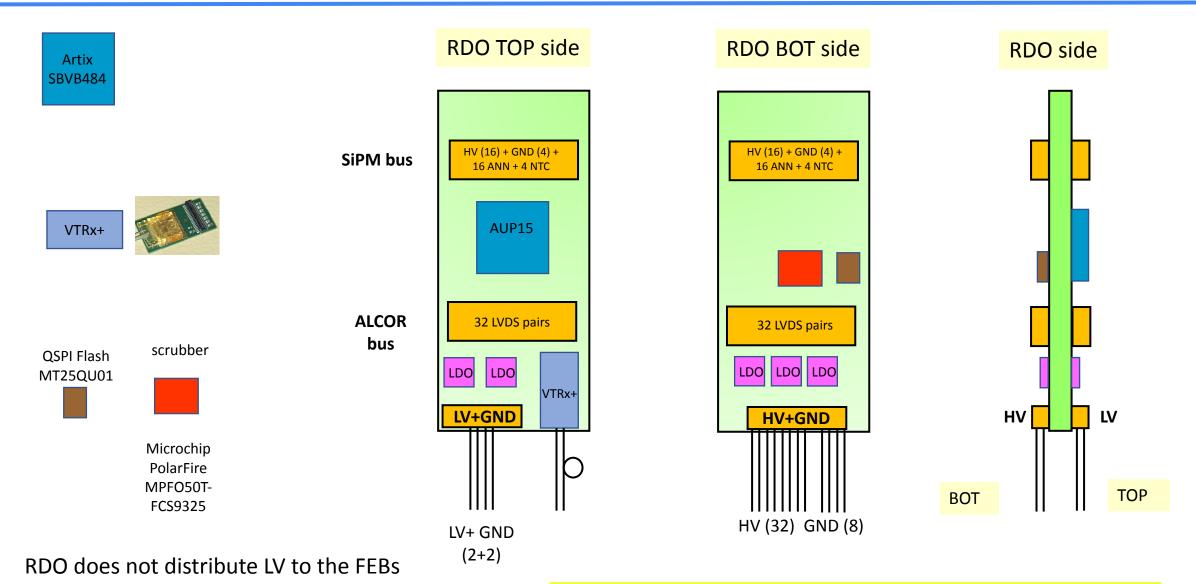

# RDO Baseline (I)

4

components on scale excluding connectors

### RDO baseline (II)

- 14-16 layers min

- HV in shielded middle-layer"!

- engineers at work on schematics

preferred clock to be received: 98.5 MHz, we aim ALCOR@396 MHz using SkyWOrks Si5236

### RDO and ePIC DAQ

### dRICH has largest number of RDOs in ePIC

#### EPIC Detector Scale and Technology Summary:

| Detector System                                                                                                                                                                                | Channels                                                                                                           | RDO                                         | Gb/s (RDO) | Gb/s (Tape) | DAM Boards | Readout Technology                                                                                                                       | Notes                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|-------------|------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Si Tracking: 3 vertex layers,<br>2 sagitta layers,<br>5 backward disks,<br>5 forward disks                                                                                                     | 7 m <sup>2</sup><br>36B pixels<br>5,200 MAPS sensors                                                               | 400                                         | 26         | 26          | 17         | MAPS:<br>Several flavors:<br>curved its-3 sensors for vertex<br>Its-2 staves / w improvements                                            | Fiber count limited by Artix Transceivers                                                                                                                                                                                                                                                             |

| MPGD tracking: Electron Endcap<br>Hadron Endcap<br>Inner Barrel<br>Outer Barrel                                                                                                                | 16k<br>16k<br>30k<br>140k                                                                                          | 8<br>8<br>30<br>72                          | 1          | .2          | 5          | uRWELL / SALSA<br>uRWELL / SALSA<br>MicroMegas / SALSA<br>uRWELL / SALSA                                                                 | 64 Channels/Salsa, up to 8 Salsa / FEB&RDO<br>256 ch/FEB for MM<br>512 ch/FEB for uRWELL                                                                                                                                                                                                              |

| Forward Calorimeters:<br>LFHCAL<br>HCAL insert*<br>ECAL W/SciFi<br>Barrel Calorimeters:<br>HCAL<br>ECAL SciFi/PB<br>ECAL ASTROPIX<br>Backward Calorimeters:<br>NHCAL<br>ECAL (PWO)             | 63,280<br>8k<br>16,000<br>7680<br>5,760<br>500M pixels<br>3,256<br>2852                                            | 74<br>9<br>64<br>9<br>32<br>230<br>18<br>12 | 502        | 28          | 19         | SiPM / HG2CROC<br>SiPM / HG2CROC<br>SiPM / Discrete<br>SiPM / HG2CROC<br>SiPM / HG2CROC<br>Astropix<br>SiPM / HG2CROC<br>SiPM / Discrete | Assume HGCROC 56 ch * 16 ASIC/RDO = 896 ch/RDO<br>32 ch/FEB, 16 FEB/RDO estimate, 8 FEB/RDO conserve.<br>HCAL 1536x5<br>*HCAL insert not in baseline<br>Assume similar structure to its-2 but with sensors with<br>250k pixels for RDO calculation.<br>24 ch/feb, 8 RDO estimate, 23 RDO conservative |

| Far Forward: B0: 3 MAPS layers<br>1 or 2 AC-LGAD layer<br>2 Roman Pots<br>2 Off Momentum<br>ZDC: Crystal Calorimeter<br>32 Silicon pad layer<br>4 silicon pixel layers<br>2 boxes scintillator | 300M pixel<br>1M<br>1M (4 x 135k layers x 2 dets)<br>640k (4 x 80k layers x 2 dets)<br>400<br>11,520<br>160k<br>72 | 10<br>30<br>64<br>42<br>10<br>10<br>10<br>2 | 15         | 8           | 8          | MAPS<br>AC-LGAG / EICROC<br>AC-LGAD / EICROC<br>AC-LGAD / EICROC<br>APD<br>HGCROC as per ALICE FoCal-E                                   | 3x20cmx20cm<br>600^cm layers (1 or 2 layers)<br>13 x 26cm layers<br>9.6 x 22.4cm layers<br>There are alternatives for AC-LGAD using MAPS and low<br>channel count DC-LGAD timing layers                                                                                                               |

| Far Backward: Low Q Tagger 1<br>Low Q Tagger 2<br>Low Q Tagger 1+2 Cal<br>2 x Lumi PS Calorimeter<br>Lumi PS tracker                                                                           | 1.3M pixels<br>480k pixels<br>700<br>1425/75<br>80M pixels                                                         | 12<br>12<br>1<br>1<br>24                    | 150        | 1           | 4          | Timepix4<br>(SiPM/HG2CROC) / (PMT/FLASH)<br>Timepix4                                                                                     |                                                                                                                                                                                                                                                                                                       |

| PID-TOF: Barrel<br>Endcap                                                                                                                                                                      | 2.2M<br>5.6 M                                                                                                      | 288<br>212                                  | 31         | 1           | 17         | AC-LGAD / EICROC (strip)<br>AC-LGAD / EICROC (pixel)                                                                                     | bTOF 128 ch/ASIC, 64 ASIC/RDO<br>eTOF 1024 pixel/ASIC, 24-48 ASIC/RDO (41 ave)                                                                                                                                                                                                                        |

| PID-Cherenkov: dRICH                                                                                                                                                                           | 317,952                                                                                                            | 1242                                        | 1240       | 13.5        | 28         | SiPM / ALCOR                                                                                                                             | Worse case after radiation. Includes 30% timing<br>window. Requires further data volume reduction                                                                                                                                                                                                     |

| pfRICH<br>DIRC                                                                                                                                                                                 | 69,632<br>69,632                                                                                                   | 17<br>24                                    | 24<br>11   | 12.5<br>6   | 1<br>1     | HRPPD / EICROC (strip or pixel)<br>HRPPD / EICROC (strip or pixel)                                                                       | software trigger                                                                                                                                                                                                                                                                                      |

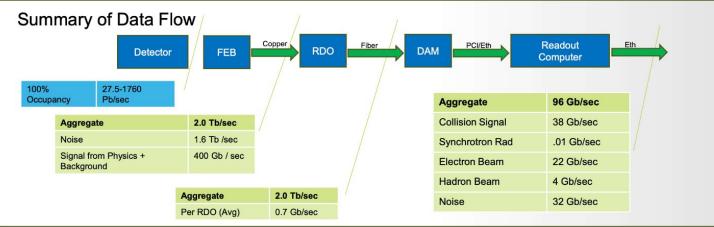

### **Summary of Channel Counts and Data Flow**

| Detector        | Channels |         |          |      |                   |      | Fiber    | DAM | Data                      | Data                          |

|-----------------|----------|---------|----------|------|-------------------|------|----------|-----|---------------------------|-------------------------------|

| Group           | MAPS     | AC-LGAD | SiPM/PMT | MPGD | HRPPD/<br>MCP-PMT |      | (single) |     | Volume<br>(RDO)<br>(Gb/s) | Volume<br>(To Tape)<br>(Gb/s) |

| Tracking (MAPS) | 16B      |         |          |      |                   | n/a  | 3158     | 35  | 26                        | 26                            |

| Tracking (MPGD) |          |         |          | 202k |                   | 118  | 236      | 5   | 1                         | 1                             |

| Calorimeters    | 500M     |         | 104k     |      |                   | 451  | 902      | 14  | 502 —                     | > 28                          |

| Far Forward     |          | 1.4M    | 253k     |      |                   | 247  | 624      | 10  | 15                        | 8                             |

| Far Backward    | 66M      | 60k     | 2k       |      |                   | 38   | 518      | 14  | 150 -                     | $\rightarrow 1$               |

| PID (TOF)       |          | 7.8M    |          |      |                   | 500  | 1500     | 14  | 31 —                      | <b>→</b> 1                    |

| PID Cherenkov   |          |         | 320k     |      | 140k              | 1283 | 2583     | 32  | 1275 —                    | → 32                          |

| TOTAL           | 16.9B    | 10.4M   | 679k     | 202k | 140k              | 2637 | 9521     | 124 | 2,000                     | 96                            |

New numbers coming out with improvements:

- Correct Thresholds

- Simulation Properties

- Updated Collider Lattice

- Distributions of hits

within detectors

- More realistic ASIC behavior

- Better understanding of software triggering scheme

See Elke's talk and ePIC background group wiki

For now, these are last summer's numbers

# Data throughput modeling (update)

| dRICH DAQ parameters                             |              |         |                   | ALCOR parameters                           |        |                      | Notes                                                    |              |  |

|--------------------------------------------------|--------------|---------|-------------------|--------------------------------------------|--------|----------------------|----------------------------------------------------------|--------------|--|

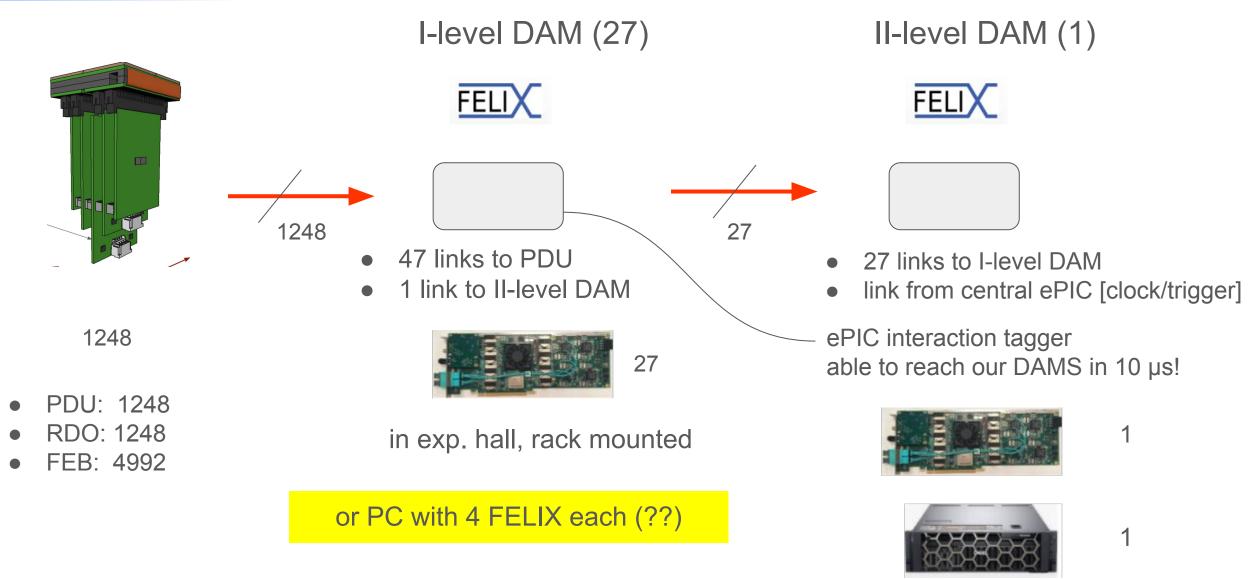

| RDO boards                                       | 1248         |         |                   | Front end limit [kHz]                      |        | 4000                 |                                                          |              |  |

| ALCOR64 x RDO                                    | 4            |         |                   | ALCOR Clock [ MHz]                         |        | 394,08 🔻             | It will be 394.08 MHz or 295.55 MHz                      |              |  |

| dRICH channels (total)                           | 319488       |         |                   | Channels/serializer                        |        | 8                    |                                                          |              |  |

| Number of DAM L1                                 | 27           |         |                   | Bits per hit                               |        | 64                   | 64 2 32-bit words per hit (also TOT)                     |              |  |

| Input link in DAM L1                             | 47           |         |                   | Bits per hit encoding 8/10                 |        | 80                   |                                                          |              |  |

| Output links in DAM L1                           | 1            |         |                   | Serializer band limit [Mb/s]               |        | 788,16               |                                                          |              |  |

| Number of DAM L2                                 | 1            |         |                   | Theoretical Serializer limit/ channel [kHz |        |                      | this would be with 0 control words                       |              |  |

| Input link to DAM L2                             | 27           |         |                   | Serializer limit single ch [kHz]           | -      |                      | this is expected to improve with ALCOR                   | ₹ v3         |  |

| Link bandwidth [ Gb/s] (assumes VTRX+)           | 10           |         |                   | Number of serializer per chip              |        | 8                    |                                                          |              |  |

| Interaction tagger reduction factor              | 200          |         |                   | Channel/chip                               |        | 64                   |                                                          |              |  |

| interaction tagger latency [s]                   | 2,00E-06     |         |                   | Shutter width (ns)                         |        | 2                    |                                                          |              |  |

| EIC parameters                                   | 2,002-00     |         |                   |                                            |        | 2                    |                                                          |              |  |

| EIC Clock [MHz]                                  | 98,522       |         |                   |                                            |        |                      |                                                          |              |  |

|                                                  |              |         |                   | Bandwidth analysis                         |        | Limit                | Comments                                                 |              |  |

| Orbit efficiency (takes into account gap)        | 0,92         |         | INPU <sup>-</sup> |                                            | 300,00 |                      |                                                          |              |  |

|                                                  |              | _       |                   | Rate post-shutter [kHz]                    | 55     |                      |                                                          |              |  |

| <ul> <li>numbers passed to ePIC</li> </ul>       |              |         |                   | Throughput to serializer [ Mb/s]           | 34     | ,                    |                                                          |              |  |

| •                                                | woral diag   | uccion  | <b>a</b> t        | Throughput from ALCOR64 [Mb/s]             | 276    |                      | limit FPGA dependent: with RDO prototype we will ha      | ave somethin |  |

| • interaction tagger critical (se                | everal disc  | u551011 | αι                | Throughput from RDO [ Gb/s]                |        |                      | based on VTRX+                                           |              |  |

| ANL)                                             |              |         |                   | Input at each DAM I [Gbps]                 | 50     |                      |                                                          |              |  |

| 7                                                | formed to by | Ideat   |                   | Buffering capacity at DAM I [MB]           | 0      |                      | to be checked but seems manageable                       |              |  |

| <ul> <li>some of the "pressure" trans</li> </ul> | siened to bu | Jagel   |                   | Throughput from DAM I to DAM II [Gbps]     | 0      |                      | this might be higher (from FELIX to FELIX)               |              |  |

|                                                  |              |         |                   | Output to each DAM II [Gbps]               | 0      | 84 270,00            | J                                                        |              |  |

| Note this is with 200                            |              | _       |                   |                                            |        |                      |                                                          |              |  |

|                                                  | 5            |         |                   |                                            |        |                      |                                                          |              |  |

| interaction toggar                               |              |         |                   |                                            |        |                      |                                                          |              |  |

| interaction tagger                               |              |         |                   | Aggregated dRICH data                      |        | Comments             |                                                          |              |  |

|                                                  |              |         |                   | Total input at DAM I [ Gb/s ]              | 1.368  | 14 This is only "ins | his is only "inside" DAM, not to be transferred on PCI   |              |  |

| reduction factor                                 |              |         |                   | Total input at DAM III Ch/a 1              | 6      | A This is based of   | a conversion above I reduction factor of the interaction | n toggor     |  |

|                                                  |              |         |                   | Total input at DAM II [ Gb/s ]             | - 0    | 64 THIS IS DASEU OF  | aggregation above + reduction factor of the interaction  | in tayyer    |  |

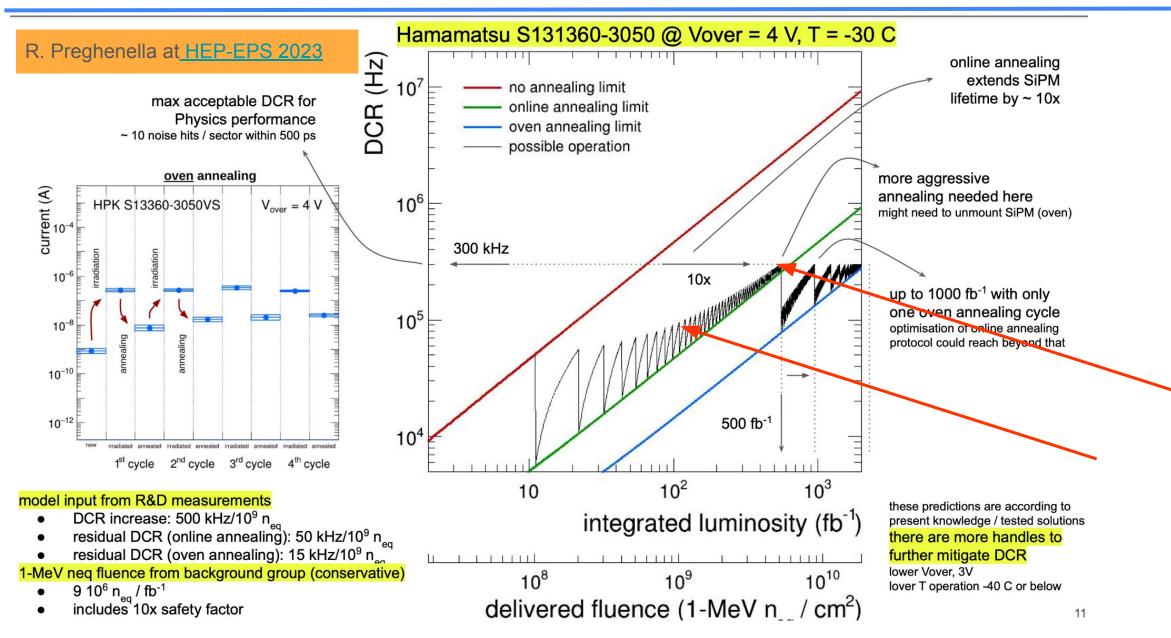

### Ageing model and some DAQ consequences...

# dRICH throughput during EIC life...

| When                                                      | DCR | Total throughput at DAM-I | Total throughput at DAM-II |

|-----------------------------------------------------------|-----|---------------------------|----------------------------|

| starting                                                  | 2   | 9.2 Gbps                  | < 1 Gbps                   |

| after 100 fb <sup>-1 (and several annealing cycles)</sup> | 100 | 456 Gbps                  | 2.28 Gbps                  |

| "at limit"                                                | 300 | 1.3 Tbps                  | 6.84 Gbps                  |

this is with factor 200 but...

https://docs.google.com/spreadsheets/d/1P3qoogFWuicXDgojwvhaFL2EnwQ7BEmGIITg1fwDUkE/edit#gid=0

Questions:

- a) when the ePIC DAQ really starts having a problem? (max. throughput FELIX2-PCIe?) [ it is also useful info for data reduction target inside DAM-II at FPGA ]

- b) any scenario about machine luminosity (and radiation) in 2031-2034?

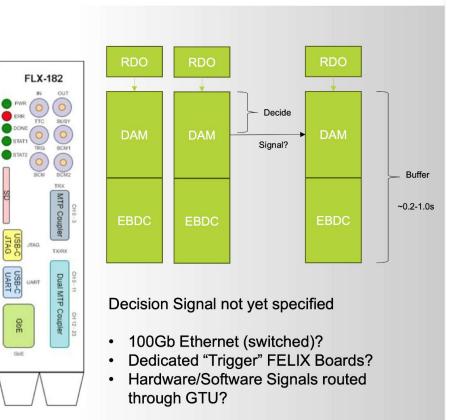

# Note on latency of interaction tagger

#### **Triggering To Do**

- Technical Issues

- How is the communication handled?

- Trigger Issues

- What are the algorithms, and what detectors go into the algorithms?

- dRICH

- Does not need to be collision trigger. Trigger only needs to ensure that there is a real hit in the detector

- Low Q Tracker

Collision Trigger expected

Could use prescale instead

- Collision detector detector?

- Do we need one?

- Can we construct one?

- What would it look like?

the model so far uses 2 µsec latency

Eth implementation on FLX-192 to distribute "interaction tagger"?

<u>Note</u>: 2 ms latency instead would require 12.8 MB buffering capacity (with 300 KHz DCR rate) in FLX-182

| 2024                                                                                                                                                                                                                       | 2025                                                                                                                                                                                                                                          | 2026                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>hardware effort</li> <li>RDO prototype as close as possible to final</li> <li>RDO readout of old FEB32</li> <li>initial ePIC link test with RDO (clock)</li> <li>input to TDR</li> <li>radiation tests</li> </ul> | <ul> <li>integration with ALCOR64 in the PDU</li> <li>readout with VC709 &amp; ePIC link<br/>(including clock)</li> <li>RDO rev. 2 final components</li> <li>possibly test in detector box</li> <li>(likely radiation tests again)</li> </ul> | <ul> <li>FELIX available in ePIC to groups</li> <li>use of DAM (FELIX2)</li> <li>crucial firmware development L1-DAM<br/>/ L2-DAM</li> </ul> |

| 2027       | 2028     | 2029                                               |

|------------|----------|----------------------------------------------------|

| production | assembly | assembly in-situ<br>DAM deployment + commissioning |

in parallel:

- someone has to think/build ePIC interaction tagger

- further data reduction/calibration through L2-DAM FPGA or SRO to be integrated

### Conclusions

- ongoing effort toward specifications/requirements for RDO (at 60/70%)

- secured VTRx+ and almost defined FPGA baseline

- need of highly integrated development of RDO with other dRICH electronic components

- ePIC link protocol still not defined, we need to remain close to central ePIC DAQ

- at the forefront  $\rightarrow$  designing first ePIC RDO (risk of later specs/surprises)

- ePIC interaction tagger is crucial to dRICH architecture  $\rightarrow$  need to work with ePIC/EIC project