### **EICROC Progress Report**

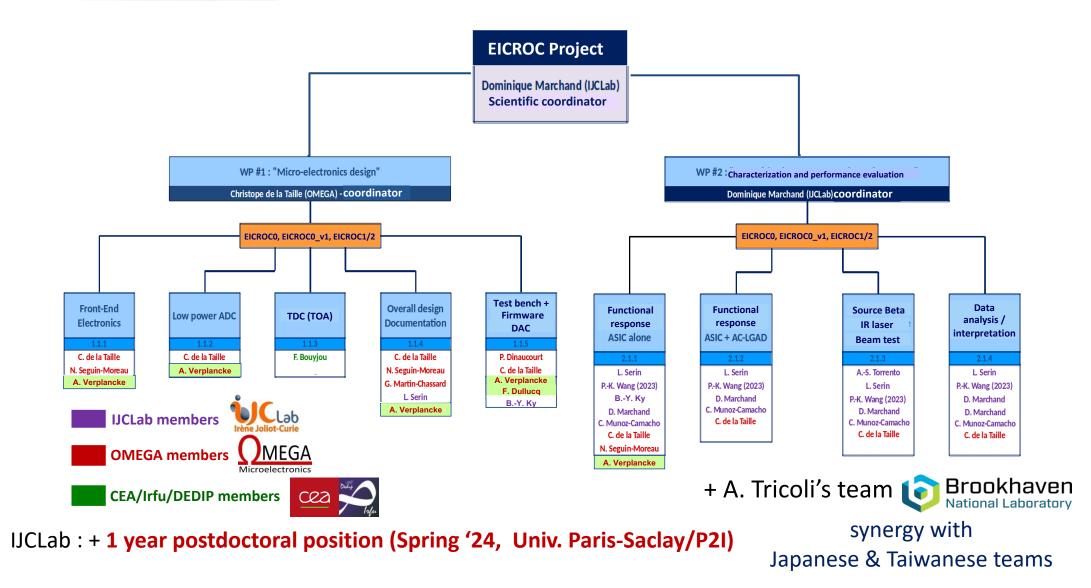

D.Marchand, C. Munoz, L. Serin, B.-Y. Ky, A.-S. Torrento (IJCLab) P. Dinaucourt, F. Dulucq, C. de La Taille, N. Seguin,-Moreau, A. Verplancke (OMEGA) F. Bouyjou (CEA/Irfu/DEDIP)

Objective: Development and characterization of an ASIC EICROC (32 x 32)

able to read-out the new generation of pixelated (500 x 500 μm²) silicon sensors: AC-LGAD

(Low-Gain Avalanche Diode) coupled AC

for the Electron Ion Collider (EIC)

1<sup>st</sup> intention: optimized for Far Forward detectors: the Roman Pots

Method: stepping up through succesive ASIC iterations to control performances fulfilling ePIC detector requirements

EICROCO prototype (16 channels; 4 x 4): under test since March '23

eRD109 - Progress Reports - Electronics & DAQ WG meeting - Feb. 1st, 2024

# The EICROC project team

#### **Requirements:**

- pixel size 0.5 x 0.5 mm<sup>2</sup> (HGTD 1.3x1.3 mm<sup>2</sup>)

- low power consumption < 2 mW/channel</li>

- low jitter ~ 20 ps

- low noise ~ 1 mV/channel

- sensitivity to low charge (2 fC)

- time resolution: 30 ps

- spatial resolution: 50 microns

#### **Charge sharing studies**

(simulation +  $\beta$  source w/ **ALTIROC1**\_v2)

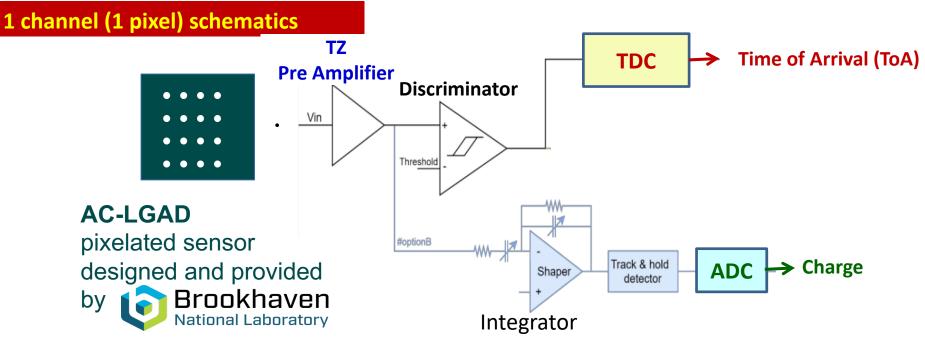

### EICROC0 design:

- **TZ Pre Amplifiers** from ALTIROC (ATLAS/HGTD)

- 10 bit **TDC** from HGCROC (CMS, CEA/Irfu)

- 8 bit ADC for time-walk correction (AGH Krakow, adapted from HGCROC)

Compared to ALTIROC (ATLAS/HGTD), ToT TDC (non-linear behavior versus the deposited charge) replaced by an ADC

# **EICROC project: status**

- **EICROCO characterization** (OMEGA, CEA/Irfu, IJCLab):

- > Individually each component shows performance in agreement with design

- Evaluation of cross-talk between channels underway, results to be released shortly

- Further investigation of noise/clock couplings mandatory to drive next ASIC iteration (EICROCOA)

- Support to BNL team to set up an EICROC0 test bench

- Periodic working meetings with BNL

- Periodic progress reports in ePIC eRD112/AC-LGAD meetings

## **Outreach**

P.-K. Wang PhD defense: 12/09/2023, partly on EICROC project

# **Strong support from DOE/eRD109 Consortium**

# **EICROC Project: recent/on-going work**

- Still investigationg couplings

- Focusing on data (rather than analogiocal probe PA signal)

Efficiency curves scripts (discriminator threshold, TDC hits vs inj. Charge)

- Exploiting External Trigger

- ➢ Board with AC-LGAD sensor (IJCLab & BNL) → oscillations > 2 PA channels observed

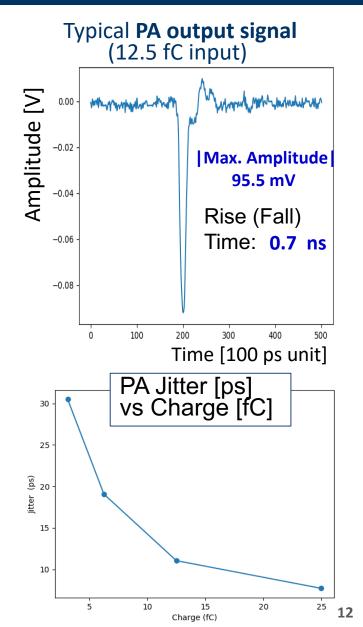

# ElCROCO: Probe PA Jitter vs Injected Charge

Probe PA Jitter [RMS] versus Injected charge (Board\_no\_sensor)

# **EICROC Project: update & perspectives**

#### 01/09 - 01/13, 2024

#### A very fruitful working winter meeting!

- > « AC-LGAD and associated electronics & DAQ » dedicated sessions: workfest:

- Feedbacks from CMS/HGCROC testing (wire/bimp-bonding),

- Feedbacks from FermiLab/FCFD testing

- EICROC0 hands-on sessions organized by the BNL team (about 70 pers.)

- EICROC0 « expert » working sessions on the test bench (thanks to Argonne colleagues for providing scope, LV, place, help):

- scripts (discri, Ext. Trigger) / method sharing, bootfiles updates,

- In person very constructive meetings/chats with people involved in FW & Far FW detectors (BNL team, Alex J., Yulia F., Zhenyu Y., Satoshi Y., Mathieu B., ...) to draw perspectives for ramping up on EICROC0 testing

- Exploiting EICROC0 analogical Probe PA output signals & digital outputs:

- \* Laser test bench (at BNL) requires synchronisation capabilities,

- \* Beta source (IJCLab & BNL) requires triggerless acquisition

- \* Will to take part to the DESY testbeam next June at DESY (wire- & bump- bonded AC-LGAD & EICROC0)

# **EICROC Project: update & perspectives**

### EICROC0 chips

• 15 will be sent to BNL mid-February in view of hybridation (EICROC0+AC-LGAD)

### Updated EICROC0 PCBs (test boards): 20 pieces

- Submitted for fabrication before Christmas should be received by mid- January Unfortunate misunderstanding between Company & OMEGA

delivery expected 2<sup>nd</sup> week of February

- Components for cabling: ordered ; delivery expected next week

- Cabling will be performed at IJCLab by the end of February

- 5 PCBs will be sent to IPHC (Strasbourg, France) to wire-bond an EICROC0 (March)

- 4 PCBs will be sent to IPHC (Strasbourg, France) to wire-bond an EICROC0 + AC-LGAD [AC-LGAD sensors provided by BNL]

- 6 PCBs will be sent to BNL (March)

- 5 PCBs will be sent to IPHC (Strasbourg, France) to wire-bond an hybrid [when hybrids ready; Hybrids provided by BNL]

Should we consider to also test HPK AC-LGADs?

# **EICROC Project: update & perspectives** Next iterations: **EICROCOA & EICROC1**

**EICROC0A:** including a low power ADC + improved testing capabilities

- > EICROC1:

- 4 (or 8) x 16 to investigate floor planning

- improved/additional testing capabilities

EICROC (0A & 1) and H2GCROC ASICs will be submitted together for fabrication (summer/fall 2024)

# BACKUP

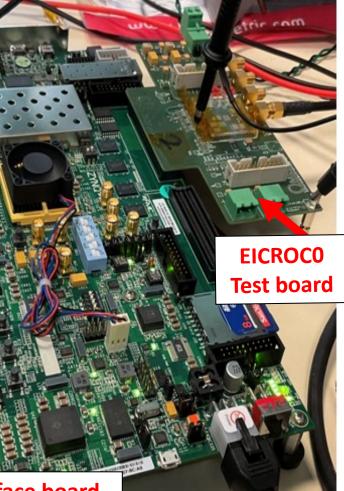

### Status of EICROC0 Test Bench at UCLab

EICROC0 Test board

#### **EICROC0 test bench operational at IJCLab since March '23**

I<sup>2</sup>C communication (firmware + software developments)

Data stream written/read

EICROC0 DC levels

Discri. threshold exploration

EICROC0 charge injection system (0 to 25 fC)

EICROC0 decoding (TDC, ADC) Firmware + software

External trigger: signal directly injected into TDC

Additional EICROC0 test benches operational at: OMEGA (May '23), BNL (July. '23), CEA/Irfu (Sept. '23)

Interface board (Xilinx ZC 706)

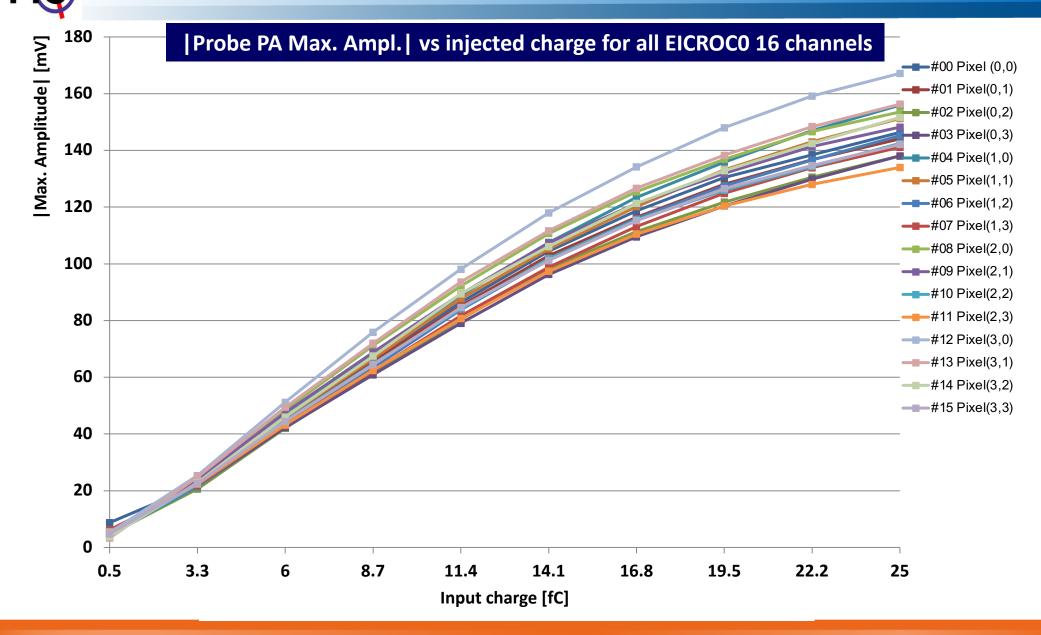

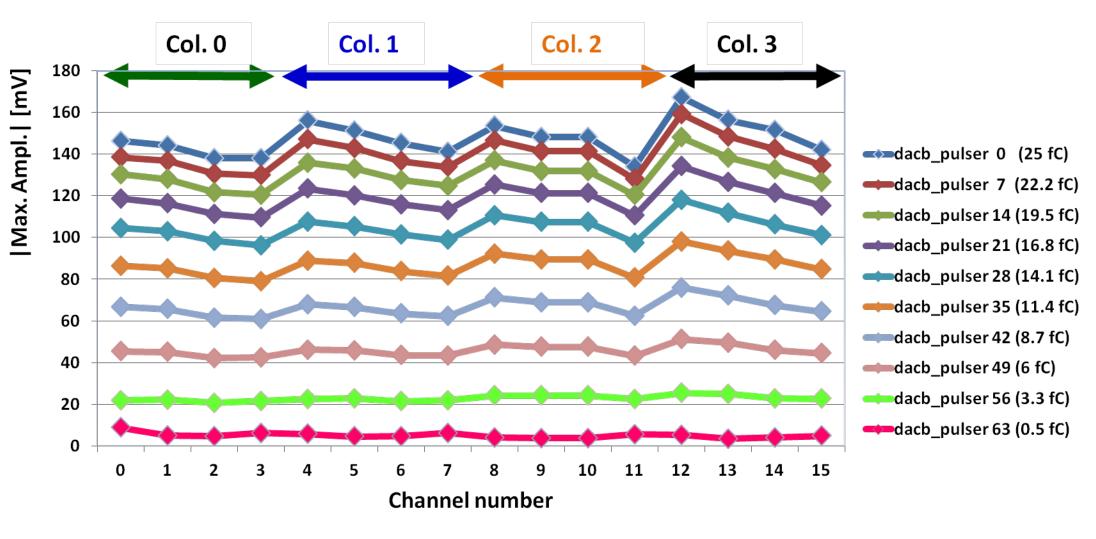

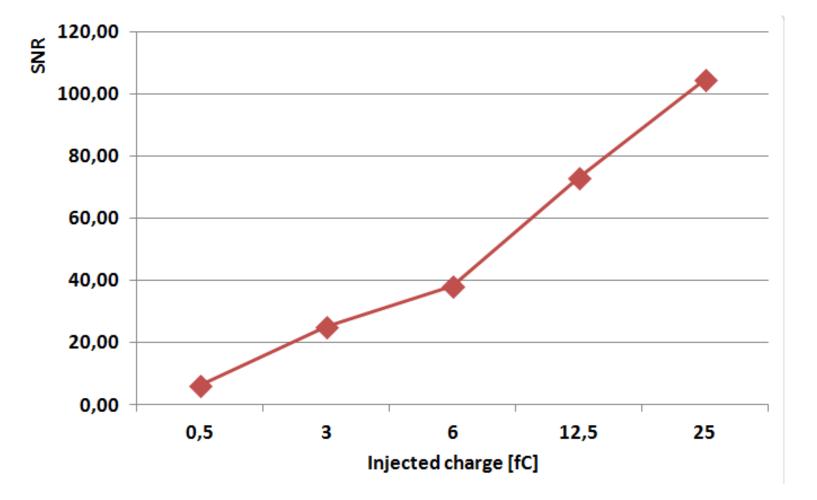

### **EICROC0 TZ Pre Amplifier Probe output signal amplitudes**

#### Current studies [board w/ EICROC0, no AC-LGAD sensor]

- > **TZ Pre Amplifier** output signals

- SNR > 70 for 12.5 fC input ; SNR > 6 for 1 fC input)

- Jitter evaluation: < 20 ps (  $\geq$  6 fC) ; 8 ps (25 fC)

- > **TDC** performance (**alone**): functional

- quantification step (~25 ps) in good agreement with design

- observation of a large noise coupled to 160 MHz clock

- Time of Arrival resolution estimated to 14 ps (25 fC)

- > ADC performance (alone) functional

- Evaluation of cross-talk between channels underway

- Further nvestigation of noise / clock (160 MHz) coupling issues (TDC and ADC)

**Short term plan:** to evaluate performances of the existing board w/ EICROC0 + AC-LGAD (4 x 4)

### EICROC0 TZ Pre Amplifier Probe output signal amplitudes

### **EICROC0** Probe PA output Signal to Noise Ratio (SNR)

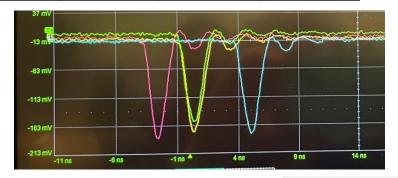

### EICROC0 TZ Pre Amplifier Probe output signals

| Pixel /<br>Channel<br>Mapping | Column 0             | Column 1    | Column 2             | Column 3             |

|-------------------------------|----------------------|-------------|----------------------|----------------------|

| Line 0                        | Pixel ( <b>0</b> ,0) | Pixel (1,0) | Pixel ( <b>2</b> ,0) | Pixel ( <b>3</b> ,0) |

|                               | <b>#00</b>           | <b>#04</b>  | <b>#08</b>           | <b>#12</b>           |

| Line 1                        | Pixel ( <b>0</b> ,1) | Pixel (1,1) | Pixel ( <b>2</b> ,1) | Pixel ( <b>3</b> ,1) |

|                               | <b>#01</b>           | <b>#05</b>  | <b>#09</b>           | <b>#13</b>           |

| Line 2                        | Pixel ( <b>0</b> ,2) | Pixel (1,2) | Pixel (2,2)          | Pixel ( <b>3</b> ,2) |

|                               | <b>#02</b>           | <b>#06</b>  | <b>#10</b>           | <b>#14</b>           |

| Line 3                        | Pixel ( <b>0</b> ,3) | Pixel (1,3) | Pixel (2,3)          | Pixel ( <b>3</b> ,3) |

|                               | <b>#03</b>           | <b>#07</b>  | <b>#11</b>           | <b>#15</b>           |

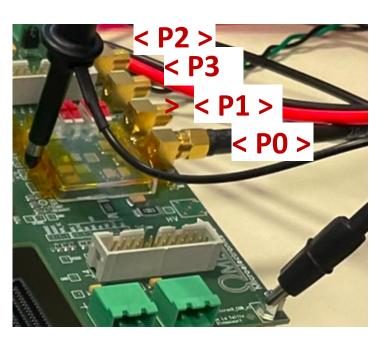

PA output signals through SMA connector s (PCB back plane)

Feature of EICROC0 test board: Observation of 4 Probe PA channels simultaneously

> **1 Probe PA per column** *Ex.: #00, #04, #08, #12*