## Note before ROC reinstallation

Jaein Hwang Byungsik Hong

## List of half entry chips(updated)

Based on latest beam data during Run 2023 (run number 24767)

- Felix 0 (pid 3001) (total 1) module 7 chip 15

- Felix 2 (pid 3003) (total 1) Module 9 chip 16

- Felix 3 (pid 3004) (total 3) Module 13 chip 21,23,25 (total 3)

- Felix 7 (pid 3008) (total 20)

Module 0 chip 1,2,3,4,5,14,15,16,17,18, 7,9,11,13,20,22,24,26 (total 18 chips)

Module 1 chip 1,2

In total, 25 chips; 25/26x112 ~ 0.86% of total chips

Let's update after calibration test! (Since calibration test would be good way to confirm the half entry chips.)

### Weird behavior at channel 0

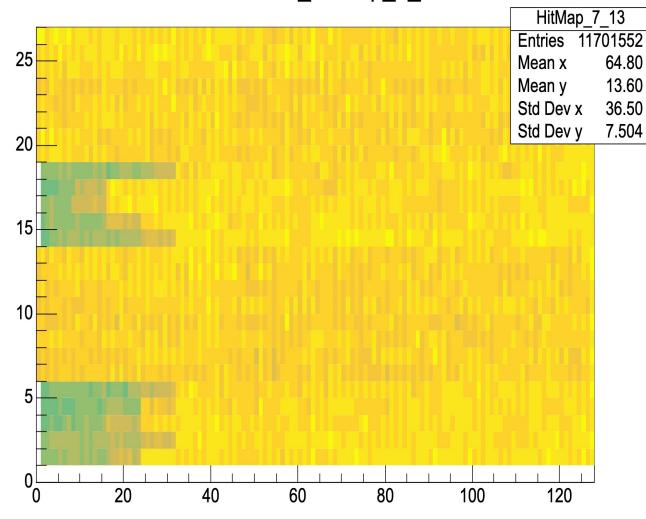

Normalized\_HitMap\_7\_13

It's already reported in Jan 11 2024 INTT meeting.

I thought that if we mask the channel 0, Some adjacent channels(from 1 to 32) will drop some hits and will be classified as cold channel. Fraction of cold channel due to that ~ 4%

#### I checked masking lists

/home/phnxrc/INTT/sphenix\_inttpy/run\_scripts/bkp/mask\_ch\_north(south)\_v1.txt.230720 and confirmed that we did not problematic mask channel 0 during run2023.

#### One idea we can try is:

Try to really mask the weird channel 0 and see whether if this issue would disappear.

#### Of course, let see the calibration plot first!

#### See also:

https://wiki.sphenix.bnl.gov/index.php/To\_do\_list\_of\_run\_24\_commissioning

# Comment on ROC-18 (will be install at IR soon at ROC-0S)

#### jaeinhwang213@gmail.com

Re: [Sphenix-intt-I] ROC-18 test at silicon lab

받는 사람: nouicer

Sorry for the late response.

As you know, ROC-18 got damaged at the regulator for column B. And we can take the good data from column B after the replacement of the regulator. D1 and D2 ports have some missing channel chips(one or two chips).

But, columns A, B, and C are good.

■ 받은 편지함 - Google 메일상자에서 찾음

Thank you, Best Regards,

Jaein

4/28/23 오전 9:15, nouicer < rachid.nouicer@bnl.gov > 작성:

2023년 5월 1일 오전 9:49

2023 May 1

Just mention it again before the ROC-reinstallation to ensure that we may need to avoid to use port D. Of course, let see the calibration plot first!

| INTT - DAQ[0-7] | 000.000.000.000 | [3001 - 3999] |           | [0-1]      | [0-13]        | [A-D][0-3]    | B[0-1]L[0-1] [00-15] | [1-16]             | RC[0-7][N/S] |

|-----------------|-----------------|---------------|-----------|------------|---------------|---------------|----------------------|--------------------|--------------|

| Server Label    | Server IP Addr  | Packet ID     | MPT48-58m | Felix Port | Felix Channel | ROC Port Name | Ladder Name          | Breakout Cable 15m | ROC Name     |

| INTT - DAQ0     |                 | 3001          | 99        | 0          | 0             | D2            | B1L1 01S             | 1                  | RC-0S        |

| INTT - DAQ0     |                 | 3001          | 99        | 0          | 1             | C1            | B0L1 01S             | 1                  | RC-0S        |

| INTT - DAQ0     |                 | 3001          | 99        | 0          | 2             | C2            | B1L0 01S             | 1                  | RC-0S        |

| INTT - DAQ0     |                 | 3001          | 99        | 0          | 3             | В3            | B1L0 00S             | 1                  | RC-0S        |

| INTT - DAQ0     |                 | 3001          | 99        | 0          | 4             | A2            | B1L1 00S             | 1                  | RC-0S        |

| INTT - DAQ0     |                 | 3001          | 99        | 0          | 5             | B1            | B0L0 00S             | 1                  | RC-0S        |

| INTT - DAQ0     |                 | 3001          | 99        | 0          | 6             | A1            | B0L1 00S             | 1                  | RC-0S        |

N

#### nouicer

[Sphenix-intt-I] Fwd: Re: ROC-18 test at silicon lab

받는 사람: sphenix-intt-l@lists.bnl.gov

2024년 1월 31일 오전 10:26

2024 Jan 1

Reminder from Rachid

Dear Jaein,

See below the e-mail that you sent me about ROC-18 status. I hope you agree that we can put ROC-18 in position RC-0S for Run-24?

Sincerely, Rachid

See also INTT e-log https://sphenix-intra.sdcc.bnl.gov/WWW/elog/INTT/98

We used Port D2 on ROC-0S.

Based on the test I did at silicon lab.

There would be one or two empty chips.

We may need to switch it to other port.

(B2 can be good candidate)

See also INTT Full Mapping document

https://docs.google.com/spreadsheets/d/1 9PSvkhAQA8rnkP0z\_wpN87CWQ6O-

f3bT/edit#gid=1658598300

## DAQ operation guide (need to be update)

Unfortunately, we could not get reasonable data through the test bench system at rack room. We have more information we may need in future.

For example, one more thing I've added: How to switch to spare GTM.

How to change setup for different GTM configuration [edit | edit source]

For different GTM, most likely spare GTM (GTM1) [edit | edit source]

Since we have two GTM, the one is main GTM, another is the spare GTM(GTM1) normally for test purpose.

The below procedure is how to setup for spare GTM in LOCAL mode

Note: In global mode, DO NOTHING without permission from DAQ operator.

- 0. Contact to DAQ operator whether if we are ready to use the spare GTM or not.

- 1. ssh inttX (connect to intt servers you want to use.)

- 2. export GTMHOST=gtm1.sphenix.bnl.gov (note : gtm.sphenix.bnl.gov = main GTM,gtm1.sphenix.bnl.gov = spare GTM)

- 3. Open operation/INTT/rc\_setup\_local.sh and changeGTMHOST=gtm.sphenix.bnl.gov toGTMHOST=gtm1.sphenix.bnl.gov

https://wiki.sphenix.bnl.gov/index.php/INT T\_Felix\_DAQ

## backup