## **AstroPix Module Interfaces Documentation**

ePIC Barrel ECAL Project

| Project Document No.: | Institute Document No.: | Created:  | 11 April 2024   | Page: I of 12 |

|-----------------------|-------------------------|-----------|-----------------|---------------|

| epic-bic-im-XXXX      | xxx                     | Modified: | 12th April 2024 | Rev. No.: 0.1 |

# **AstroPix Module Interfaces Documentation**

ePIC Barrel ECAL Project Abstract

This document provides a technical description of the interfaces between AstroPix Module, Stave, and End-of-Stave FPGA board.

| Prepared by  | Checked by | Approved by |

|--------------|------------|-------------|

| Manoj Jadhav |            |             |

|              |            |             |

|              |            |             |

$Distribution\ List$

# History of Changes

| Rev. No. | Date          | Pages | Description of changes |

|----------|---------------|-------|------------------------|

| Draft    | 11 April 2024 | All   | Draft                  |

| v0.1     | 11 April 2024 | All   | created the draft      |

# Contents

| 2 | Ast | roPix Chip Specification |

|---|-----|--------------------------|

|   | 2.1 | AstroPix Version 5       |

|   | 2.2 | Digital Interface        |

|   | 2.3 | Digitization Data Rate   |

## 1 Introduction

The Barrel Electromagnetic Calorimeter comprises two detector technologies: AstroPix, an HV-CMOS MAPS sensor, and Pb/SciFi. The AstroPix sensors are integrated into 4 barrel layers, sandwich between Pb/SciFi layers to construct an imaging part of the barrel ECAL.

1

7

The document will provide details on the AstroPix chip, Module design, Module electric schematic, Stave assembly, and interfacing with the end-of-stave FPGA card.

### 2 AstroPix Chip Specification

- AstroPix is a low-power HV-CMOS monolithic active pixel sensor designed with 180 nm

- 10 CMOS process technology. The AstroPix baseline performance requirements are listed in

- table 1, comprising effective area, angular resolution, and energy resolution.

$500 \times 500 \ \mu \text{m}^2$ Pixel size  $2 \times 2 \text{ cm}^2$ Chip size  $1.5 \text{ mW/cm}^2$ Power usage 20 keV -700 keV Dynamic range 5 keV  $\sigma$  @ 122 keV Energy resolution Time resolution 25 nsNoise Floor 5 keV Signal threshold 20 keV

Table 1: The expected specifications of AstroPix readouts.

#### 2.1 AstroPix Version 5

- <sup>13</sup> Currently testing AstroPix versions 3 and 4. The specifications of versions 3 and 4 will

- be added later. Version 5 is under design process and will be available at the beginning

- of FY2025. The specifications of AstroPix version 5 are listed in table 2.

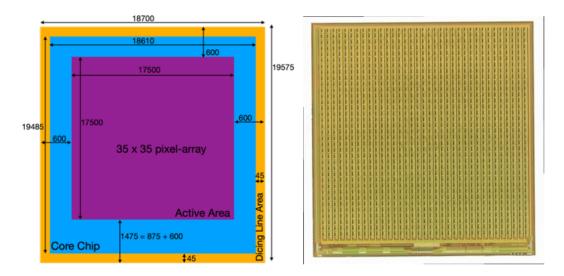

Figure 1: The AstroPix version 3 dimensions (left) and chip image (right). Version 5 dimensions match to the dimensions of version 3.

| Pixel Pitch                        | $500 \ \mu \text{m} \ (\text{pixel size } 300 \ \mu \text{m})$ |

|------------------------------------|----------------------------------------------------------------|

| Chip size                          | $1.87 \times 1.96 \text{ cm}^2$                                |

| Pixel matrix                       | $35 \times 33$                                                 |

| Sensor thickness                   | $525~\mu\mathrm{m}$                                            |

| Power usage                        | $1.63 \mathrm{\ mW/cm^2}$                                      |

| Dynamic range                      | $20 \mathrm{keV}$ - $700~\mathrm{keV}$                         |

| Energy resolution                  | $5~{\rm keV}~\sigma$ @ 122 keV                                 |

| Time resolution                    | 3.25 ns (25 ns without TDC)                                    |

| Noise Floor                        | 5  keV                                                         |

| Signal threshold                   | 20  keV                                                        |

| Operating temperature (not tested) | -40 °C/+150 °C                                                 |

Table 2: The specifications of AstroPix version 5.

| Analog VDDA                 | 1.8V      |

|-----------------------------|-----------|

| Analog VSSA                 | 1.2V      |

| Digital VDDD                | 1.8V      |

| Analog Ground               | GNDA      |

| Digital Ground              | GNDD      |

| Sensor Reverse Bias Voltage | 0 to 400V |

Table 3: External supply voltage required of AstroPix version 5.

### 2.2 Digital Interface

AstroPix version 5 has pixel-by-pixel readout with 1 Hitbuffer assigned per pixel. Each column has an end-of-column buffer. There are 3 timestamp clocks: 15-bit course TimeStamp<sub>18</sub> at 2.5 MHz, 3-bit fine TimeStamp at 20 MHz, and 16-bit flash TDC, which provides time response and Time-Over-Threshold resolution of 3.125 ns.

16

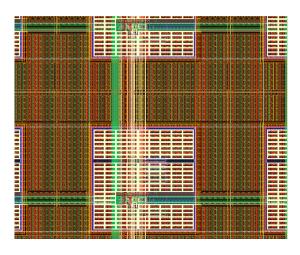

Figure 2: The pixel matrix structure for AstroPix with a pixel pitch of 500  $\mu$ m and pixel nwell/implant size of 300  $\mu$ m.

[git] •

The comparator output is connected to Hitbuffer in the periphery. At the signal's first (falling) edge, coarse and fine TS are saved, and the Flash TDC is started. The TDC measures the exact difference from the falling edge to the next rising edge of the FineTS clk.

#### 25 DaisyChain Protocol

31

32 33

The data streaming from EOSB to AstroPix and AstroPix to EOSB features a Header and Data format. The formats are different in two directions: EOSB to the chip (Module) configures AstroPix chips by writing data and AstroPix chip (Module) to EOSB only defines frames of data passing through the daisy chain with length. The command set is framed by the chip selection, some of the commands can be chained.

#### EOSB to Chip protocol:

| bits |         |   |   |              |   |   |   |

|------|---------|---|---|--------------|---|---|---|

| 7    | 6       | 5 | 4 | 3            | 2 | 1 | 0 |

|      | Command |   |   | Chip Address |   |   |   |

| BIT   | FIELD   | DESCRIPTION                                                                                                               |

|-------|---------|---------------------------------------------------------------------------------------------------------------------------|

| [4:0] | Address | Requires 20 single addresses  - 0x00 - 0x14 : Single addresses - 0x15 - 0x1F : Reserved - 0x1D: Invalid - 0x1E: Broadcast |

| [7:5] | Command | 8 Commands:  - 0x01 - NOCMD / IDLE - 0x02 - Routing: dispatch addresses - 0x03 - Shift Register Config                    |

IDLE Byte represents no specific command and an invalid address: 0x1D for address and 0x1 for IDLE -> 0x3D

Figure 3: Hyder Bytes.

| COMMAND | NAME                        | LENGTH  | DESCRIPTION                                                                                                                                                                                                                                                                                                    |

|---------|-----------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01    | NOCMD                       | 1 Byte  | Nothing to do                                                                                                                                                                                                                                                                                                  |

| 0x02    | Address<br>Config           | 1 Byte  | Header Address represents the new address of the Chip Chip forwards command to the next chip with Address = Address + 1  To configure Addresses with first Chip "00", send 0x40 to the first Chip, then send some IDLE bytes so that the Clock stays active and the addressing byte gets passed down the chain |

| 0x03    | Shift<br>Register<br>Config | N Bytes | Once this command is send, the whole SPI Frame is used - SPI Chip Select must be deasserted and reasserted to send a new command                                                                                                                                                                               |

Figure 4: Commands to AstroPix Chip.

#### Chip to EOSB protocol:

7

6

5

4

3

2

1

0

Chip Address

Payload Length

- Chip Address is the Configured Chip ID using the routing byte

- The PayloadLength is the number of bytes trailing the header

#### Hit Packet Type

At the moment we only need 1 Packet type:

| bytes  |                       |                                     |                     |                                                  |                          |                                                                |                             |

|--------|-----------------------|-------------------------------------|---------------------|--------------------------------------------------|--------------------------|----------------------------------------------------------------|-----------------------------|

| 0      | 1                     | 2                                   | 3                   | 4                                                | 5                        | 6                                                              | 7                           |

| Header | Row<0:5><br>,Col<0:1> | Col<2:5<br>>,TSFr<br>omDet<<br>0:3> | TSFromD<br>et<4:11> | TSFrom<br>Det<12:<br>14>,TS<br>FromDe<br>t2<0:4> | TSFrom<br>Det2<5:1<br>2> | TSFrom<br>Det2<13:<br>:14>,TSF<br>ine<0:2><br>,TSFine<<br>0:2> | TSTDC1<0:3>,<br>TSTDC2<0:3> |

Figure 5: Data Format from the Chip.

AstroPix version 5 will have 1x8 Bytes. Right now, they can be reduced by on-chip subtraction. As shown in figure 5 the data bytes can be decoded as,

38 8b Header,

39 6b Row,

35

40 6b Col,

41 15b TS,

$42 ext{ } 15b + 2x(4b + 3b) ext{ ToT.}$

### <sup>14</sup> 2.3 Digitization Data Rate

- The whole Chip triggers at 10Hz. Only one counter per row/column with 8 Bytes. With

- <sup>46</sup> Chip array of 36  $\times$  36 and 500  $\mu$ m Pixels there are around 1300 Pixels.

- 47 1300 \* 8 Bytes Data = 10400 Bytes

- Protocol including daisy chain etc.. = 50% overhead i.e. +5200 Bytes

- Total = 15600 Bytes /s / chip

- 50 Pixelator: 1 Chip, Full Module with 9 chips = 9 \* Pixelator = 9 Chips

- For one Module:  $9 \times 15600 = 140 \text{ kByte/s}$

The maximum expected rate for Barrel Ecal using the following table 4:

Avg hit rate/pixel [1/s] is 5.68E-02, so for a chip it is 70 hits and for a Module it is 840

Considering double the hits per module, it is 1680

The expected data rate for a Module is 1680\*8 bytes = 13.44 kBytes/s.

52

The expected data rate for a Module is 1680\*8 bytes = 13.44 kBytes/s.

56

58

60

61

#### Data rate for Barrel ECAL

| Integration time [s]                                  | 6.00E-06 |

|-------------------------------------------------------|----------|

| Nb of pixels                                          | 5.28E+08 |

| Total rate [1/s]                                      | 3.00E+07 |

| Avg hit rate/pixel [1/s]                              | 5.68E-02 |

| Propablility of getting hit twice                     | 1.94E-08 |

| Propablility of getting hit twice for entire detector | 1.02E+01 |

| Drop rate for the entire detector                     | 3.41E-07 |

| Nb of hits with one drop                              | 2.93E+06 |

Table 4: Data hit rate

The expected hit rate for all imaging layers together Low rates is well below ;  $30~\mathrm{MHz}$  This translates to a maximum hit rate per tracker stave (1 x 108) ;  $36~\mathrm{kHz}$

This draft will also add more information about module design, electrical interface and power numbers. This information can temporarily be accessed at link here

# 62 A Appendix