# Silicon: Readout

Joachim Schambach

SVT Readout and Powering Work Package Co-Coordinator

Oak Ridge National Laboratory

Incremental Design and Safety Review of the EIC Tracking Detectors

March 20-21, 2024

Electron-Ion Collider

### **Charge Questions Addressed**

- 1. Are the technical performance requirements appropriately defined and complete for this stage of the project?

- 2. Are the plans for achieving detector performance and construction sufficiently developed and documented for the present phase of the project?

- 3. Are the current designs and plans for detector, electronics readout, and services sufficiently developed to achieve the performance requirements?

- 4. Are plans in place to mitigate risk of cost increases, schedule delays, and technical problems?

- 5. Are the fabrication and assembly plans for the various tracking detector systems consistent with the overall project and detector schedule?

- 6. Are the plans for detector integration in the EIC detector appropriately developed for the present phase of the project?

- 7. Have ES&H and QA considerations been adequately incorporated into the designs at their present stage?

#### **Outline**

- Top Level Readout Design

- Inner Barrel Readout Design

- Outer Barrel and Disk Readout Design

- SVT Numbers

- Prototype Developments

- Summary

# Top Level Readout Design

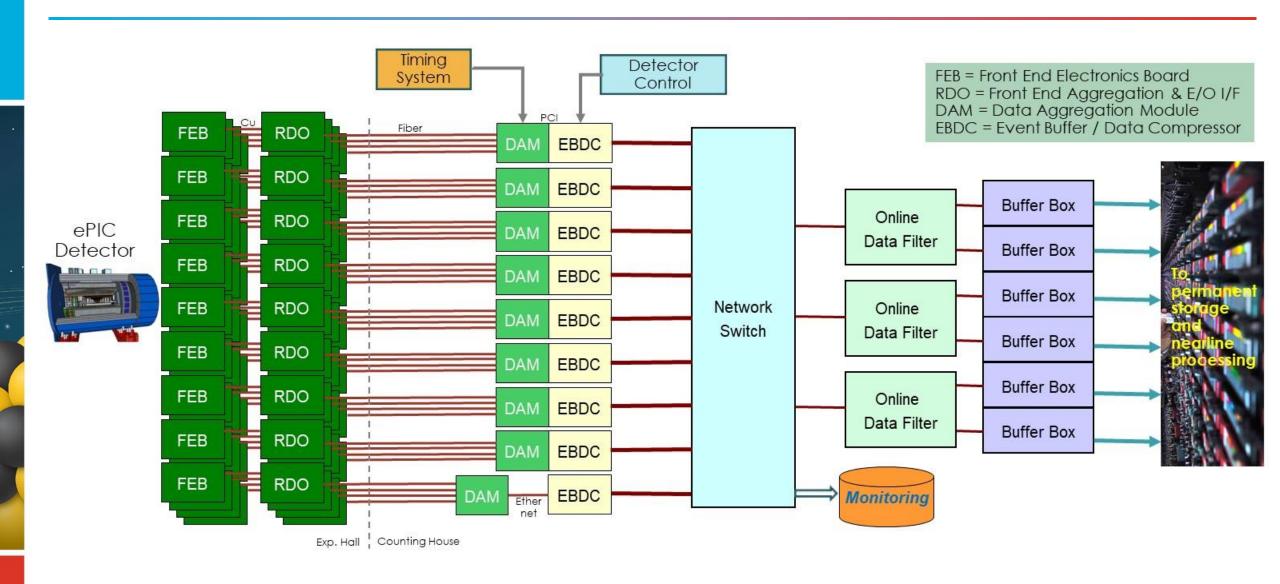

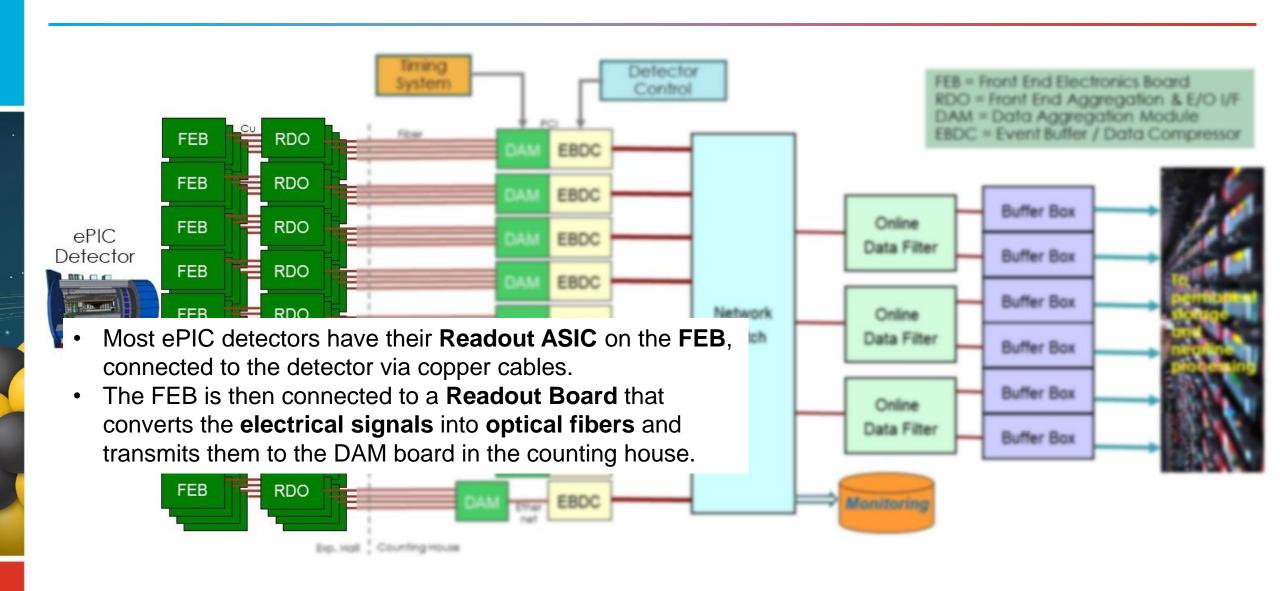

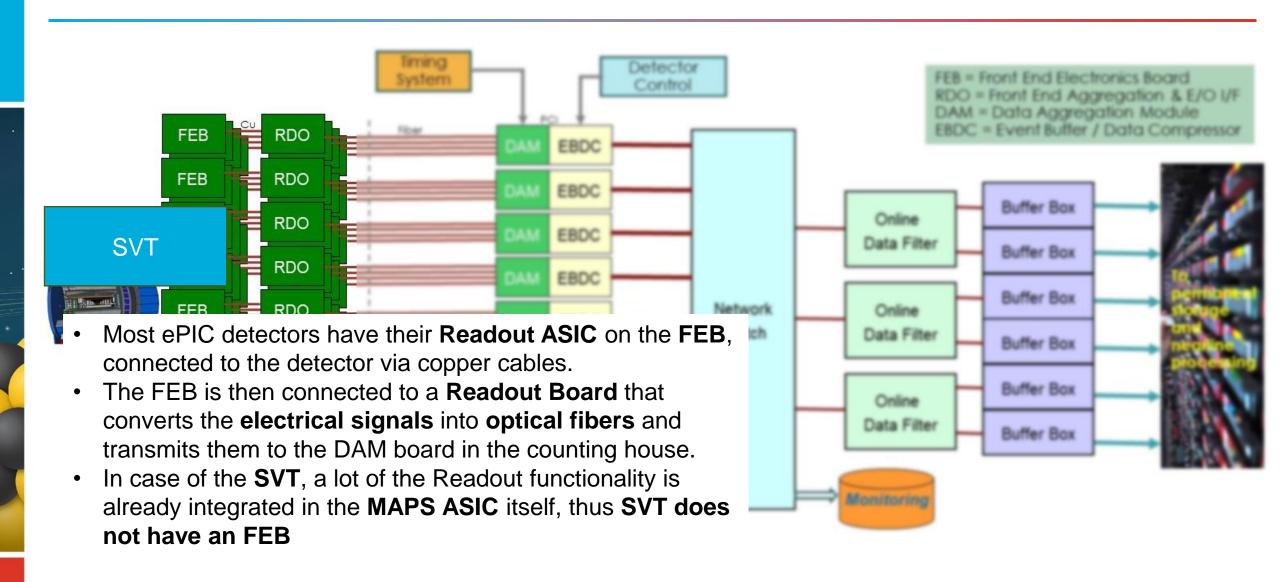

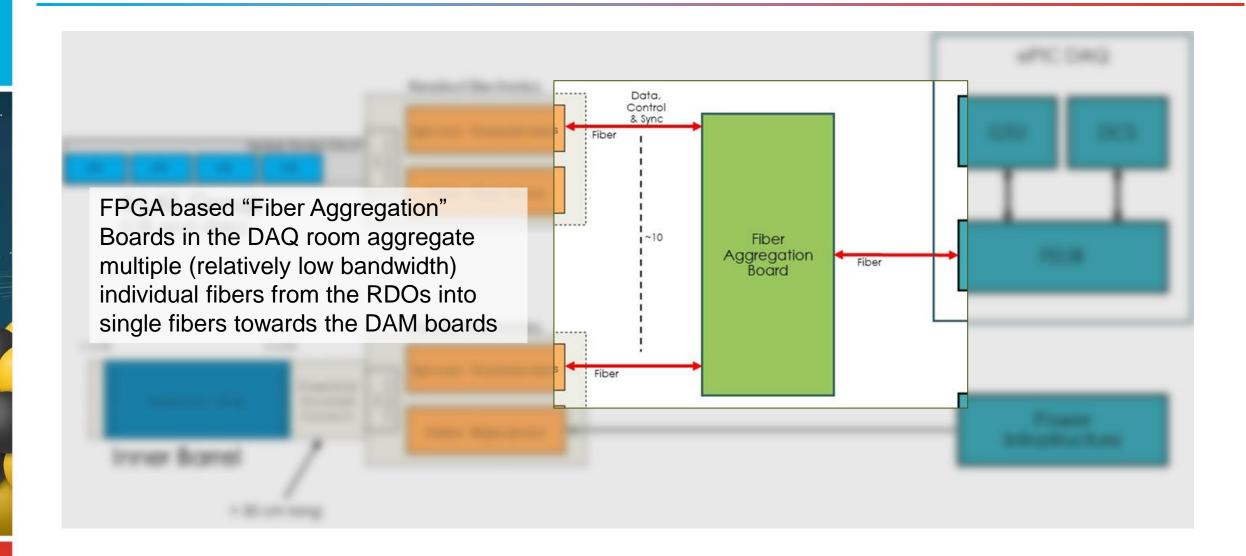

# ePIC Streaming DAQ for SVT

## ePIC Streaming DAQ for SVT

## ePIC Streaming DAQ for SVT

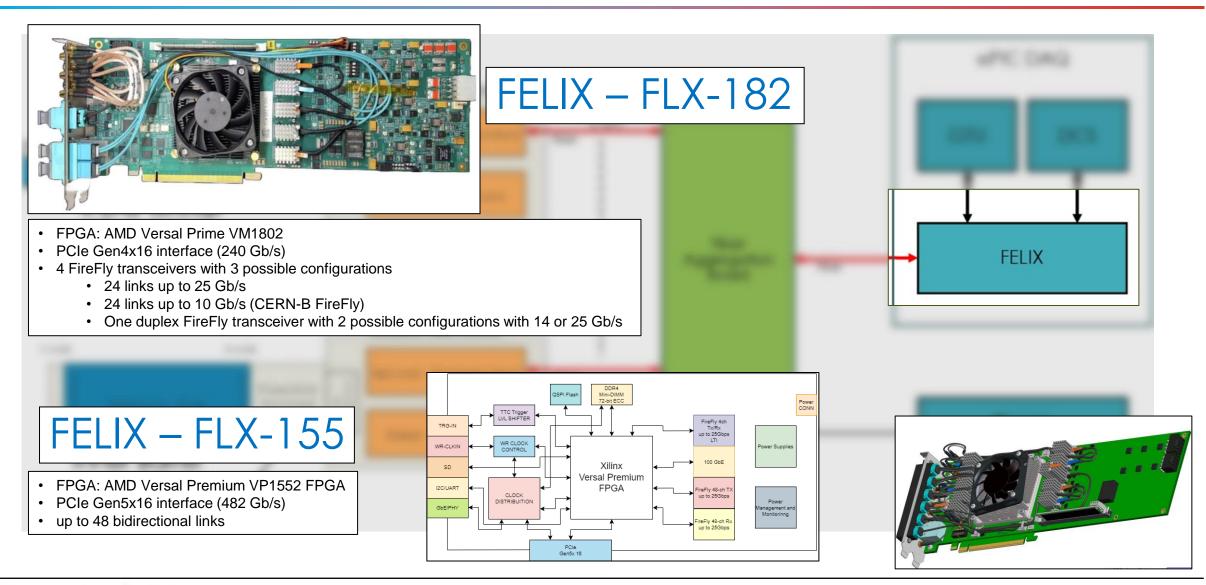

# **Backend: ATLAS FELIX Development for Phase-2 Upgrade**

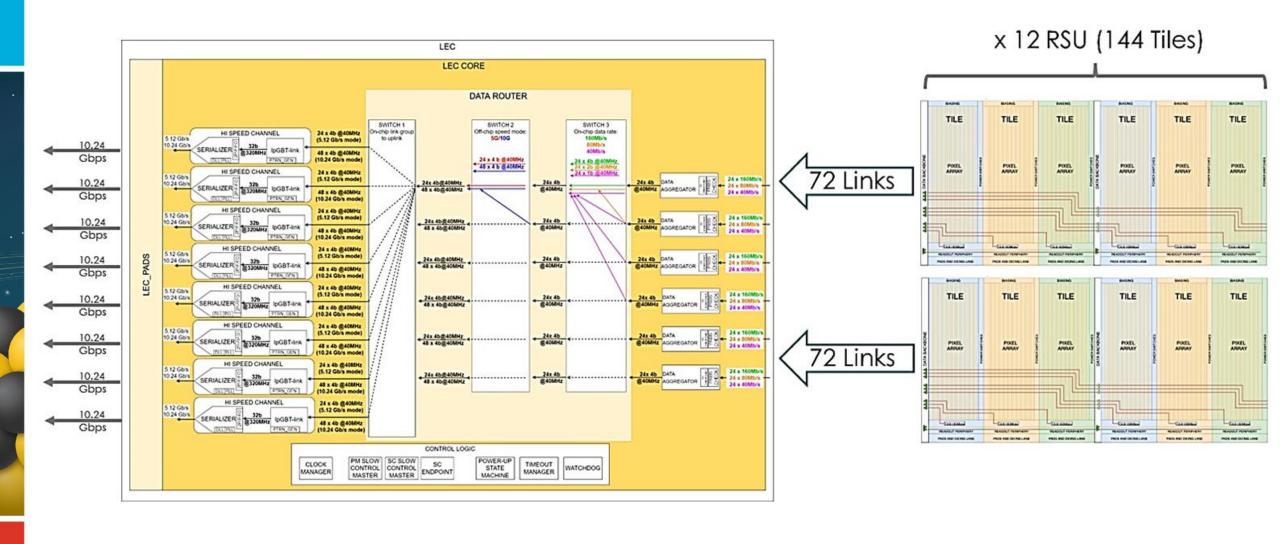

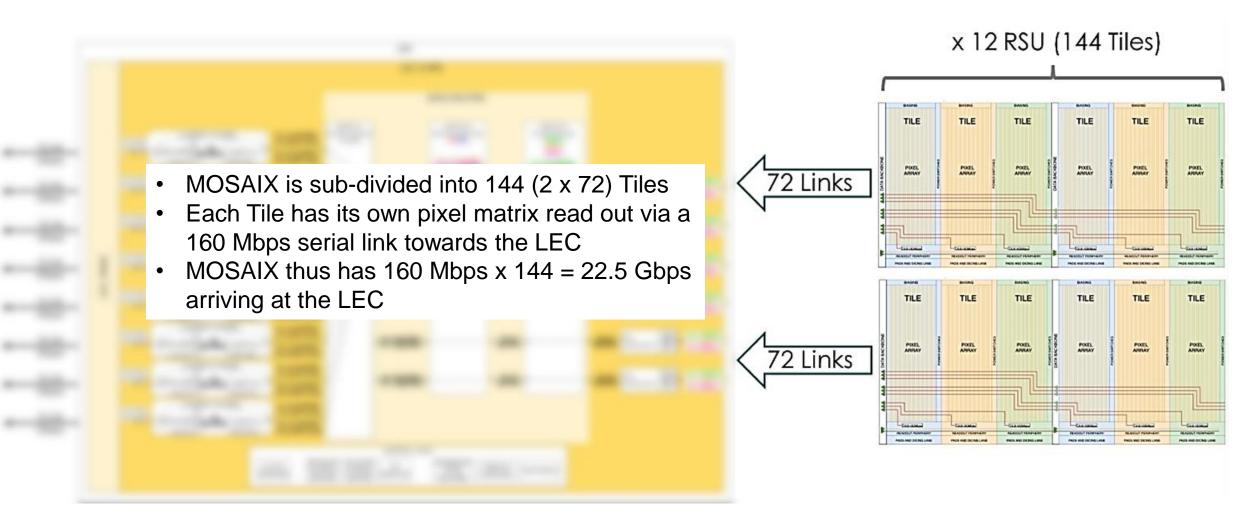

## Inner Barrel: MOSAIX Readout

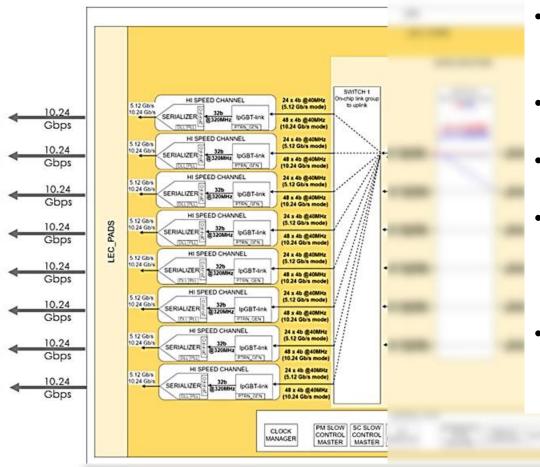

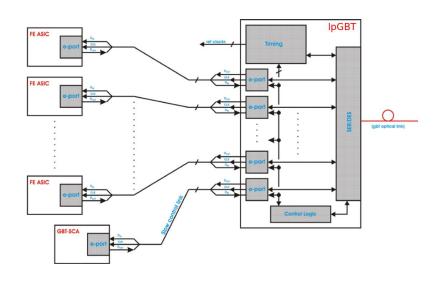

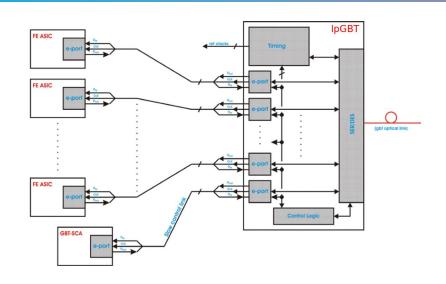

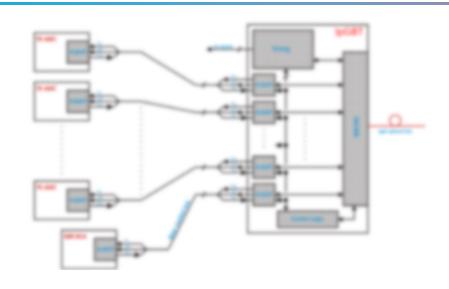

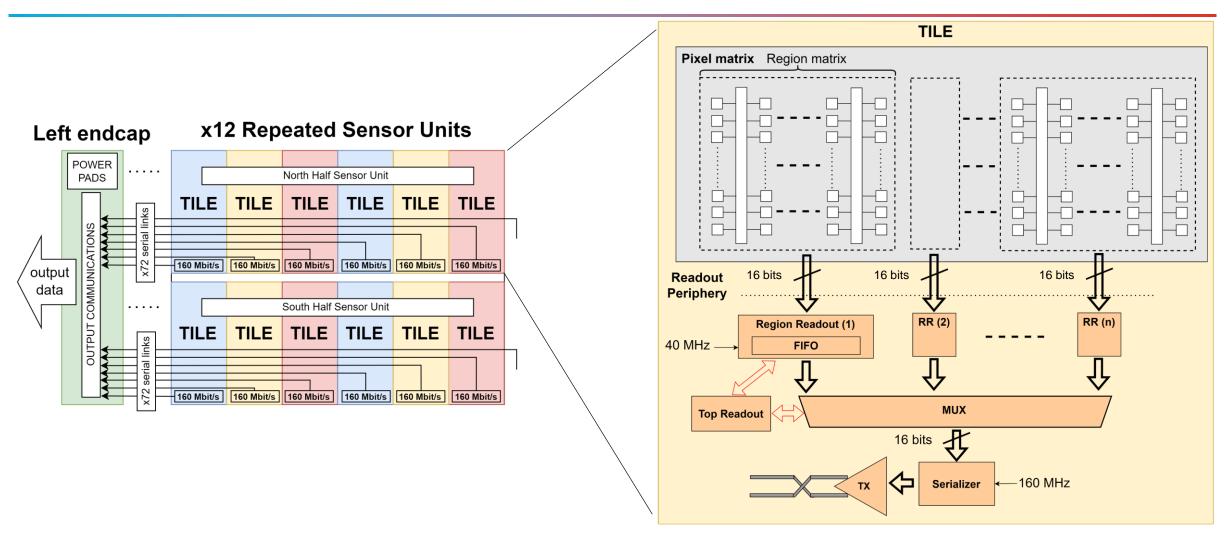

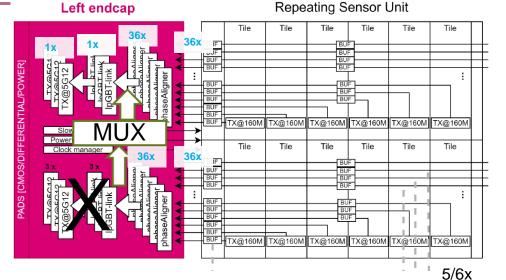

- In the LEC, the tile serial links are received and aligned

- Via a switch matrix, the data can then selectively be sent to individual encoders and off-chip serializers

- The data are then encoded with IpGBT IPs (providing a radiation tolerant protocol) and serialized to be shipped off the sensor via 10.24 Gbps links.

- The MOSAIX design contains a total of 8 encoders and serializers, providing a total 80 Gbps bandwidth.

- A fallback option is to run the serializers at 5.12 Gbps, thus still providing 40 Gbps.

- This provides high redundancy for the 22.5 Gbps

payload from the tiles in case of radiation damage; the

switch matrix can be programmed with different (fixed)

routing to mitigate the impact of failed components.

- In case of the SVT **LAS**, only **one serializer** is foreseen in the design due to the much lower payload requirements in these sensors.

#### Downlink

Data Uplink

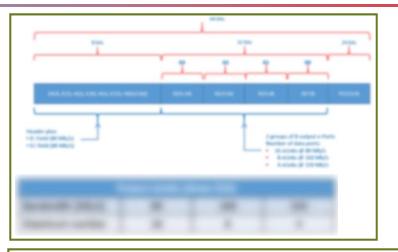

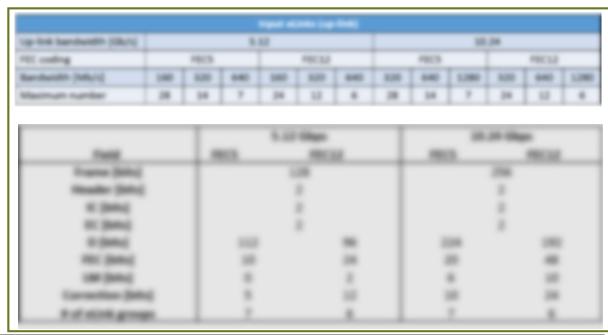

| Input eLinks (up-link)              |     |             |   |       |     |     |      |     |      |       |     |      |  |

|-------------------------------------|-----|-------------|---|-------|-----|-----|------|-----|------|-------|-----|------|--|

| Up-link bandwidth [Gb/s] 5.12 10.24 |     |             |   |       |     |     |      |     |      |       |     |      |  |

| FEC coding                          |     | FEC5        |   | FEC12 |     |     | FEC5 |     |      | FEC12 |     |      |  |

| Bandwidth [Mb/s]                    | 160 | 160 320 640 |   | 160   | 320 | 640 | 320  | 640 | 1280 | 320   | 640 | 1280 |  |

| Maximum number                      | 28  | 14          | 7 | 24    | 12  | 6   | 28   | 14  | 7    | 24    | 12  | 6    |  |

|                   | 5.1  | 2 Gbps | 10.24 Gbps |       |  |  |

|-------------------|------|--------|------------|-------|--|--|

| Field             | FEC5 | FEC12  | FEC5       | FEC12 |  |  |

| Frame [bits]      |      | 128    | 256        |       |  |  |

| Header [bits]     |      | 2      |            | 2     |  |  |

| IC [bits]         |      | 2      | 2          |       |  |  |

| EC [bits]         |      | 2      | 2          |       |  |  |

| D [bits]          | 112  | 96     | 224        | 192   |  |  |

| FEC [bits]        | 10   | 24     | 20         | 48    |  |  |

| LM [bits]         | 0    | 2      | 6          | 10    |  |  |

| Correction [bits] | 5    | 12     | 10         | 24    |  |  |

| # of eLink groups | 7    | 6      | 7          | 6     |  |  |

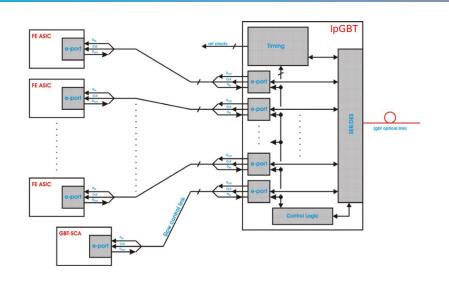

- Front Ends connect to "e-links"

- The fiber protocol includes "Forward Error Correction"

- Front Ends connect to "e-links"

- The fiber protocol includes "Forward Error Correction"

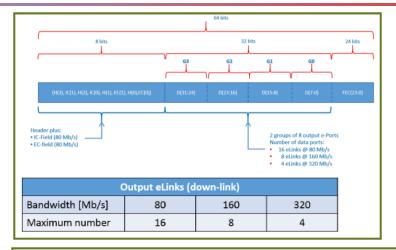

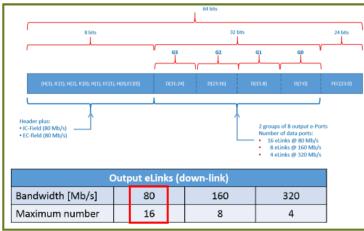

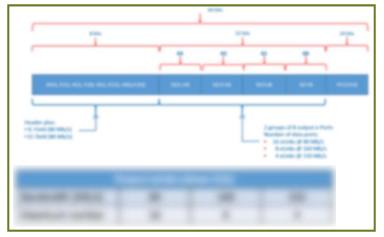

- Downlink runs at 2.56 Gbps

- Downlink frame is 64bit wide, of which 32 bits are payload

- 1.28 Gbps payload

- Up to 16 e-links @ 80 Mbps

#### Downlink

Line Rate: **2.56 Gbps** 32 out of 64 bits are data: Payload = **1.280 Gbps**

Data Uplink

- Front Ends connect to "e-links"

- The fiber protocol includes "Forward Error Correction"

- Downlink runs at 2.56 Gbps

- Downlink frame is 64bit wide, of which 32 bits are payload

- 1.28 Gbps payload

- Up to 16 e-links @ 80 Mbps

- Uplink runs at either 10.24 Gbps or 5.12 Gbps

- Uplink frame is either 128bit or 256bit

- 256bit frame contains 192bits of payload (7.68 Gbps)

- Up to 24 e-links at either 160 Mbps or 320 Gbps

#### Downlink

Line Rate: **2.56 Gbps** 32 out of 64 bits are data: Payload = **1.280 Gbps**

#### Data Uplink

192 out of 256 bits are data: Payload = **7.680 Gbps**

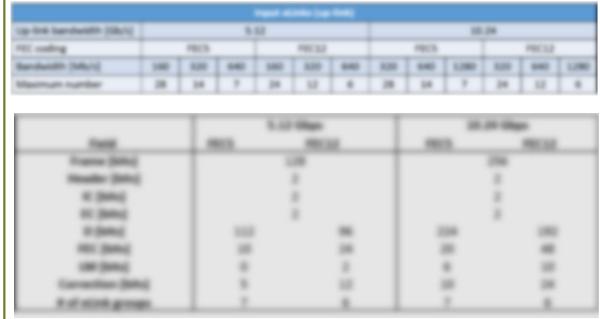

| Input eLinks (up-link)   |         |             |    |       |     |         |      |     |      |       |     |      |  |

|--------------------------|---------|-------------|----|-------|-----|---------|------|-----|------|-------|-----|------|--|

| Up-link bandwidth [Gb/s] |         | 5.12 10.24  |    |       |     |         |      |     |      |       |     |      |  |

| FEC coding               | FEC5    |             |    | FEC12 |     |         | FEC5 |     |      | FEC12 |     |      |  |

| Bandwidth [Mb/s]         | 160     | 160 320 640 |    | 160   | 320 | 640     | 320  | 640 | 1280 | 320   | 640 | 1280 |  |

| Maximum number           | 28 14 7 |             | 24 | 12 6  |     | 28 14 7 |      | 7   | 24   | 12    | 6   |      |  |

|                   | 5.1  | 12 Gbps |      | 10.24 Gbps |  |

|-------------------|------|---------|------|------------|--|

| Field             | FEC5 | FEC12   | FEC5 | FEC12      |  |

| Frame [bits]      |      | 128     |      | 256        |  |

| Header [bits]     |      | 2       |      | 2          |  |

| IC [bits]         |      | 2       |      | 2          |  |

| EC [bits]         |      | 2       |      | 2          |  |

| D [bits]          | 112  | 96      | 224  | 192        |  |

| FEC [bits]        | 10   | 24      | 20   | 48         |  |

| LM [bits]         | 0    | 2       | 6    | 10         |  |

| Correction [bits] | 5    | 12      | 10   | 24         |  |

| # of eLink groups | 7    | 6       | 7    | 6          |  |

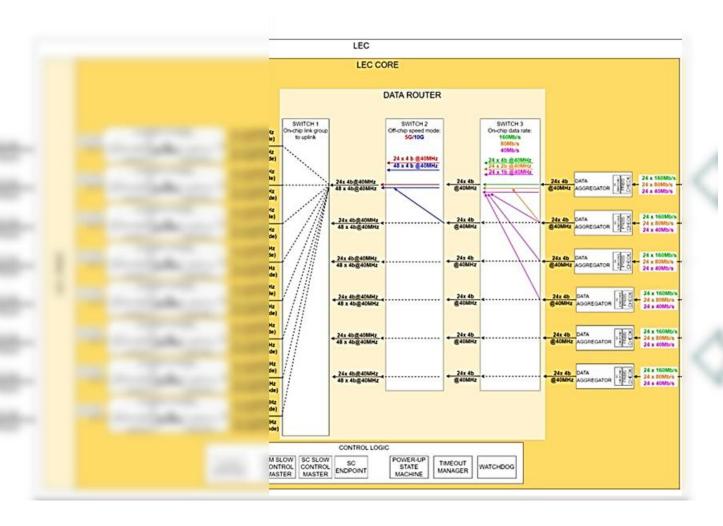

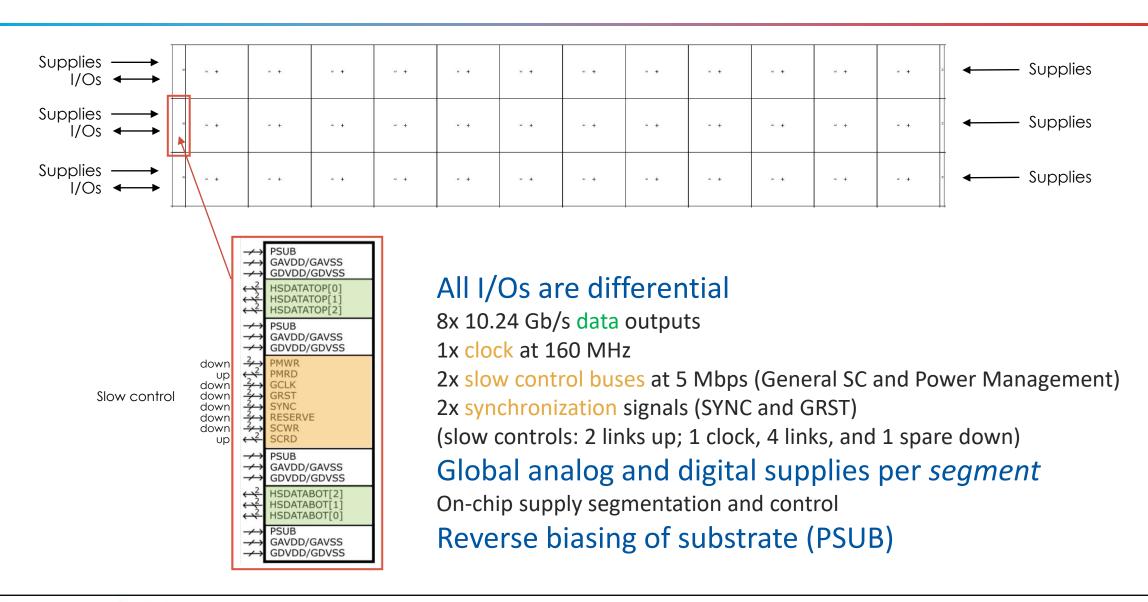

### **MOSAIX** Interfaces in the Left End Cap (LEC)

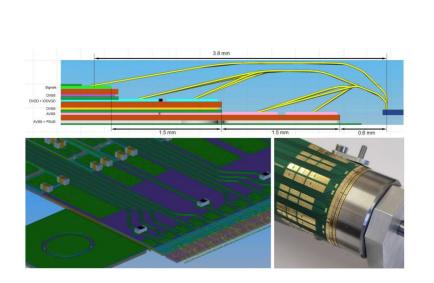

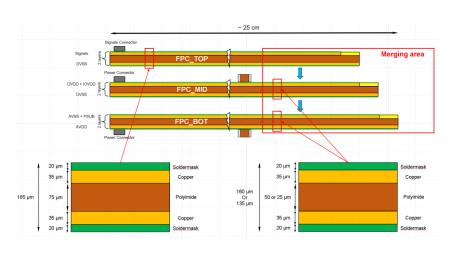

# ITS3 Flex PC Design: Inspiration for SVT IB FPC design

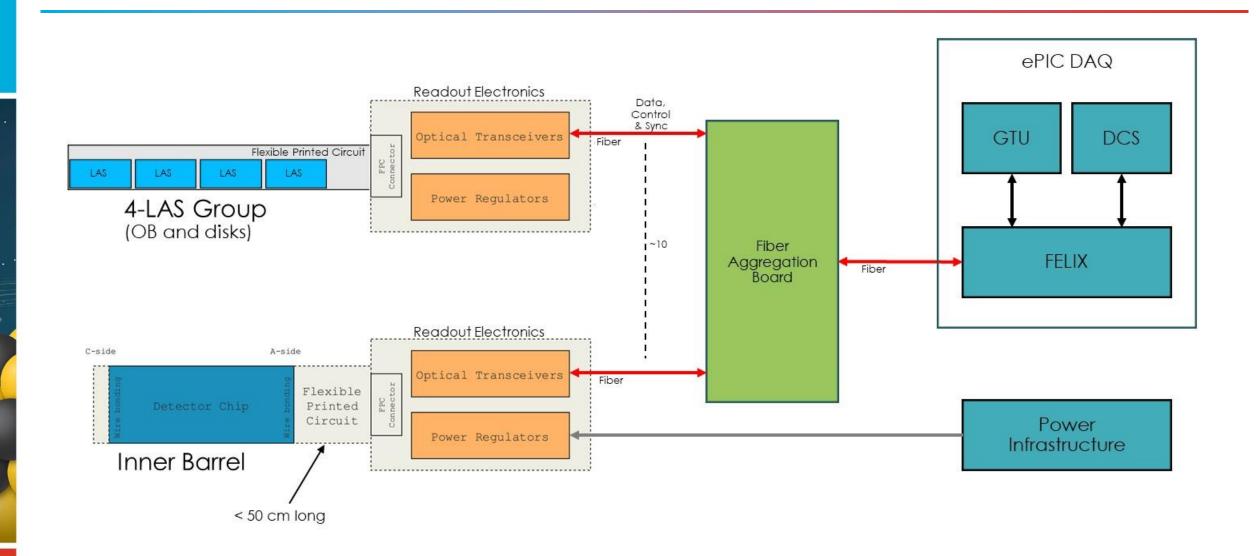

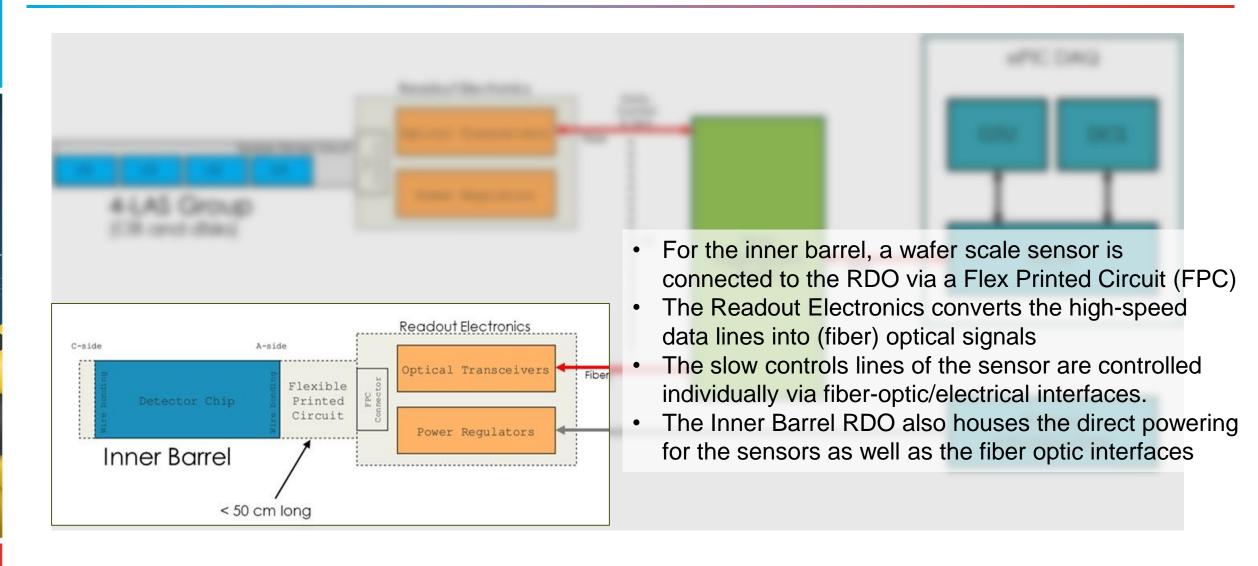

# Inner Barrel Readout Electronics (inspired by ITS-3 DSE)

Electron-Ion Collider

# Inner Barrel Readout Electronics (inspired by ITS-3 DSE)

Electron-Ion Collider

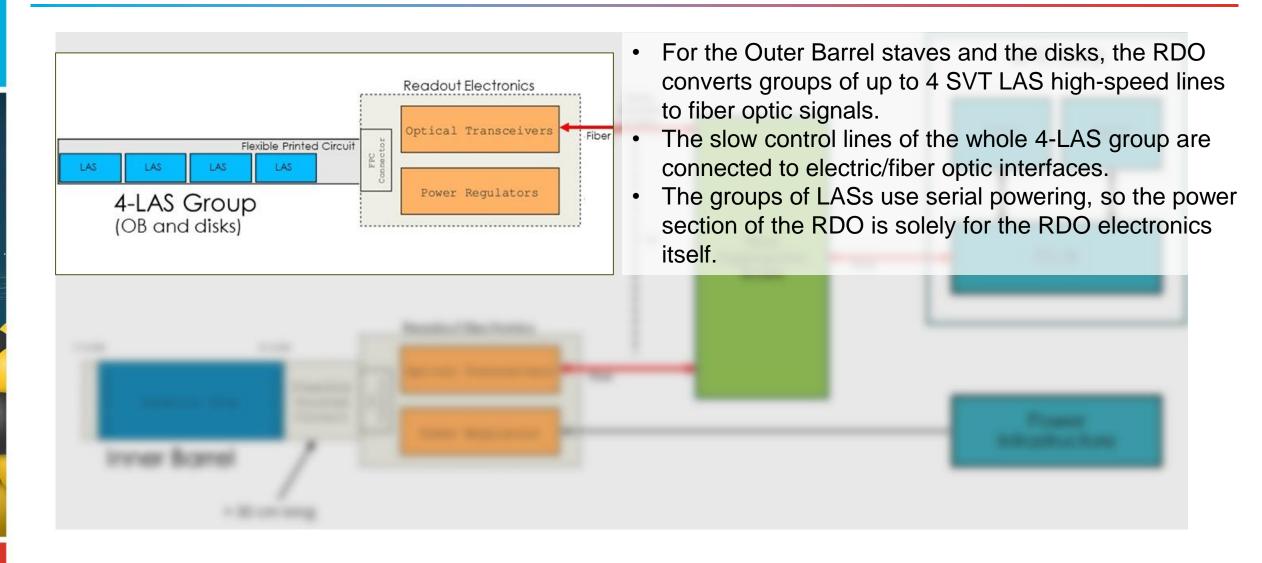

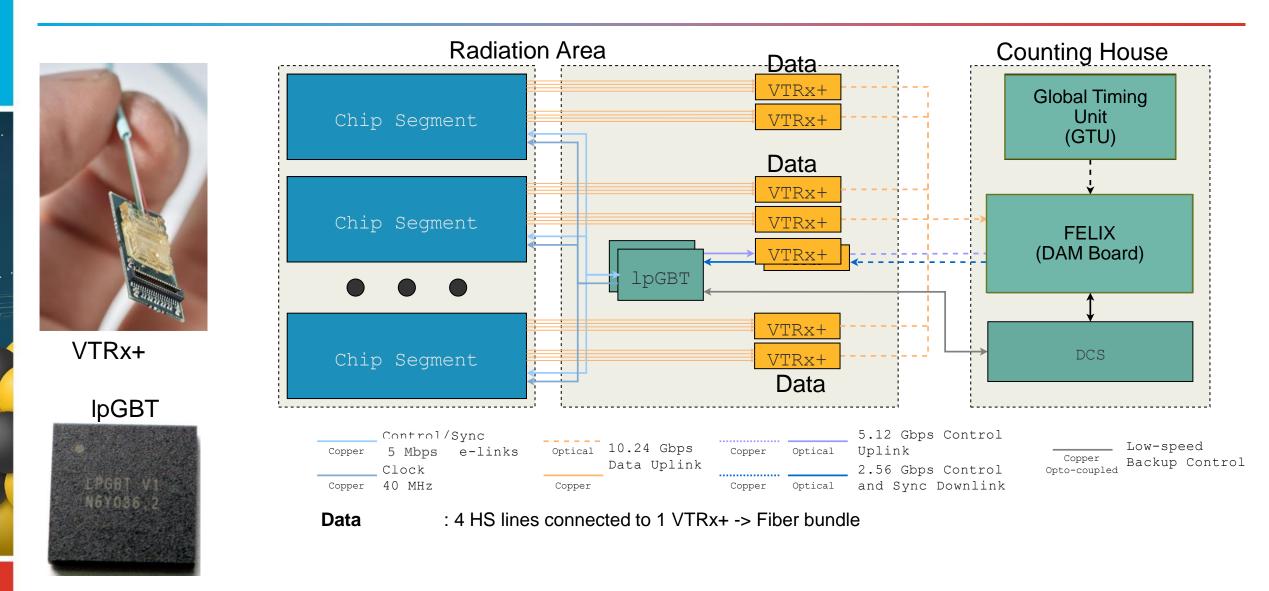

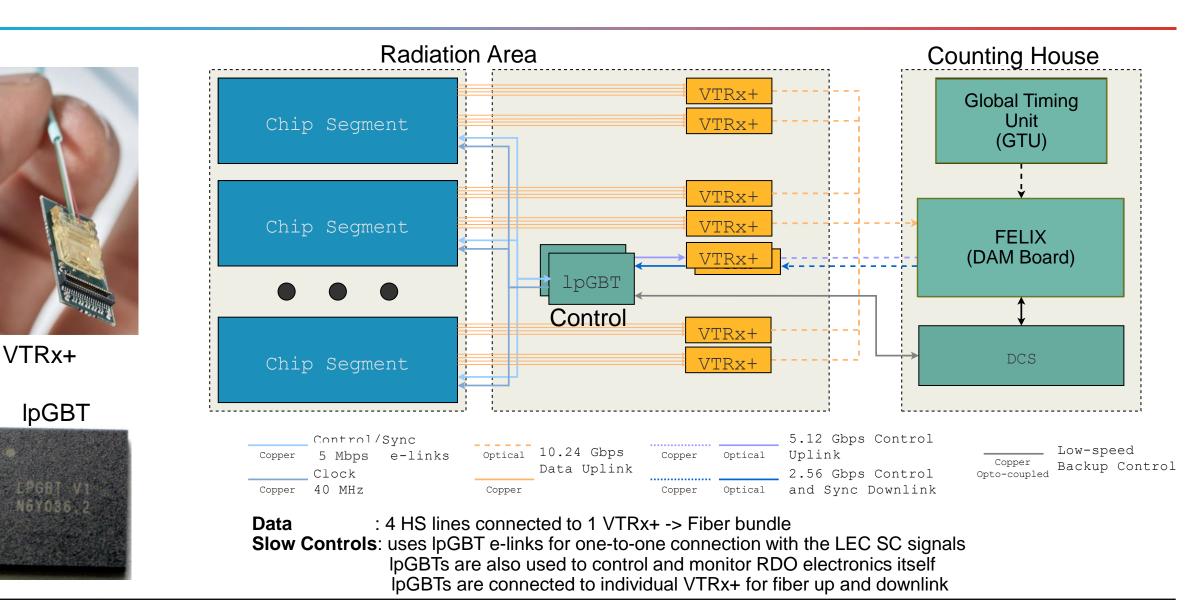

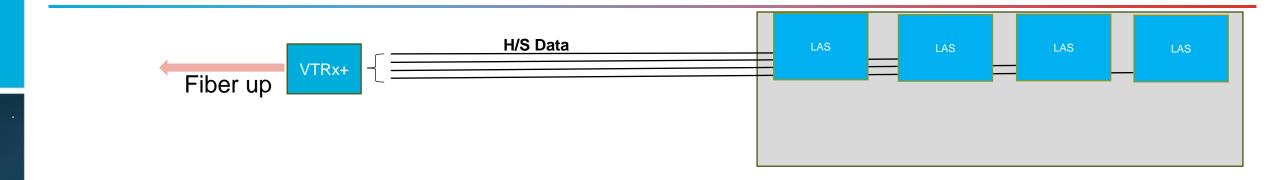

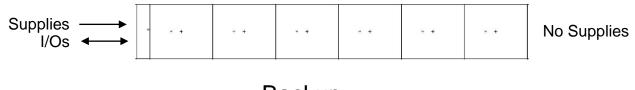

## Outer Barrel & Disk LAS Readout

#### **Outer Barrel and Disk Readout Electronics**

#### **Disks & Staves:**

Up to 4 LAS connect their **H/S data** to **one** VTRx+

#### **Outer Barrel and Disk Readout Electronics**

Electron-Ion Collider

Tracking Detectors Review, March 20-21, 2024

## **SVT Readout Numbers**

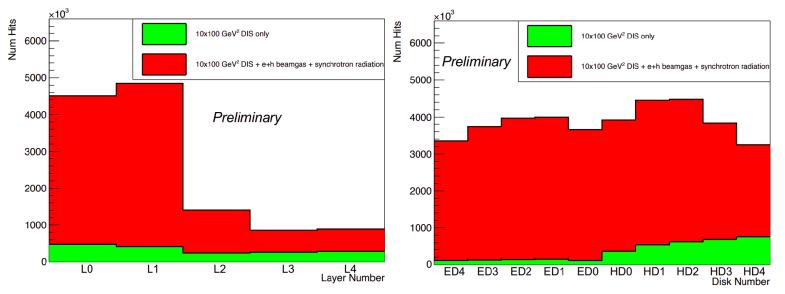

#### **SVT Hit Rate Simulations**

- 10x100 GeV ep, 4.48 x 10<sup>33</sup> cm<sup>-2</sup>s<sup>-1</sup>, 184 kHz DIS event rate

- 10 GeV SR

- 10 GeV e-beam gas, 10000 Ahr

- 100 GeV proton-beam gas, 100 Ahr

|    | Hit Rate (Hz) | Area (cm <sup>2</sup> ) | Hits/s/cm <sup>2</sup> |

|----|---------------|-------------------------|------------------------|

| L0 | 4.50E+06      | 610.73                  | 7.37E+03               |

| L1 | 4.85E+06      | 814.30                  | 5.96E+03               |

| L2 | 1.41E+06      | 2035.75                 | 6.93E+02               |

| L3 | 8.55E+05      | 9160.88                 | 9.33E+01               |

| L4 | 8.89E+05      | 22167.08                | 4.01E+01               |

|     | Hit Rate (Hz) | Area (cm <sup>2</sup> ) | Hits/s/cm <sup>2</sup> |

|-----|---------------|-------------------------|------------------------|

| ED0 | 3.66E+05      | 1767.11                 | 2.07E+02               |

| ED1 | 4.00E+06      | 5368.16                 | 7.45E+02               |

| ED2 | 3.97E+06      | 5536.32                 | 7.17E+02               |

| ED3 | 3.74E+06      | 5532.26                 | 6.76E+02               |

| ED4 | 3.35E+06      | 5524.62                 | 6.06E+02               |

|     | Hit Rate (Hz) | Area (cm²) | Hits/s/cm <sup>2</sup> |

|-----|---------------|------------|------------------------|

| HD0 | 3.92E+06      | 1767.11    | 2.22E+03               |

| HD1 | 4.45E+06      | 5368.16    | 8.29E+02               |

| HD2 | 4.48E+06      | 5533.75    | 8.10E+02               |

| HD3 | 3.83E+06      | 5513.51    | 6.95E+02               |

| HD4 | 3.25E+06      | 5486.76    | 5.92E+02               |

# **SVT** by the numbers

|              | width (mm) | length (mm)  |         | # pixels per RSU |          |           |              |              |                  |         |            |           |          |        |      |              |             |

|--------------|------------|--------------|---------|------------------|----------|-----------|--------------|--------------|------------------|---------|------------|-----------|----------|--------|------|--------------|-------------|

| Reticle size | 19.564     | 21.666       |         | 827,424          |          |           |              |              |                  |         |            |           |          |        |      |              |             |

| Pixel size   | 0.0208     | 0.0228       |         |                  |          |           |              |              |                  |         |            |           |          |        |      |              |             |

|              |            |              |         |                  |          |           |              |              |                  |         |            |           |          |        |      |              |             |

| Barrel       |            |              |         |                  | Se       | ensor     |              |              |                  |         |            |           |          |        |      | 10x27        | '5GeV       |

|              | radius     | , ,          |         |                  |          |           | # of sensors |              |                  | #       |            | # Readout |          | # Data | # SC |              | Hits/pixel/ |

| Layer Index  | ` '        | z (mm)       |         |                  | in width |           |              | sensors in z |                  | sensors | Notes      |           | # Staves |        |      | Hit Rate / s |             |

| L0           | 36         |              |         | 58,811           |          |           |              |              | 119,149,056      |         | bent ITS3  | 96        |          | 24     |      | 2.73E+07     |             |

| L1           | 48         |              |         | 78,414           |          | 12        |              | -            | 158,865,408      |         | bent ITS3  | 128       |          | 32     |      | 2.94E+07     | -           |

| L2           | 120        |              |         | 196,035          |          |           |              | 1            | 397,163,520      |         | bent ITS3  | 320       |          | 80     |      | 8.55E+06     |             |

| L3           | 270        |              |         | 882,158          |          | 6         |              |              | 1,906,384,896    |         | 6 -RSU LAS | 384       |          | 96     |      | 5.19E+06     |             |

| L4           | 420        | 840          |         | 2,216,706        | 1        | 5         | 148          | 8            | 4,898,350,080    | 1184    | 5-RSU LAS  | 1184      | 74       | 296    | 25   | 5.39E+06     | 2.05E-09    |

| e-endcap     |            |              |         |                  |          |           |              |              |                  |         |            |           |          |        |      |              |             |

|              |            |              | outer r |                  |          |           |              |              |                  |         |            |           | Readout  |        |      |              |             |

| Disk index   | z (mm)     | inner r (mm) | (mm)    |                  |          | 5-RSU LAS | 6-RSU LAS    |              |                  |         |            |           | Groups   |        |      |              |             |

| ED0          | -250       | ` '          | 240     | 176,710          |          | 56        | 40           |              | 337,588,992      | 96      | 5-RSU LAS  | 96        |          | 26     | 3    | 2.22E+06     | 1.22E-08    |

| ED1          | -450       | 36.76        | 415     |                  |          | 334       | 0            |              | 1,381,798,080    | 334     | 5-RSU LAS  | 334       | 96       | 96     | 8    | 2.43E+07     | 3.27E-08    |

| ED2          | -650       | 36.76        | 421.4   |                  |          | 334       | 0            |              | 1,381,798,080    | 334     | 5-RSU LAS  | 334       | 96       | 96     | 8    | 2.41E+07     | 3.24E-08    |

| ED3          | -850       |              | 421.4   |                  |          | 334       | 0            |              | 1,381,798,080    | 334     | 5-RSU LAS  | 334       | 96       | 96     |      | 2.27E+07     |             |

| ED4          | -1050      | 46.3529      | 421.4   |                  |          | 334       | 0            |              | 1,381,798,080    |         | 5-RSU LAS  | 334       | 96       | 96     |      | 2.03E+07     | 2.74E-08    |

|              |            |              |         |                  |          |           |              |              |                  |         |            |           |          |        |      |              |             |

| h-endcap     |            |              |         |                  |          |           |              |              |                  |         |            |           |          |        |      |              |             |

| Disk index   |            |              |         |                  |          |           |              |              |                  |         |            |           |          |        |      |              |             |

| HD0          | 250        | 36.76        | 240     | 176,710          |          | 56        | 40           |              | 337,588,992      | 96      | 5-RSU LAS  | 96        | 26       | 26     | 3    | 2.38E+07     | 1.31E-07    |

| HD1          | 450        | 36.76        | 415     | 536,815          |          | 334       | 0            |              | 1,381,798,080    | 334     | 5-RSU LAS  | 334       | 96       | 96     | 8    | 2.70E+07     | 3.63E-08    |

| HD2          | 700        | 38.52        | 421.4   | 553,216          |          | 334       | 0            |              | 1,381,798,080    | 334     | 5-RSU LAS  | 334       | 96       | 96     | 8    | 2.72E+07     | 3.66E-08    |

| HD3          | 1000       | 53.43        | 421.4   | 548,909          |          | 334       | 0            |              | 1,381,798,080    | 334     | 5-RSU LAS  | 334       | 96       | 96     | 8    | 2.32E+07     | 3.13E-08    |

| HD4          | 1350       | 70.14        | 421.4   | 542,422          |          | 334       | 0            |              | 1,381,798,080    | 334     | 5-RSU LAS  | 334       | 96       | 96     | 8    | 1.97E+07     | 2.65E-08    |

|              |            |              |         |                  |          |           |              |              |                  |         |            |           |          |        |      |              |             |

| TOTAL        |            |              |         | 8,161,315        |          |           |              |              | 19,209,475,584   | 4448    |            | 4976      |          | 1348   | 132  | 2.90E+08     | hite/e      |

| IOTAL        |            |              |         | 0,101,313        |          |           |              |              | 19,209,475,564   | 4440    |            | 4970      | )        | 1340   | 132  |              | Gbps        |

|              |            |              |         |                  |          |           |              |              | # of segments:   | 4500    |            |           |          |        |      |              |             |

|              |            |              |         |                  |          |           |              |              | # of SC links    |         |            |           |          |        |      | nluc         | noico       |

|              |            |              |         |                  |          |           |              |              | down             | 22500   |            |           |          |        |      | plus         | 110126      |

|              |            |              |         |                  |          |           |              |              | # of SC links up | 9000    |            |           |          |        |      |              |             |

# **SVT Readout Prototype Developments**

#### **SVT Prototype Developments**

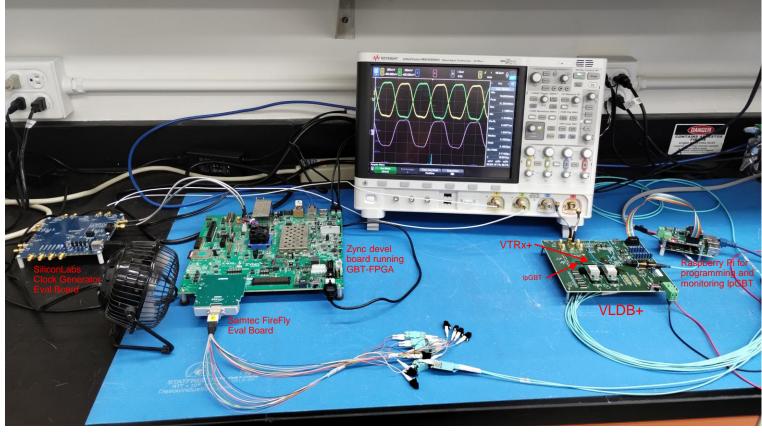

- A full setup with IpGBT, VTRx+, and FPGA development boards (stand-ins for FELIX) exists at ORNL for evaluation of the various RDO components.

- Alternatives to CERN's IpGBT universe of components using commercial alternatives are being investigated.

- First results with these setups have been achieved in the context of an R&D project concerned with the Silicon using EIC project funds.

- Evaluation of the Samtec Optical FireFly as an alternative to VTRx+

- Evaluation of the Microchip PolarFire FPGA as a radiation-tolerant FPGA replacement of the lpGBT

- Evaluation of Aggregator Board architectures with commercial FPGA development boards has been started at MIT in the context of the Silicon R&D project.

- A test setup for the characterization of CERN Engineering Run chiplets to be used in the MOSAIX and LAS designs is under development.

- Investigations on Redundancy issues on the LAS design interfaces has started.

- Work is ongoing on defining the details of the LAS physical and protocol interfaces.

# Commercial Alternatives: FireFly & PolarFire

|                |                                         | MPF050 | MPF100 | MPF200 | MPF300 | MPF500 |

|----------------|-----------------------------------------|--------|--------|--------|--------|--------|

|                | Logic Elements (4LUT + DFF)             | 48K    | 109K   | 192K   | 300K   | 481K   |

|                | Math Blocks (18 × 18 MACC)              | 150    | 336    | 588    | 924    | 1480   |

|                | LSRAM Blocks (20 Kb)                    | 160    | 352    | 616)   | 952    | 1520   |

| FPGA Fabric    | uSRAM Blocks (64 × 12)                  | 450    | 1008   | 1764   | 2772   | 4440   |

|                | Total RAM (Mb)                          | 3.6    | 7.6    | 13.3   | 20.6   | 33     |

|                | uPROM (Kb)                              | 216    | 297    | 297    | 459    | 513    |

|                | User DLLs/PLLs                          | 8      | 8 each | 8 each | 8 each | 8 each |

| High-Speed I/O | 250 Mbps–12.7 Gbps Transceiver<br>Lanes | 4      | 8      | 16     | 16     | 24     |

|                | PCIe® Gen 2 Endpoints/Root Ports        | 2      | 2      | 2      | 2      | 2      |

| Total I/O      | Total User I/O                          | 176    | 296    | 364    | 512    | 584    |

## **eRD104 Test Setups**

PolarFire Gigabit Transceiver Test Setup

Samtec FireFly Test Setup with Fiber Loopback

IpGBT Test Setup with Samtec FireFly (VTRx+ alternative), Xilinx Ultrascale FPGA evaluation board ("FELIX), and SiliconLabs Clock Generator Board ("GTU")

#### Electron-Ion Collider

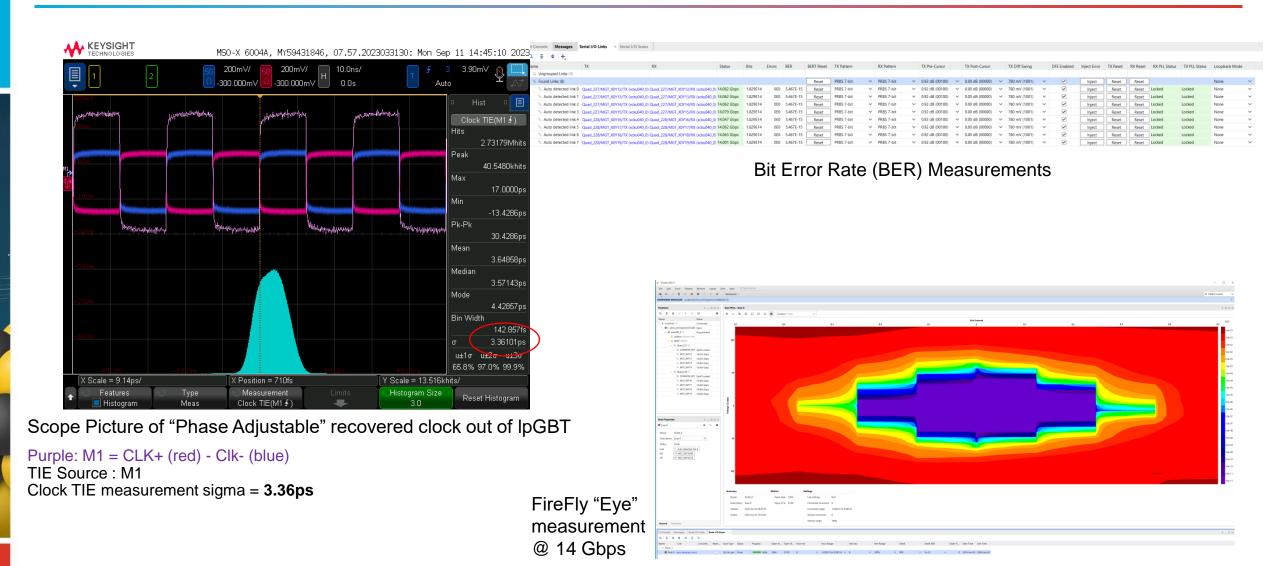

#### **Selected Test Results:**

Electron-Ion Collider

Tracking Detectors Review, March 20-21, 2024

### **Summary**

- An SVT Readout Design has been developed and demonstrated here

- Inner Barrel RDO based on ALICE ITS-3 Service Electronics Board Design

- Direct connection of multiple HS data serializers per segment to VTRx+

- One-to-One connection between IpGBT e-links and LEC signals for slow controls

- Direct powering of wafer scale sensor

- Outer Barrel RDO concept uses a concept of LAS Readout groups

- Group of up to 4 Single HS Data lines are directly connected to VTRx+

- Slow Controls multiplexed between groups of 4 LAS via AncASICs on each LAS on a single bus

- Prototype Setups are being investigated with evaluation boards of various components

- First results have already been shown running all components at the full desired speeds and show that sufficient performance is achieved

# **Backup Slides**

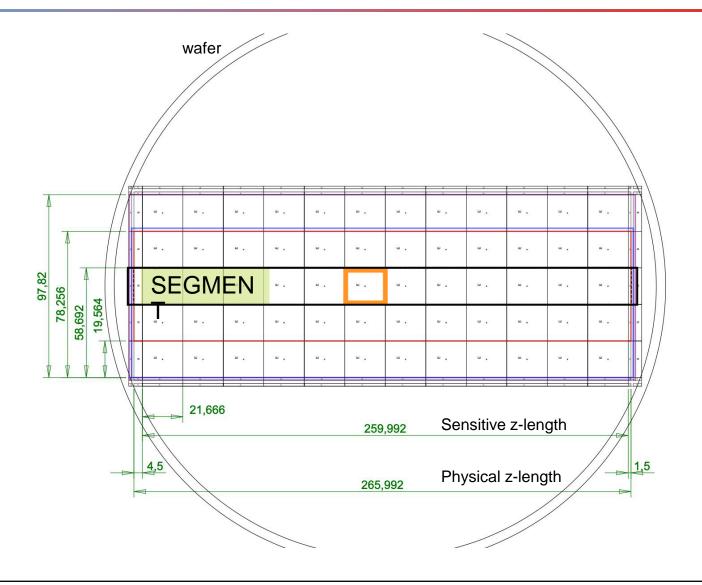

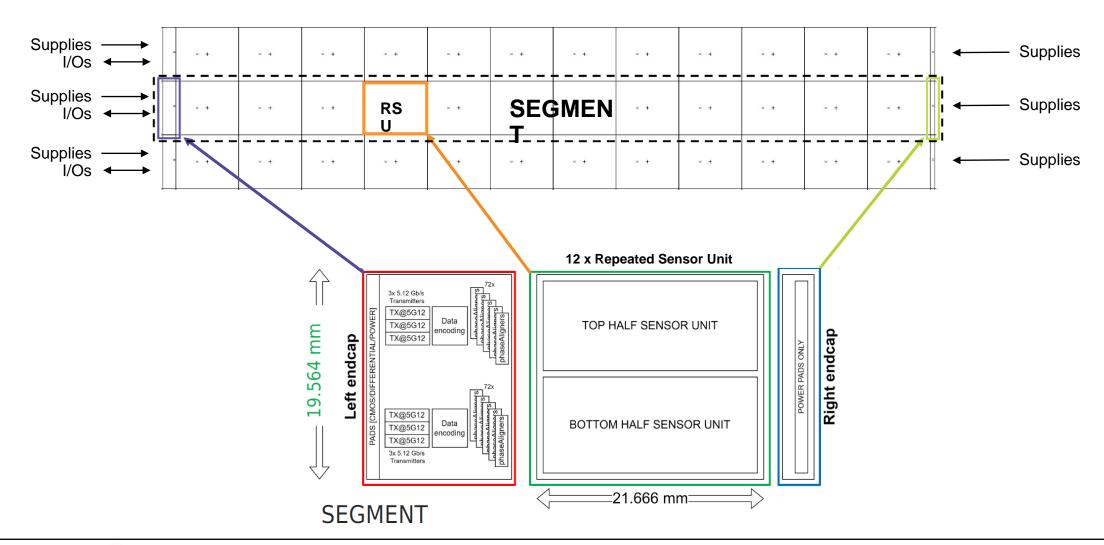

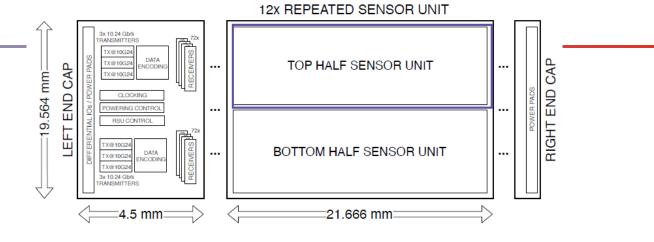

#### "MOSAIX" Stitched Sensor for SVT Inner Barrel

Layer 0: 12 x 3 repeated units + endcaps

Layer 1: 12 x 4 repeated units + endcaps

Layer 2: 12 x 5 repeated units + endcaps

Repeated (Stitched) Sensing Unit (RSU)

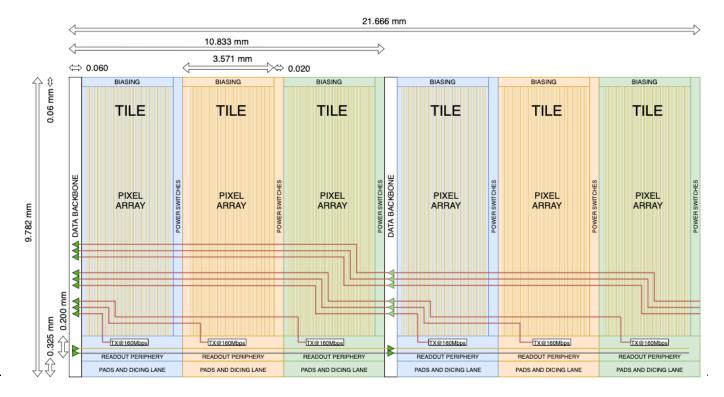

#### **MOSAIX Stitched Sensor Detail**

### **Half Repeated Sensor Unit**

Each Half Unit is segmented in **Tiles** (Domains)

#### Each tile acts as an independent sensor

Separate Local Power

Configuration

Readout Link (160 Mb/s)

Each **Tile** data output has direct connection to

the **left endcap**

#### **Tile Readout Scheme**

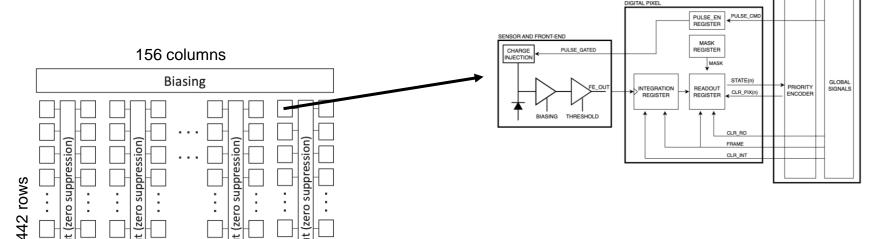

### **Pixel Array Readout Architecture**

442 x 156 pixels / domain 827,424 pixels per RSU 144 domains / segment 9.929 Mpixels / segment

**20.8 μm x 22.8 μm** pixel pitch

Continuously active front-end (40 nW typ.)

Global shutter

Zero-suppressed matrix readout

Continuous readout mode

Integration time: 2 / 5 / 10μs

#### In pixel:

Amplification

Discrimination

Hit integration register

readout register

Test charge injection

Digital pulsing

Masking

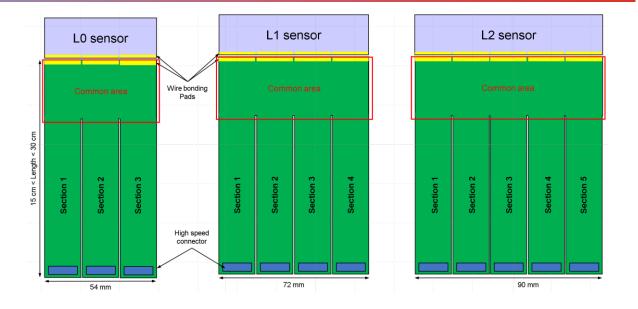

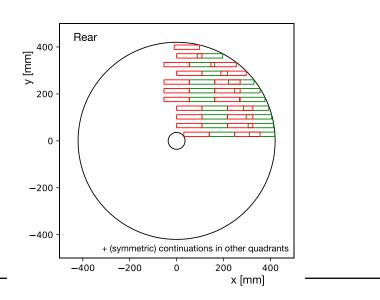

## ePIC SVT: "Large Area Sensor" (LAS)

#### 6-RSU LAS

- Inner Barrel (Layers 0,1,2) will reuse ITS3-like sensors as is

- Layer 0: 4 sensors in r-phi, 3 segments of 12 RSU

- Layer 1: 4 sensors in r-phi, 4 segments of 12 RSU

- Layer 2: 8 sensors in r-phi, 5 segments of 12 RSU

- EIC variant for the Outer Barrel (Layers 3,4) and Endcap Disks

- "Large Area Sensor" (LAS)

- Will be stitched, but not to wafer scale

- Likely 1 Segment of 5 or 6 RSU (no need for right endcap)

- The intention is to multiplex Tile data lines to 1 High-Speed output

- More conventional carbon composite mechanical support with integrated cooling

Backup

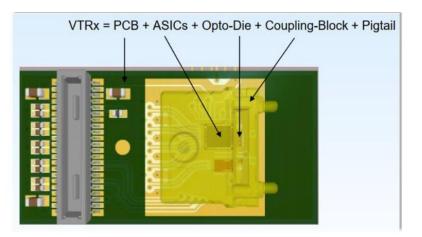

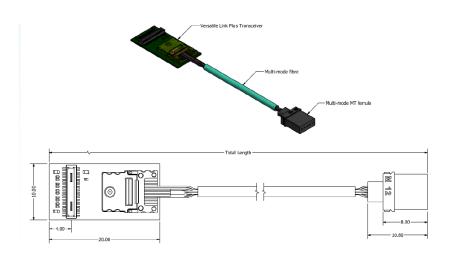

#### **VTRx+ Front-end Module**

- Versatile

- Up to 4 Tx + 1 Rx, configurable by masking channels

- Miniaturised

- 20 x 10 x 2.5 mm

- Pluggable

- Electrical connector

- Data-rate

- Tx: up to 4×10 Gb/s, Rx: 2.5 Gb/s

- Environment

- Temperature: -35 to + 60 °C

- Total Dose: 100 Mrad

- Total Fluence: 1x10<sup>15</sup> n/cm<sup>2</sup> and 1x10<sup>15</sup> hadrons/cm<sup>2</sup>

- Status

- Pre-production ongoing

- . Solving problems with module assembly

- Alignment of optical components

- Ramping up to 2k modules/month in 2023