ORNL is managed by UT-Battelle LLC for the US Department of Energy

## HGCROC usage in different calorimeters

#### Hadron Calorimeters:

- LFHCal:

- Main user, >60k channels

- Larger dynamic range because of the forward region, but also requirement for MIP (e.g. muon)

- 1.3x1.3 mm<sup>2</sup> SiPM's and 3x3 mm<sup>2</sup> SiPM's:

- Grouping (summing) in groups of 5 and 10 for input signal

- Insert:

- 3x3 mm2 on tile, single SiPM readout

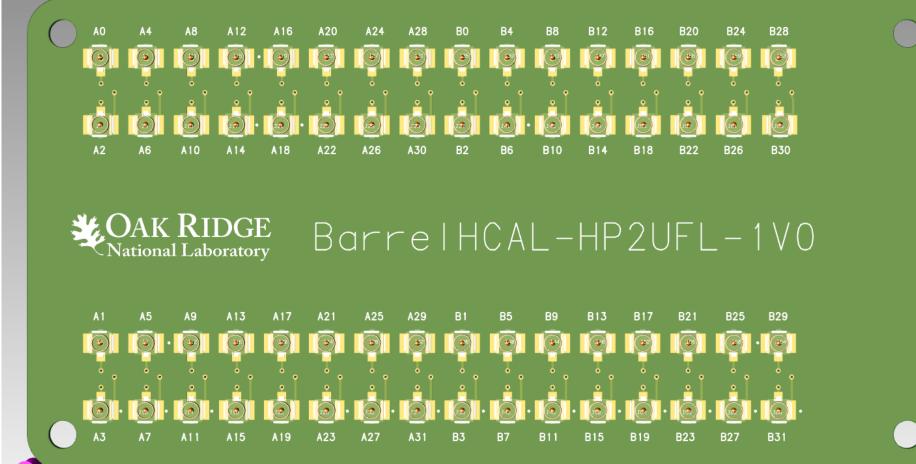

- Barrel HCal:

- 3x3 mm2 SiPM on tile

- Cable to the FEB (up to 2-3 m)

- Backward HCal:

- Work in progress, following LFHCal

- Electromagnetic Calorimeters:

- Barrel ECal:

- 4x4 Array of 3x3 mm2 SiPM's

- Timing will translate to position (100-150 µsec requirement)

- Small signal requirement for MIP detection

## Ongoing work

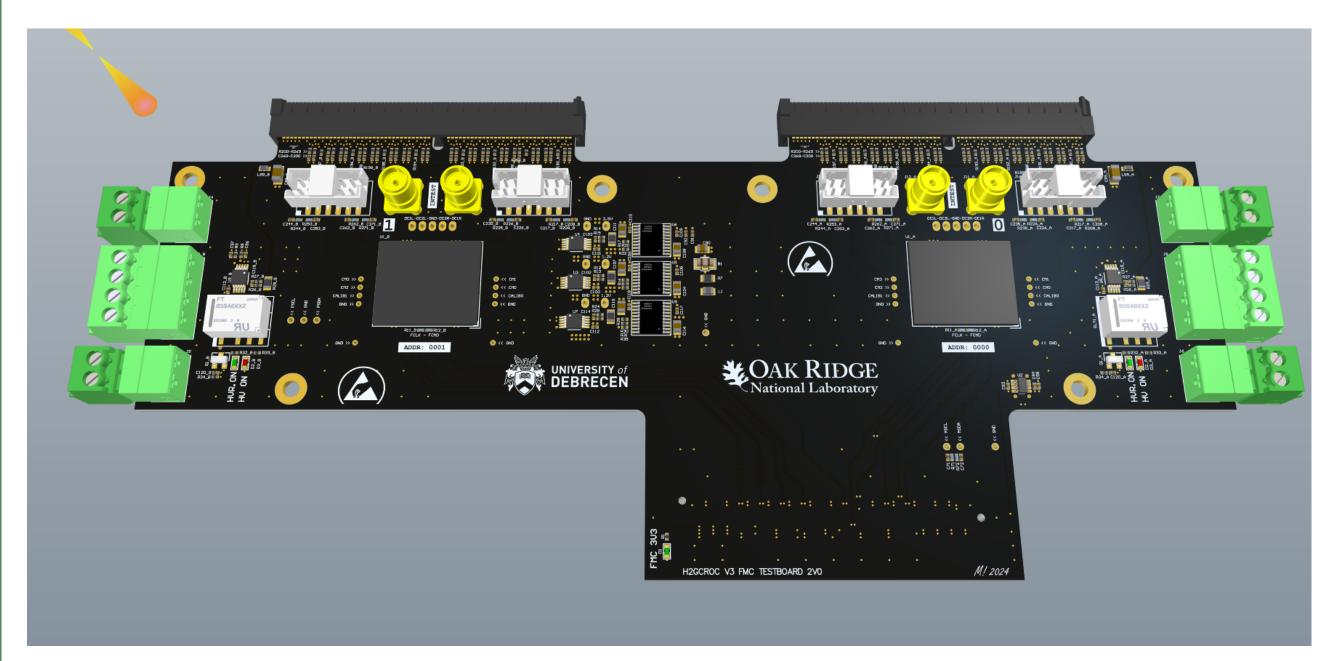

#### ProtoBoard2.0:

- Design is ready

- Sent to production, finished time end-of-March:

- Price is ~1000\$, working on quotes

- eRD109 money is coming in April, the manufacturer trusted us that we will pay for it

#### Modification list:

- Simplified communication with the KCU board (cheaper components)

- Extra connector for the 8 channels (72/hgcroc/-64/ caen connector/ = 8)

- Two LED pulser with SMA connectors

- Monitoring of low/bias voltages

Should be compatible with Tonko's effort on RDO

## SiPM signal summing

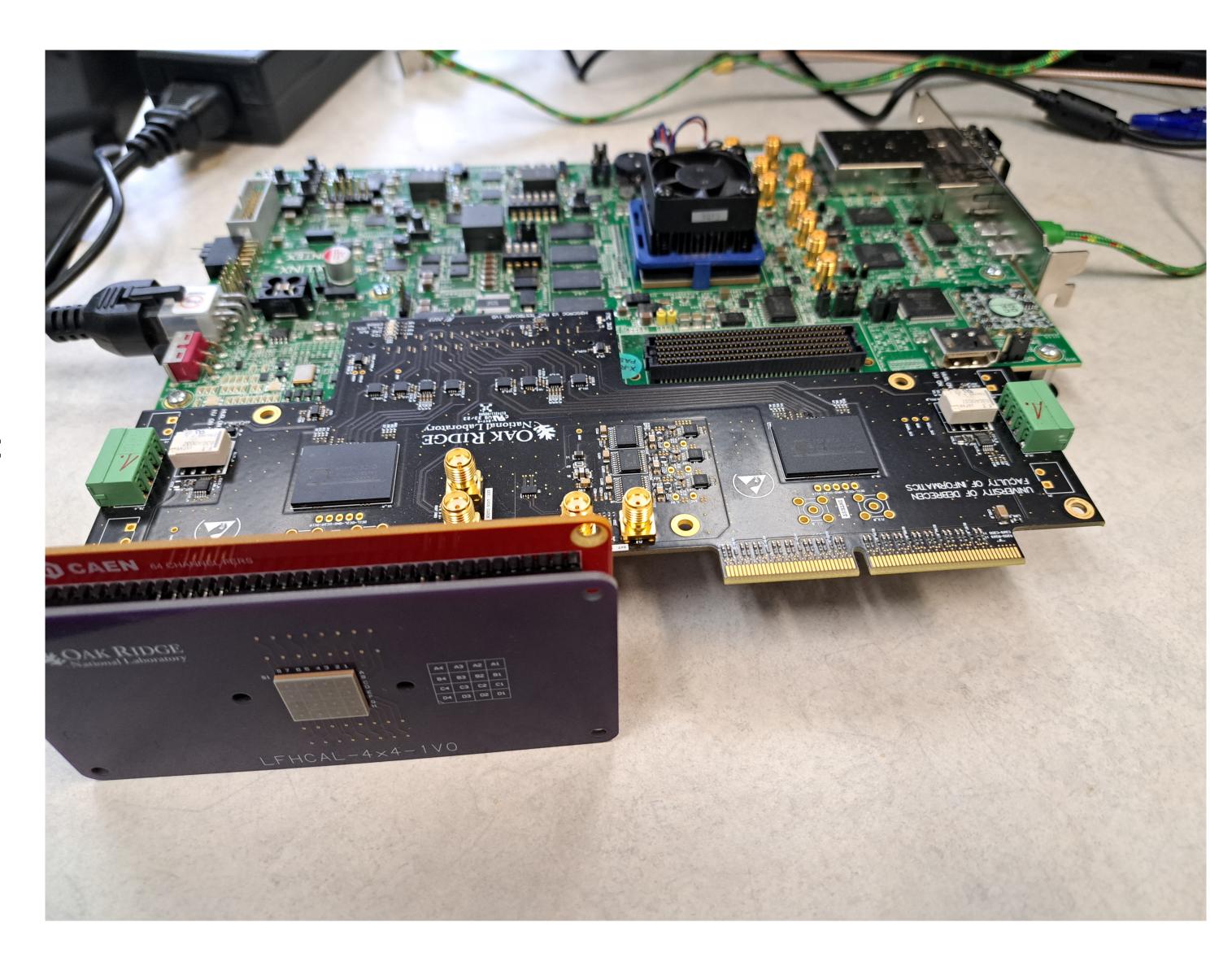

#### Received the 4x4 array from Argonne:

- 3x3 mm2 SiPM's, 16 in total

- Modular design to approach the summing systematically:

- Compatible the CAEN unit (red board)

- Purple one is only the SiPM array

- Extra summing board we will add in-between:

- Try different methods of summing from serial connector to more complicated designs

- Easily interchangeable:

- We can readout 16 channels (as on picture)

- We can add 2, 2x2, 3x3, 4x4 SiPM's gradually

Also important for LFHCal prototype

## HCal progress

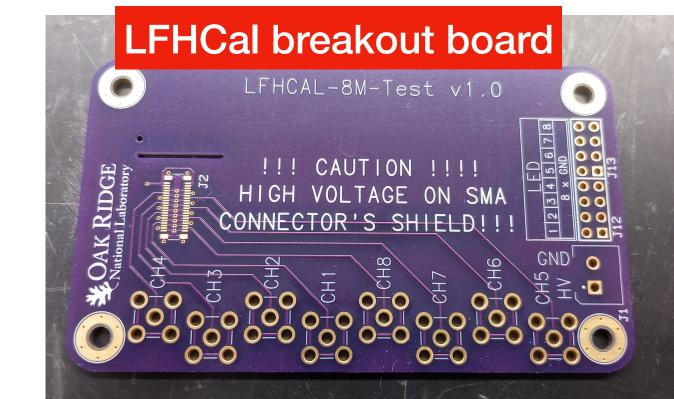

#### LFHCal:

- Testbeam planned in CERN May 15-22:

- One full 8M module (65 layers, 2x4 array)

- 520 individual channels for readout

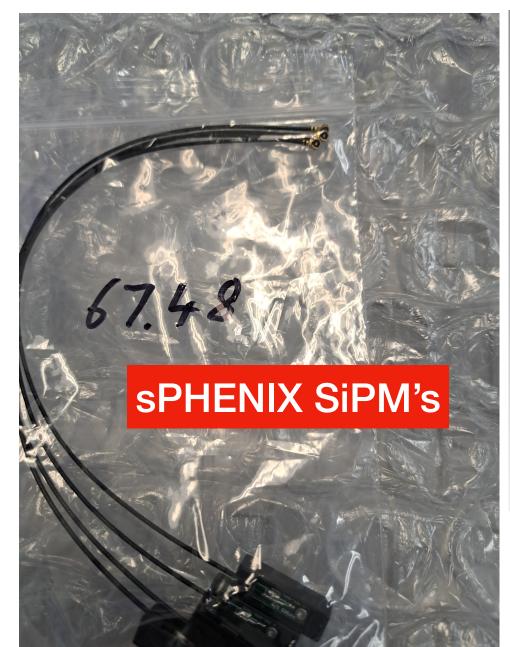

#### **Barrel HCal:**

**Backward HCal:**

expected

Very similar path as the

LFHCal, no summing is

- Received 4 sPHENIX SiPM boards, couple more components which can be made to SiPM boards also

- We also have some tiles from sPHENIX to test on

- Breakout board is already designed and sent to production

#

Breakout board for HGCROC

## Summary

Work ongoing with focus on the CERN PS test beam with LFHCal

Preparing the summing scheme with the Barrel

ECal SiPM array - first step is done

Progress in designing the FEB for LFHCal and BarrelECal, BarrelHCal

Also close communication with the Omega team about the CALOROC design and schedule

ORNL is managed by UT-Battelle LLC for the US Department of Energy

### Barrel TOF Flex PCB

- Connect 64 ASICs (+X) along stave to RDO at end of stave

- Low voltage, bias (HV), ground

- Differential e-links, clocks, slowcontrol/I<sup>2</sup>C?

- Individual ASIC output data rate is only ~Mbit/s (based on Tonko's initial estimates)

- Low mass: 1% X/X<sub>0</sub> total barrel material budget

- Needs to fit barrel TOF geometry

- ~1.3m length

- Kapton flex PCB:

- Custom geometry "sandwich" of thin kapton and conductor layers

- Used in other tracking detectors already

## Towards a TOF Barrel Flex Prototype for the TDR

- TDR should be 70-90% design maturity.

- We won't have a 70-90% mature ASIC.

- The ASIC (largely) defines the actual requirements of the flex: number of conductors, e-link speed, power requirements...

- All we can really do is demonstrate we master the technology to 70-90% design maturity

- Reading out a similar ASIC over a "long" flex with a prototype TOF RDO would be reasonable

- Plan made in Argonne: will demonstrate readout of ETROC (CMS endcap TOF ASIC) over "long" flex with TOF prototype RDO board

## Update

- Found capable engineering support at Debrecen

- In the meantime: produced flex PCBs test boards with different vendors

- Evaluated LV, HV characteristics

- LFHCAL flex boards in production in three different processes, including super thin state of the art layup, will evaluate yield and impedance

- Looking into low profile high density e-link connectors

- Unsolved: high density connector that includes HV bias capability... Likely requires second connector or even separate distribution