## **OB FPC prototyping**

**WP3 Electrical interfaces**

### **Outline**

- Recap of design on low TRL prototyping for OB:

- Based on a snapshot of project from Feb. 2024;

- Stave layout;

- Circuit definition;

- Signal ratings;

- Manufacturing technology;

- Module layout;

Of the evolutionary development

# Stave layout

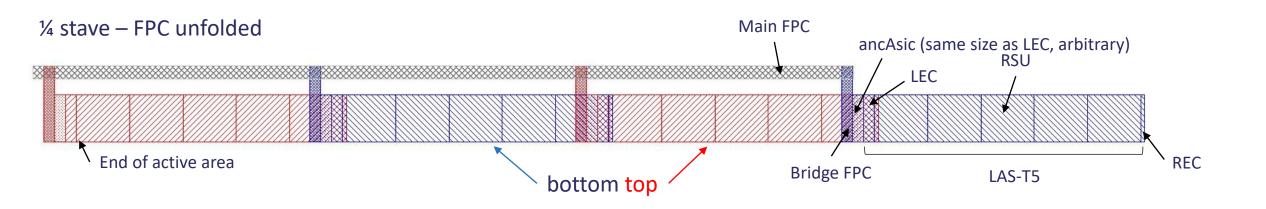

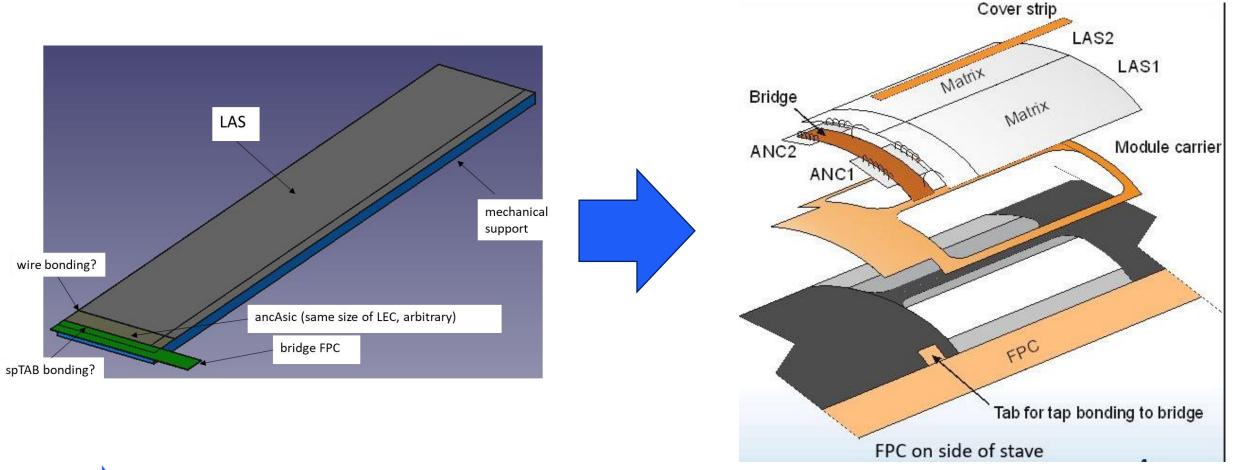

### Modules/LAS on stave & FPCs

Bridge FPC: connects ancASICs to Common Bus FPC; Size: W: ~5mm; L: ~340mm;

Main FPC: connects FPC bridges to end of stave; Size: W: ~5mm; L: ~30mm;

## Circuit definition

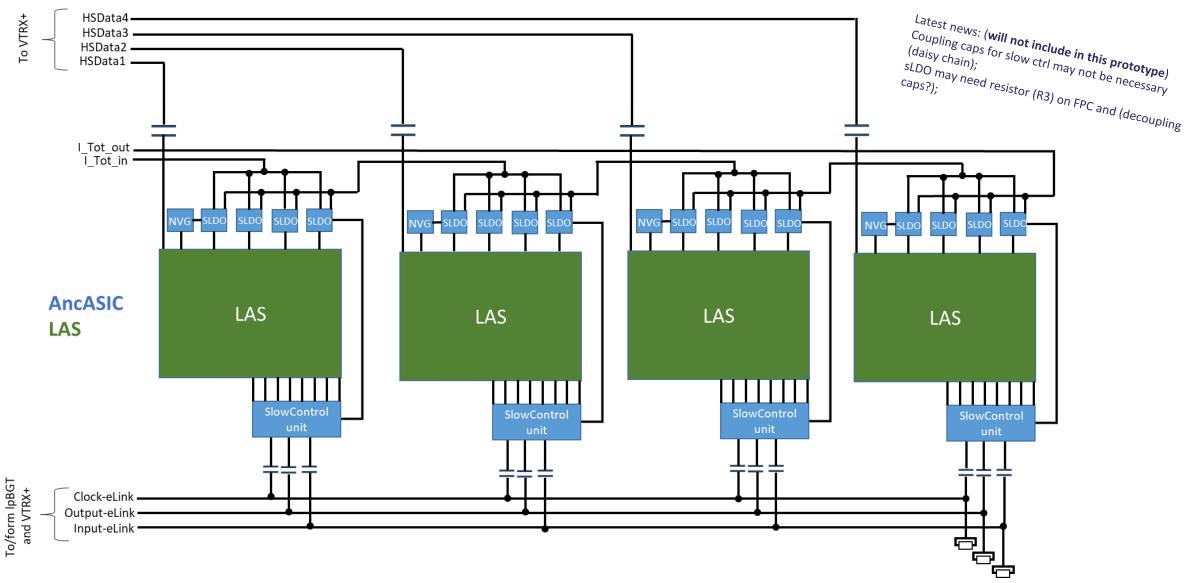

FPC connects the AncASIC to the DAQ system and pwr supplies.

Presenting a sequence of 4 sensors. [longest sequence in Epic Svt]

# Signal ratings

| Signal name            | Туре | Comment                                     | Coupling   | Standard                          | lpGBT eLink  | Rate                  |

|------------------------|------|---------------------------------------------|------------|-----------------------------------|--------------|-----------------------|

| slow ctrl clk (down)   | AC   | from IpGBT to AncASIC                       | Capacitive | CERN Low Powering Signal (CLPS)   | clock-eLink  | 80 Mb/s               |

| slow ctrl write (down) | AC   | from IpGBT to AncASIC                       | Capacitive | CERN Low Powering Signal (CLPS)   | output-eLink | 80 Mb/s               |

| slow ctrl read (up)    | AC   | from AncAsic to IpGBT                       | Capacitive | CERN Low Powering Signal (CLPS)   | input-eLink  | 160 Mb/s              |

| data                   | AC   | from AncAsic to VTRX+ (1 diff line/AncASIC) | Capacitive | CERN Low Powering Signal (CLPS)   | N/A          | 5.12 Gb/s (or 10Gb/s) |

| voltage supply         | DC   | Max: (2.5V/AncASIC) * (4 AncASIC)           | Direct     | 10% Vdrop for 2.5V/LAS, is it OK? | N/A          | N/A                   |

| current                | DC   | 2.5 A (total per AnASIC)                    | Direct     |                                   | N/A          | N/A                   |

To check: Is voltage supply still 2.5V ? (1.8V?)

To check: Is current supply still 2.5A? (worst case)

## Manufacturing technology

**Supplier RPE LTU**

### Updated preliminary design: unfolded assembled FPC

Composition of the assembled FPC:

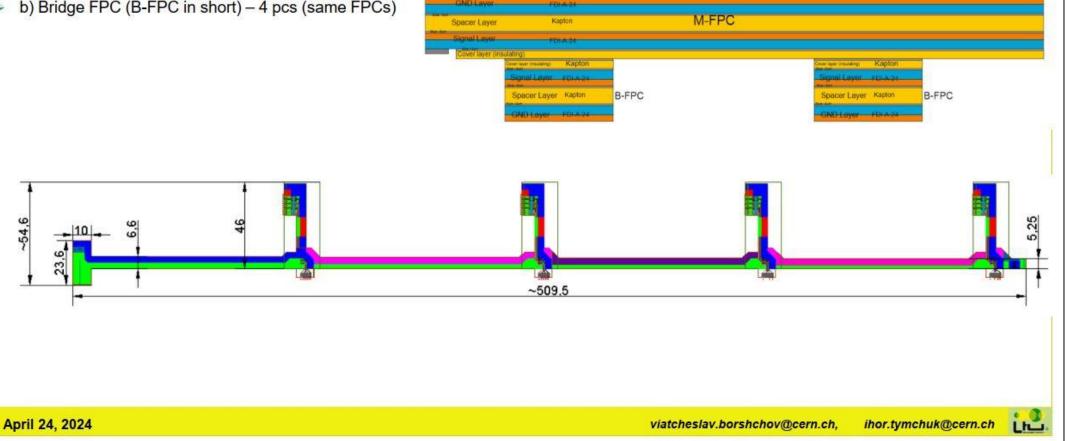

- a) Main FPC (M-FPC in short) 1pc

- b) Bridge FPC (B-FPC in short) 4 pcs (same FPCs)

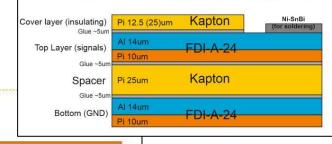

#### Schematic cross-section

Base cross-section of M-FPC and B-FPCs

# Module (a.k.a. HIC)

### Module based approach to OB stave

# 1<sup>st</sup> low TRL prototype

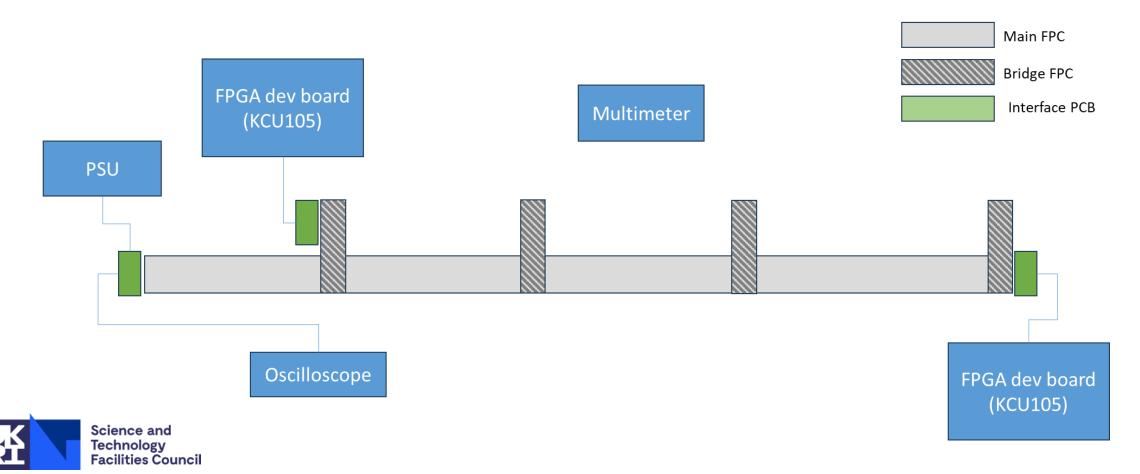

## Test set-up

Sketch of test set-up

### Conclusion

The definition stage of a Low TRL prototype (OB L4 stave) was based on a snapshot of the project from ~Feb.2024;

Design stage approaching completion, to be reviewed next week;

Next: procurement and testing (w Oxford and LANL);

## Thank you

**Facebook:** Science and Technology Facilities Council

Twitter: @STFC\_matters

YouTube: Science and

Technology Facilities Council