## ePIC SVT WP3 Electrical Interfaces Meeting

July 11, 2024

# Experience and capabilities of LTU team in direction of creating sensitive layers based on thin bent MAPS chips

### **RPE LTU:**

Vyacheslav (Slava) Borshchov Ihor Tymchuk <u>(responsible, speaker)</u> Maksym Protsenko

- Brief introduction

- Considered initial data

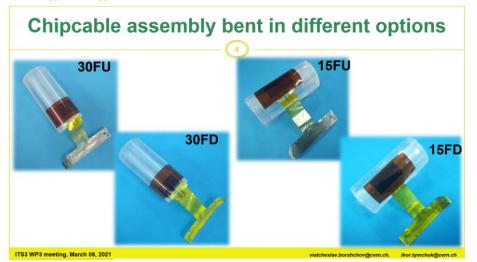

- Features of approach proposed for ALICE ITS3

- ITS3 SpTAB prototypes based on ALPIDE MAPS chips

- Some test results for bent MAPS chips obtained by LTU team

- Conclusions

## **Brief introduction**

- LTU team performed some activities directed on development of interconnection approach to thin bent MAPS chips for ALICE ITS3 project (main part of following slides were reported by LTU team within ALICE ITS3 WP3 and/or WP4 meetings)

- Proposed interconnection approach is based on using ultralight adhesiveless aluminium-polyimide dielectrics and SpTAB interconnection technique

- Activities have been performed in 2020-2021 but, unfortunately, were postponed because of the russian invasion in Ukraine. Now the activities are resuming.

- Activities have been performed in close cooperation with colleagues from CERN and from University of Bergen (leading by Prof. Dieter Röhrich)

# Initial data for developing and proposing approach by LTU within ALICE ITS3 project

### **Considered information**

Lol and Magnus' talks (ITS3 kick-of meeting 04.12.2019, ITS plenary 21.01.2020)

### **Base approach**

Base line for interconnection: ٠. wire bonding ۲ Interconnection

The chip to (flex) PCB interconnection needs to be studie

before/after bending potting?

Also the mechanical attachment of chip and flex need to be studied

January 31, 2020, CERN

Features/possible complications (our feeling)

- > Sensor need to be glued to FPC (or FPC-to-sensor) - possible complication at further bending

- > Wire bonding on bent sensor- special complicated jig agreed/tuned with/to wire bonder

- > Encapsulating of the wires for flat sensor- *possible* complication at further bending

- > Encapsulating of the wires for bent sensorcomplicated process (liquid glues)

> -...

viatcheslav.borshchov@cern.ch, ihor.tymchuk@cern.ch

### July 11, 2024

### ePIC SVT WP3 Electrical Interfaces Meeting

#### viatcheslav.borshchov@cern.ch,

# Some features of proposed approach by LTU team

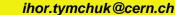

### Features of suggested approach

- For connecting sensor-to-FPC chipcable is using

- Connecting chipcable to sensor and to FPC is performing in flat (unbent) shape

- Bending of functional assembly (sensor + chipcable + FPC) is foreseen

- Chipcable is bonding to the sensor, then to FPC

- Interconnection technique: ultrasonic bonding ribbon leads of chipcable (to sensor and to FPC)

- Chipcable (single layered) and FPC (multilayered) are made of adhesiveless aluminium-polyimide dielectrics

- Protecting bond joints by dots of glue

- Functional electrical testing after each step

- Standard wedge wire bonding can be used (e.g. Delvotec)

#### January 31, 2020, CERN

viatcheslav.borshchov@cern.ch, ihor.tymchuk@cern.ch

### Key steps of assembly work flow

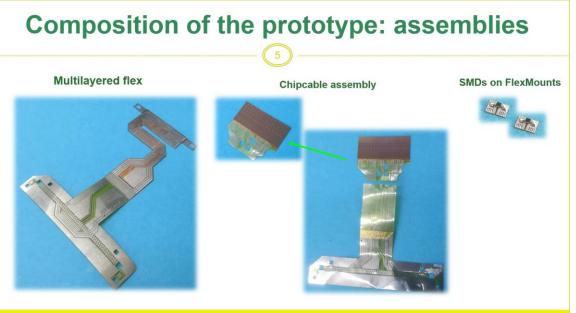

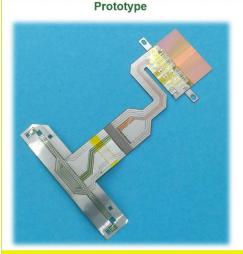

# ITS3 SpTAB prototypes developed and created by LTU team

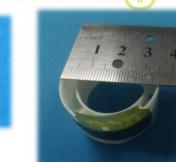

## Mechanical mock-up of bent chip

- Bending radius is 18 mm (ITS3 layer 0)

- For the mock-up pCT/FoCal chipcable has been used (AI 14um thick)

- Assembly was bent/unbent few times damages of bonds were not observed (visual inspection)

January 31, 2020, CERN

viatcheslav.borshchov@cern.ch, ihor.tymchuk@cern.ch

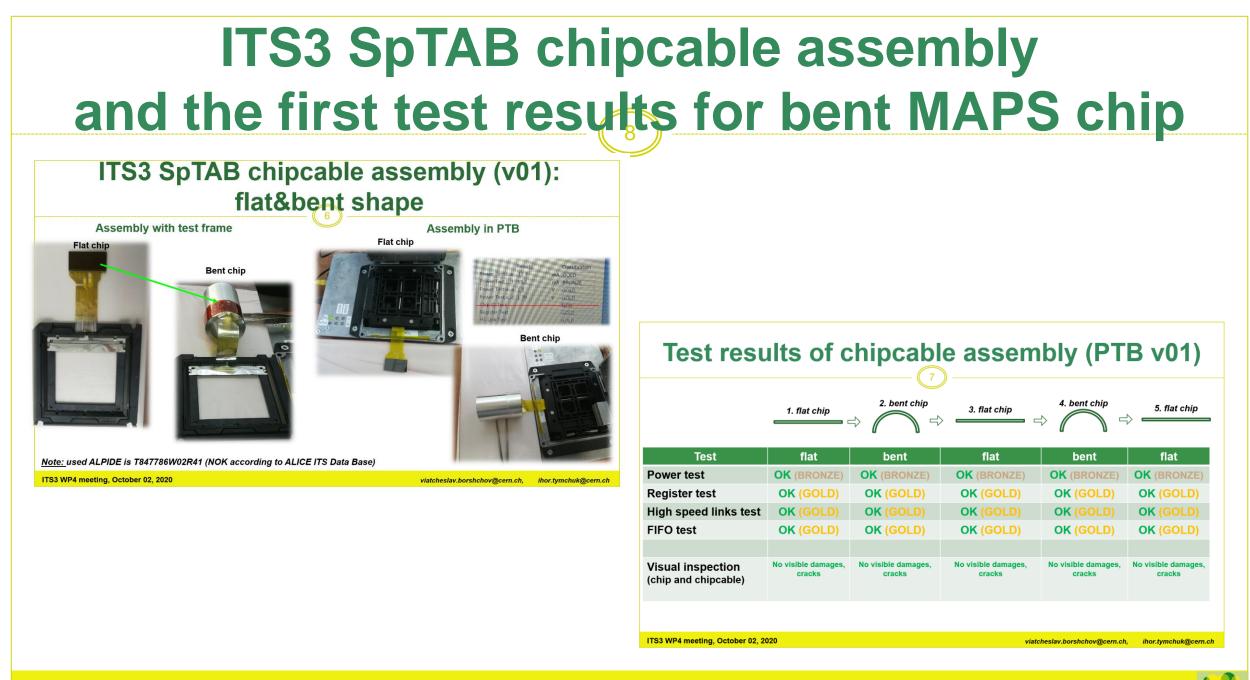

ITS3 WP4 meeting, October 02, 2020

viatcheslav.borshchov@cern.ch, ihor.tymchuk@cern.ch

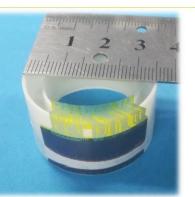

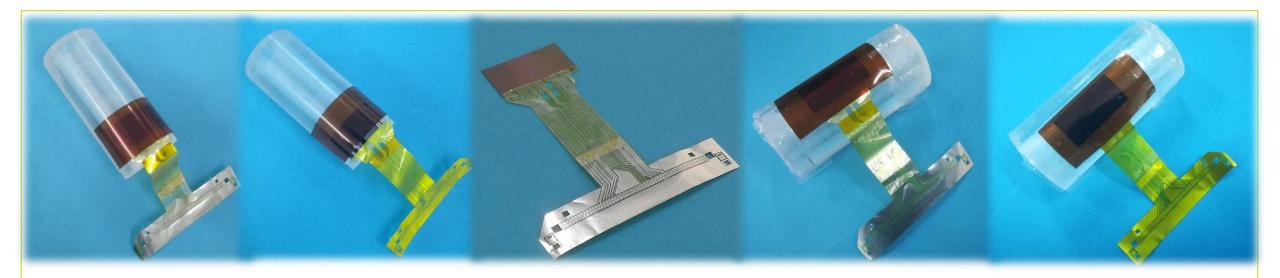

## **ITS3 SpTAB interconnection prototype**

## ITS3 SpTAB interconnection prototype (v01): flat shape

Prototype with test frame P

Prototype in PTB

ITS3 WP4 meeting, October 02, 2020

viatcheslav.borshchov@co

viatcheslav.borshchov@cern.ch, ihor.tymchuk@cern.ch

## ITS3 SpTAB interconnection prototype (v01): bent shape

Prototype (on metal core)

Prototype with test frame in PTB

ITS3 WP4 meeting, October 02, 2020

viatcheslav.borshchov@cern.ch, ihor.tymchuk@cern.ch

Important notes:

- PTBv01 hardware and software have been used for all tests of ALPIDE chips

- PTBv01 developed, created and kindly provided to LTU by UniBergen team (leading by Prof. Dieter Röhrich) within joint activities within pCT project/collaboration

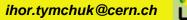

| Preliminary conclusion:                   | Notes | G - Gold   |            | Category        |                 |                |            |  |  |  |

|-------------------------------------------|-------|------------|------------|-----------------|-----------------|----------------|------------|--|--|--|

| Any significant differences have not been |       | S - Silver | Parameter  | gold            | silver          | bronze         | NOK        |  |  |  |

| observed for 10 bent/unbent steps         |       | B - Bronze | $I_A$ (mA) |                 | 10.42 to 15.54  |                |            |  |  |  |

| (without tests of pixel matrix)           |       |            | $I_D$ (mA) | 44.40 to 50.02  | 40.00 to 50.70  | 35.00 to 70.00 | otherwise  |  |  |  |

| ITS3 WP4 meeting, October 16, 2020        |       |            |            | viatcheslav.boi | rshchov@cern.ch | , ihor.tymchu  | ik@cern.ch |  |  |  |

ihor.tymchuk@cern.ch

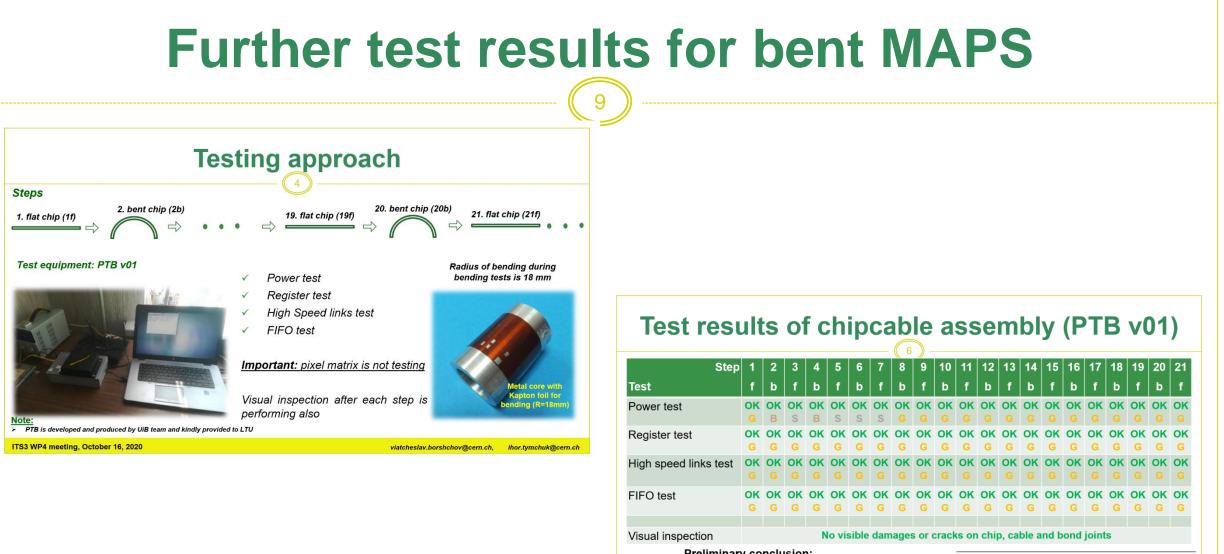

## ITS3 SpTAB chipcable assembly: improved and developed test approach

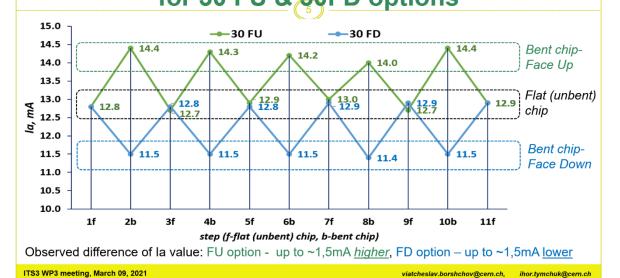

### Test results for 30 FU and 30 FD options

| Test f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b f b                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power test OK/S    |

| Register test OK/G |

| O HS links test OK/S    |

| FIFO test OK/G OK/G OK/G OK/G OK/G OK/G OK/G OK/G                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Visual inspection No visible damages or cracks on chip, cable and bond joints                                                                                                                                                                                                                                                                                                                                                                                                        |

| Power test OK/G OK/G OK/S OK/G OK/S OK/G OK/G OK/G OK/G OK/G OK/G                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Register test OK/G |

| HS links test OK/G OK/G OK/G OK/G OK/G OK/G OK/G OK/G                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FIFO test OK/G OK/G OK/G OK/G OK/G OK/G OK/G OK/G                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Visual inspection No visible damages or cracks on chip, cable and bond joints                                                                                                                                                                                                                                                                                                                                                                                                        |

| G – Gold, S – Silver, B - Bronze                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| significant differences have not been observed for 11 bent/unbent steps<br>for FU and FD test options (without analog scan of pixel matrix)                                                                                                                                                                                                                                                                                                                                          |

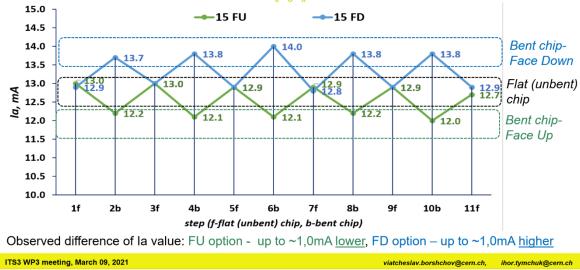

### Test results for 15 FU and 15 FD options

| Option        | Step                               | 1    | 2     | 3       | 4     | 5       | 6       | 7       | 8        | 9         | 10        | 11       | 15 FU test option |

|---------------|------------------------------------|------|-------|---------|-------|---------|---------|---------|----------|-----------|-----------|----------|-------------------|

|               | Test                               | f    | b     | f       | b     | f       | b       | f       | b        | f         | b         | f        | ion o iciscopilon |

| 1             | Power test                         | OK/G | OK/G  | OK/G    | OK/G  | OK/G    | OK/G    | OK/G    | OK/G     | OK/G      | OK/G      | OK/G     | ·                 |

| E             | Register test                      | OK/G | OK/G  | OK/G    | OK/G  | OK/G    | OK/G    | OK/G    | OK/G     | OK/G      | OK/G      | OK/G     |                   |

|               | HS links test                      | OK/G | OK/G  | OK/G    | OK/G  | OK/G    | OK/G    | OK/G    | OK/G     | OK/G      | OK/G      | OK/G     |                   |

| 15            | FIFO test                          | OK/G | OK/G  | OK/G    | OK/G  | OK/G    | OK/G    | OK/G    | OK/G     | OK/G      | OK/G      | OK/G     |                   |

| -             | Visual inspection                  |      | No vi | sible d | amage | s or cr | acks on | chip, d | cable an | d bond je | oints     |          | 000               |

|               | Power test                         | OK/G | OK/G  | OK/G    | OK/S  | OK/G    | OK/G    | OK/G    | OK/G     | OK/G      | OK/G      | OK/G     | 15 FD test option |

| E             | Register test                      | OK/G | OK/G  | OK/G    | OK/G  | OK/G    | OK/G    | OK/G    | OK/G     | OK/G      | OK/G      | OK/G     |                   |

|               | HS links test                      | OK/G | OK/G  | OK/G    | OK/G  | OK/G    | OK/G    | OK/G    | OK/G     | OK/G      | OK/G      | OK/G     |                   |

| 15            | FIFO test                          | OK/G | OK/G  | OK/C    | OK/G  | OK/G    | OK/G    | OK/G    | OK/G     | OK/G      | OK/G      | OK/G     |                   |

|               | Visual inspection                  |      | No vi | sible d | amage | s or cr | acks on | chip, d | cable an | d bond je | oints     |          | P D               |

| onclusi       | on:                                |      |       |         |       |         |         |         | G -      | Gold, S - | Silver, B | - Bronze |                   |

| Sala and Sala | nificant differen<br>for FU and FD |      |       |         |       |         |         |         |          |           | eps       |          | 1 Litte           |

ePIC SVT WP3 Electrical Interfaces Meeting

# Obtained test results for Id and Ia for ITS3 SpTAB chipcable assembly

### Difference in la for flat/bent ALPIDE for 30 FU & 30FD options

Difference in la for flat/bent ALPIDE for 15 FU & 15FD options

## Conclusions

- LTU team has successful experience in activities relating interconnecting thin bent MAPS chips within ALICE ITS3 project (in close cooperation with CERN and University of Bergen teams)

- Available experience, approaches and capabilities of LTU team might be developed and implemented in further activities relating bent MAPS chips for ePIC SVT project

# Thanks a lot for your attention!

With the best wishes from Ukraine!