# eRD109 update - H2GCROC

Norbert Novitzky With Miklos Czeller, Gabor Nagy (ORNL)

ORNL is managed by UT-Battelle LLC for the US Department of Energy

## Hardware and Firmware are ready

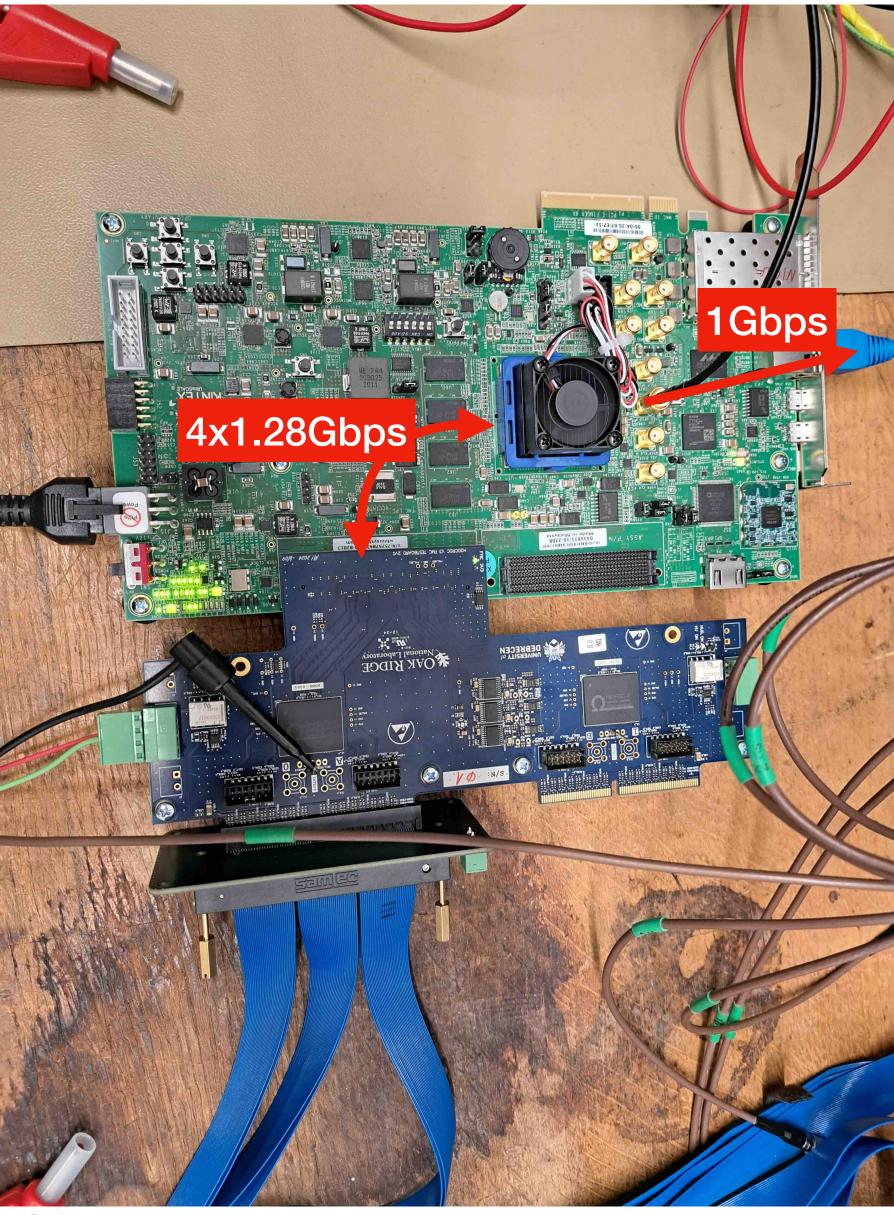

- FPGA and H2GCROC3s:

- UpStream:

#### **Communication with the H2GCROC3:**

- DownStream:

- 2xI2C lines for setup

- 2xFCMD lines

- 2x320MHz clock

- 2x2x1.28Gbps data lines

- 1 sample takes 80x32 bit word + idle

- About 1.025 µs readout

- 2x4x1.28Gbps trigger lines (option to not include in more upstream) • KCU105 and PC:

- 1 Gbps UDP readout

- Creating a bottle neck

- Factor of 5 less speed

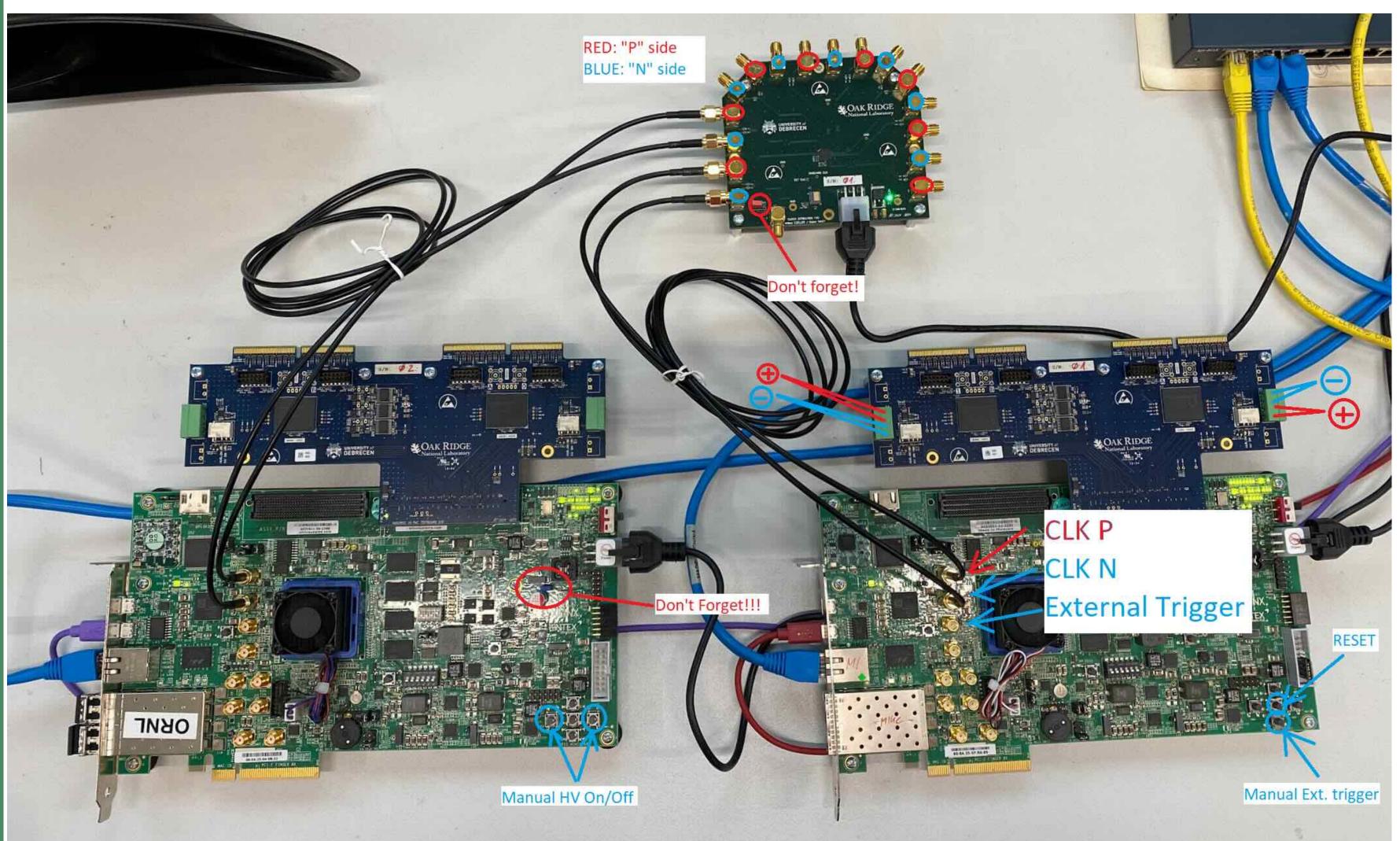

### External Clock – to synchronize the data

#### Simple external clock is board is used for synchronization:

- The oscillator provides 40 MHz LVDS clock via the SMA connector in KCU105

- Cable length is the same 1 meter sufficient for our tests

- External trigger is coming in 1.8V input

### Data format

| a0 00 24 00                  | 05 05 28 5          | 1 50 ac 06 85 00 00 44 00 04 a                                                   | a0 00 00 07 a0 00 00 06 f0    | 00 00 06 f0 00 00 06 50 00 00 09 40 00 00                                              |

|------------------------------|---------------------|----------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------|

|                              |                     |                                                                                  |                               | 00 00 05 d0 00 00 06 f0 00 00 07 50 00 00                                              |

|                              |                     |                                                                                  |                               | 00 00 06 60 00 00 09 00 00 00 07 90 00 00                                              |

| a0 00 24 03                  | 05 05 28 5          | 1 09 00 00 00 08 20 00 00 06 1                                                   | f0 00 00 07 50 00 00 0a 00 (  | 00 00 08 20 00 00 08 40 00 00 07 f0 00 00                                              |

| a0 00 24 04                  | <b>05 05 28 5</b> 3 | 1 07 70 00 00 05 b0 00 00 04 c                                                   | d0 00 00 08 10 00 00 07 70 0  | 00 00 04 80 00 00 06 f0 00 00 cf 98 73 60                                              |

|                              |                     |                                                                                  |                               | 00 00 04 40 00 00 05 f0 00 00 06 f0 00 00                                              |

|                              | 05 05 28 5          |                                                                                  |                               | 00 00 06 f0 00 00 05 b0 00 00 06 f0 00 00                                              |

| a1 00 25 0                   |                     | 5 50 00 00 06 d0 00 00 06 c                                                      | d0 00 00 07 70 00 00 06 50 (  | 00 00 06 f0 00 00 06 d0 00 00 06 50 00 00                                              |

| a1 00 25 0                   |                     | 5 a0 00 00 06 b0 00 00 08 0                                                      | 00 00 00 05 70 00 00 05 00 0  | 00 00 06 80 00 00 06 80 00 00 05 e0 00 00                                              |

|                              |                     |                                                                                  |                               | 00 00 06 b0 00 00 05 70 00 00 d5 a9 78 e8                                              |

|                              |                     |                                                                                  |                               | 00 00 02 e0 00 00 02 a0 00 00 02 e0 00 00                                              |

| a0 00 25 01                  |                     |                                                                                  |                               | 00 00 03 60 00 00 04 20 00 00 04 90 00 00<br>00 00 05 50 00 00 04 20 00 00 04 50 00 00 |

| ASIC EPGA                    |                     |                                                                                  |                               | 00 00 05 a0 00 00 04 80 00 00 04 b0 00 00<br>00 00 06 e0 00 00 05 50 00 00 05 b0 00 00 |

|                              |                     |                                                                                  |                               | 00 00 02 a0 00 00 04 40 00 00 5d d2 9a 01                                              |

|                              |                     | ר כט טט טט טט 4 00 00 00 00 00 00 00 1<br>1 כע טט טט טט טט כס כט <i>א</i> ט מע מ |                               |                                                                                        |

|                              |                     |                                                                                  |                               | 00 00 05 70 00 00 06 e0 00 00 03 a0 00 00<br>00 00 05 70 00 00 06 e0 00 00 03 a0 00 00 |

|                              |                     |                                                                                  |                               | 00 00 05 70 00 00 05 40 00 00 05 00 00 00                                              |

|                              |                     |                                                                                  |                               | 00 00 05 f0 00 00 05 00 00 00 02 50 00 00                                              |

|                              |                     |                                                                                  |                               | 00 00 03 e0 00 00 05 70 00 00 cc d1 3e 39                                              |

|                              |                     |                                                                                  |                               | 00 00 06 f0 00 00 06 80 00 09 00 00 00                                                 |

|                              |                     |                                                                                  |                               | 00 00 05 f0 00 00 06 f0 00 00 07 60 00 00                                              |

| a0 00 24 02                  | 05 05 28 7          | a 06 50 00 00 05 f0 00 00 05 0                                                   | 00 00 00 06 80 00 00 08 40 (  | 00 00 06 50 00 00 09 00 00 00 07 70 00 00                                              |

| a0 00 24 03                  | 05 05 28 7a         | a 09 00 00 00 08 10 00 00 06 1                                                   | f0 00 00 07 50 00 00 0a 00 (  | 00 00 07 f0 00 00 08 50 00 00 08 20 00 00                                              |

|                              |                     |                                                                                  |                               | 00 00 04 80 00 00 06 f0 00 00 a6 72 6e 98                                              |

|                              |                     |                                                                                  |                               | 00 00 04 50 00 00 05 f0 00 00 06 f0 00 00                                              |

|                              |                     |                                                                                  |                               | 00 00 07 20 00 00 05 a0 00 00 06 f0 00 00                                              |

|                              |                     |                                                                                  |                               | 00 00 06 f0 00 00 06 b0 00 00 06 50 00 00                                              |

|                              |                     |                                                                                  |                               | 00 00 06 80 00 00 06 80 00 00 05 d0 00 00                                              |

|                              |                     |                                                                                  |                               | 00 00 06 b0 00 00 05 50 00 00 5e 8a db 54                                              |

|                              |                     |                                                                                  |                               | 00 00 02 e0 00 00 02 a0 00 00 02 d0 00 00<br>00 00 02 E0 00 00 04 20 00 00 04 E0 00 00 |

|                              |                     |                                                                                  |                               | 00 00 03 50 00 00 04 20 00 00 04 50 00 00<br>00 00 05 a0 00 00 04 b0 00 00 05 00 00 00 |

|                              |                     |                                                                                  |                               | 00 00 05 a0 00 00 04 b0 00 05 00 00 00 00<br>00 00 06 d0 00 00 05 70 00 00 05 a0 00 00 |

|                              |                     |                                                                                  |                               | 00 00 02 a0 00 00 04 50 00 00 34 16 8f c2                                              |

|                              | 05 05 28 7          |                                                                                  | au uu uu uu 4u uu uu uu uu uu | 00 00 02 00 00 00 04 30 00 00 34 10 01 C2                                              |

| OAK RIL (a1 00 24 01         | 05 05 28 7          | a 04 10 00 00 03 a0 00 00 00 05 0                                                | 90 00 00 03 00 00 00 03 30 0  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                   |

| <b>CINATIONAL LADOI</b> HOPV |                     |                                                                                  |                               |                                                                                        |

#### H2GCROC data

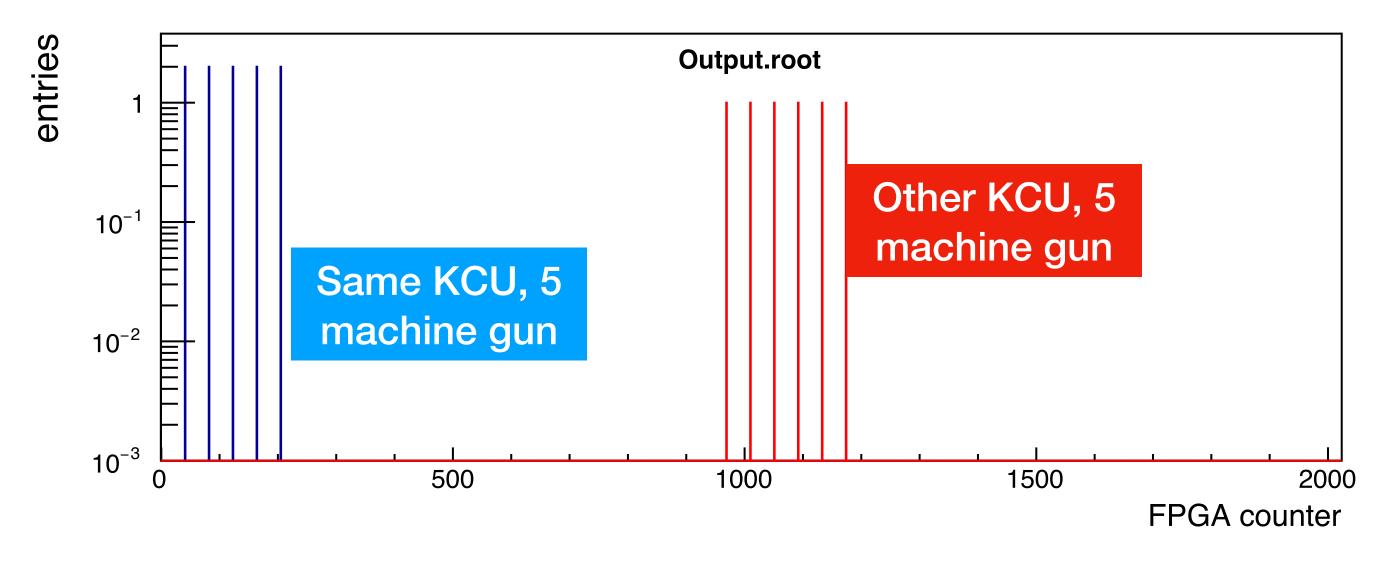

## Synchronization process offline

#### **Procedure for analysis:**

- Collect 20 lines of KCU information:

- Has to have the same FPGA time stamp

- Contains all readout for 2 ASICs, both sides

- Create root file

- Create events using full KCU information:

- Take one FPGA counter reference

- Compare the difference to it with the same FPGA ID:

- This will collect the same machine guns

- Compare the difference to it with a different FPGA ID:

- This will collect the other KCU information

- There is an expected offset:

- This offset changes run-by-run, but very stable

- Tag all the used FPGA counters

#### 1 event example

## Software development

| 0                                              |                    |                  |                                |                                |                                |                                |                                |                                | Current Config -                            |

|------------------------------------------------|--------------------|------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|---------------------------------------------|

| D ASIC 1                                       |                    |                  |                                |                                |                                |                                |                                |                                | FPGA selection: FPGA 0                      |

|                                                |                    |                  |                                |                                |                                |                                |                                |                                | ASIC selection: ASIC 0                      |

| Top Register                                   | <u> </u>           |                  |                                | Register                       | : Channel_54                   |                                |                                |                                | Register Selection                          |

| Тор                                            | Bit 7              | Bit 6            | Bit 5                          | Bit 4                          | Bit 3                          | Bit 2                          | Bit 1                          | Bit 0                          | Use half-wise regi                          |

| Global Analog Register:<br>Global Analog 1     | Byte Gain_conv< 1> | Gain_conv<<br>0> | Inputdac<5>                    | Inputdac<4>                    | Inputdac<3>                    | Inputdac<2>                    | Inputdac<1>                    | Inputdac<0>                    | ✓ Use channel-wise regi<br>Config File Info |

| Global Analog 0                                | 0 0                | 0                | Θ                              | 0                              | 0                              | 0                              | Θ                              | Θ                              | /home/epical/PythonCode                     |

| Reference Voltage Regi                         | Byte trim_toa<5>   | trim_toa<4>      | trim_toa<3>                    | trim_toa<2>                    | trim_toa<1>                    | trim_toa<0>                    | sel_trig_t<br>oa               | mask_toa                       | NewGit/H2GConfig/config,<br>f0a0.json       |

| Reference_Voltage_1                            | 1 0                | 0                | 0                              | 0                              | 0                              | 0                              | 0                              | 0                              | Synced to File                              |

| Reference_Voltage_0                            | Byte trim_tot<5>   | trim tot<4>      | trim tot<3>                    | trim tot<2>                    | trim tot<1>                    | trim tot<0>                    | NA                             | NA                             | Load Save Sa                                |

| Master TDC Registers - Master TDC 1            | 2 0                | 0                | 0                              | 0                              | 0                              | 0                              | 0                              | 0                              |                                             |

| Master TDC 0                                   | Byte trim_inv<5>   | trim_inv<4>      | trim_inv<3>                    | trim_inv<2>                    | trim_inv<1>                    | trim_inv<0>                    | probe_noinv                    | probe_inv                      |                                             |

| Digital Half Registers                         |                    |                  | 0                              |                                |                                | 0                              |                                |                                |                                             |

| Digital Half 1                                 | 3 0                | 0                | 0                              | 0                              | 0                              | 0                              | 0                              | 0                              |                                             |

| Digital_Half_0                                 | Byte probe_toa     | probe_tot        | mask_tot                       | sel_trig_t<br>ot               | Channel_off                    | HighRange                      | LowRange                       | probe_pa                       |                                             |

| Channel Wise Registers                         | 4 0                | 0                | 0                              | 0                              | 0                              | 0                              | 1                              | Θ                              |                                             |

| CM_2 CM_3<br>Channel_36 Channel_37             | Byte mask_adc      | NA               | DAC_CAL_CT<br>DC_TOT<5>        | DAC_CAL_CT<br>DC_TOT<4>        | DAC_CAL_CT<br>DC_TOT<3>        | DAC_CAL_CT<br>DC_TOT<2>        | DAC_CAL_CT<br>DC_TOT<1>        | DAC_CAL_CT<br>DC_TOT<0>        |                                             |

| Channel_38 Channel_39                          | 5 0                | 0                | 0                              | 0                              | Θ                              | Θ                              | 0                              | 0                              |                                             |

| Channel_40 Channel_41<br>Channel 42 Channel 43 | Byte HZ_inv        | HZ_noinv         | DAC_CAL_CT<br>DC_TOA<5>        | DAC_CAL_CT<br>DC_TOA<4>        | DAC_CAL_CT<br>DC_TOA<3>        | DAC_CAL_CT<br>DC_TOA<2>        | DAC_CAL_CT<br>DC_TOA<1>        | DAC_CAL_CT<br>DC_TOA<0>        |                                             |

| Channel 44 Channel 45                          | 6 0                | 0                | 0                              | 0                              | 0                              | 0                              | Θ                              | 0                              |                                             |

| Channel_46 Channel_47                          | Byte NA            | NA               | DAC_CAL_FT<br>DC_TOT<5>        | DAC_CAL_FT<br>DC_TOT<4>        | DAC_CAL_FT<br>DC_TOT<3>        | DAC_CAL_FT<br>DC_TOT<2>        | DAC_CAL_FT<br>DC_TOT<1>        | DAC_CAL_FT<br>DC_TOT<0>        |                                             |

| Channel_48 Channel_49                          | 7 0                | 0                | 0                              | 0                              | 0                              | 0                              | 0                              | 0 -                            |                                             |

| Channel_50 Channel_51<br>Channel_52 Channel_53 | Byte NA            | NA               | DAC_CAL_FT<br>DC TOA<5>        | DAC_CAL_FT<br>DC TOA<4>        | DAC_CAL_FT<br>DC TOA<3>        | DAC_CAL_FT<br>DC TOA<2>        | DAC_CAL_FT<br>DC TOA<1>        | DAC_CAL_FT<br>DC TOA<0>        |                                             |

| Channel_54 Channel_55                          | 8 0                | 0                | 0                              | 0                              | 0                              | 0                              | 0                              | 0                              |                                             |

| Channel_56 Channel_57                          | 8 0                | 0                | -                              | -                              |                                | -                              | -                              | -                              | Link Info                                   |

| Channel_58 Channel_59<br>Channel 60 Channel 61 | Byte NA            | NA               | IN_FTDC_EN<br>CODER_TOA<<br>5> | IN_FTDC_EN<br>CODER_TOA<<br>4> | IN_FTDC_EN<br>CODER_TOA<<br>3> | IN_FTDC_EN<br>CODER_TOA<<br>2> | IN_FTDC_EN<br>CODER_TOA<<br>1> | IN_FTDC_EN<br>CODER_TOA<<br>0> | IP Address: 10.1.2.2<br>Port: 11000         |

| Channel 62 Channel 63                          | 9 0                | 0                | 0                              | 0                              | 0                              | 0                              | 0                              | 0                              | Ping FPGA                                   |

| Channel_64 Channel_65                          |                    | 0                | IN_FTDC_EN                     | IN_FTDC_EN                     | IN_FTDC_EN                     | IN_FTDC_EN                     | IN_FTDC_EN                     | IN_FTDC_EN                     | Send Current ASIC Con                       |

| Channel_66 Channel_67                          | Byte DIS_TDC       | NA               | CODER_TOT<                     | CODER_TOT<<br>4>               | CODER_TOT<<br>3>               | CODER_TOT<<br>2>               | CODER_TOT<                     | CODER_TOT<                     |                                             |

#### **DAQ** is very simple:

- File or terminal dump

- Generator settings all in 40MHz

- External trigger

- Ext. trigger delay needs to avoid the UDP packet loss

- Daq push 1 event

- HV on/off for the board

- Adjustment if there is a misalignment, debugging

#### **Slow Control for the H2GCROC:**

- N FPGA with 2 H2GCROC setup (1x2 in this case)

- All registers are settable and working

|      |     |                                 | H2GDAQ                     |                       |

|------|-----|---------------------------------|----------------------------|-----------------------|

|      | DAQ | Working Folder                  | Generator Debug            | DAQ + Generator START |

|      |     |                                 | Data Collection            | DAQ Push              |

|      |     | /home/epical/PythonCodes/       | Data Coll En[7:0] 3        | Start Generator       |

|      |     | NewGit/H2GDAQ                   | Trig Coll En[7:0]          | Stop Generator        |

|      |     | Select Folder Print to Terminal | Generator                  |                       |

|      |     |                                 | Gen PreImp En 🗸            | High Voltage Reset/Ad |

|      |     | DAQ Settings                    | Gen Pre Int 16 🌲           |                       |

|      |     | event 100 🌲                     | Gen Nr Cycles 1000         | ✓ F0 ✓ A0 ✓ A         |

|      |     |                                 | Gen Interval 100000        |                       |

|      |     | time [sec] 1                    | External Trigger           |                       |

|      |     | ✓ manual                        | Ext Trg En                 |                       |

|      |     |                                 | Ext Trg Delay 0            |                       |

|      |     |                                 | Ext Trg DeadT 255          |                       |

|      |     |                                 | Fast Command               |                       |

|      |     | Run Number 35 🏮                 | DAQ FCMD 75 🌲              |                       |

|      |     |                                 | DAQ Push FCMD 75 4         |                       |

|      |     | Data Count 8.46 MB              | Gen Pre FCMD 45 🌲          |                       |

|      |     | Set IODELAY                     |                            |                       |

|      |     |                                 | Gen FCMD 75 🜲              |                       |

|      |     | Start DAQ                       | Machine Gun 10 \$          |                       |

|      |     |                                 |                            |                       |

|      |     | Stop DAQ                        | Send Gen Config before DAQ |                       |

|      |     | Scop DAQ                        | Send Gen Config            | Send HV Settings      |

| - 18 |     |                                 |                            |                       |

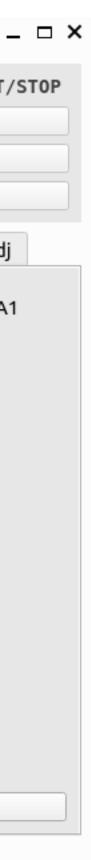

### Some very early results

combine them so far

Channel vs. ADC (Board 208)

## Summary

### Hardware:

• Done, 6 boards (1 France, 5 with me) Firmware:

• Done

### **Software:**

- Work in progress:

- I2C GUI interface done

- I2C terminal setup work-in-progress needed for fast calibration

- DAQ GUI interface done

- DAQ terminal setup work-in-progress again, calibration

### More to come:

- Production and testing of summing boards

- Testing of the Samtec cables (firmware ready)

- LED testing