#### **DAQ Demonstrator**

**Atanu Modak**

Particle Physics

#### **Motivation**

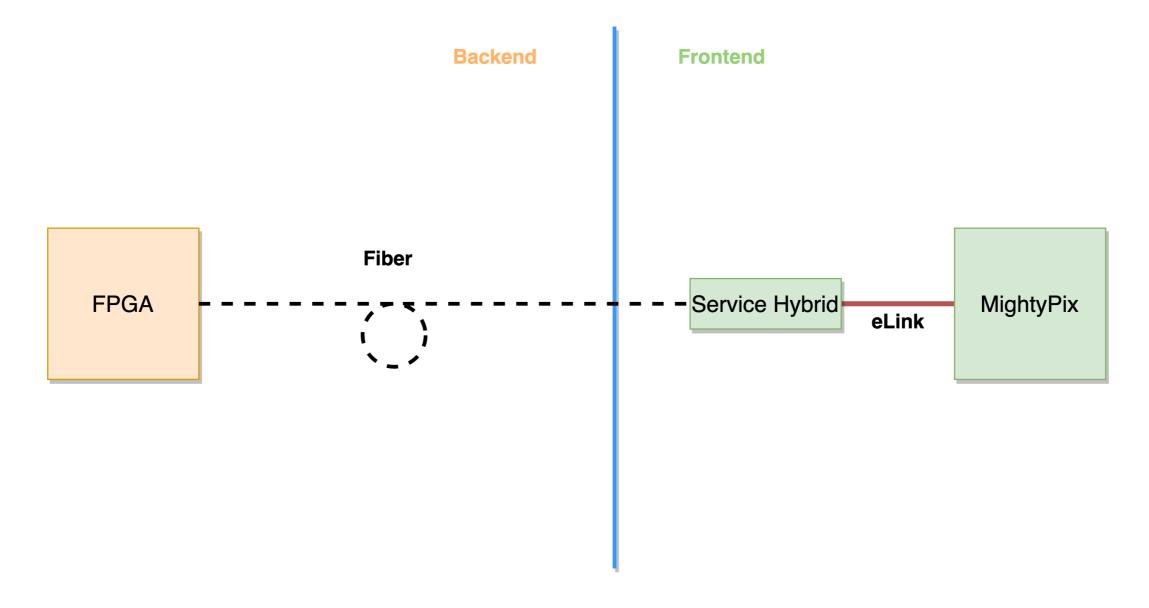

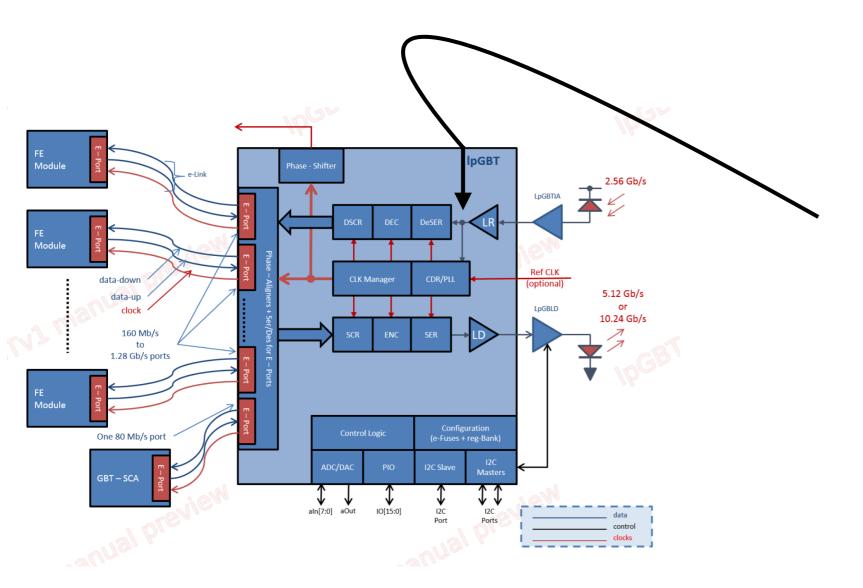

Demonstrate a full DAQ chain with final system like components for LHCb tracker upgrade in LS4 (2033-34)

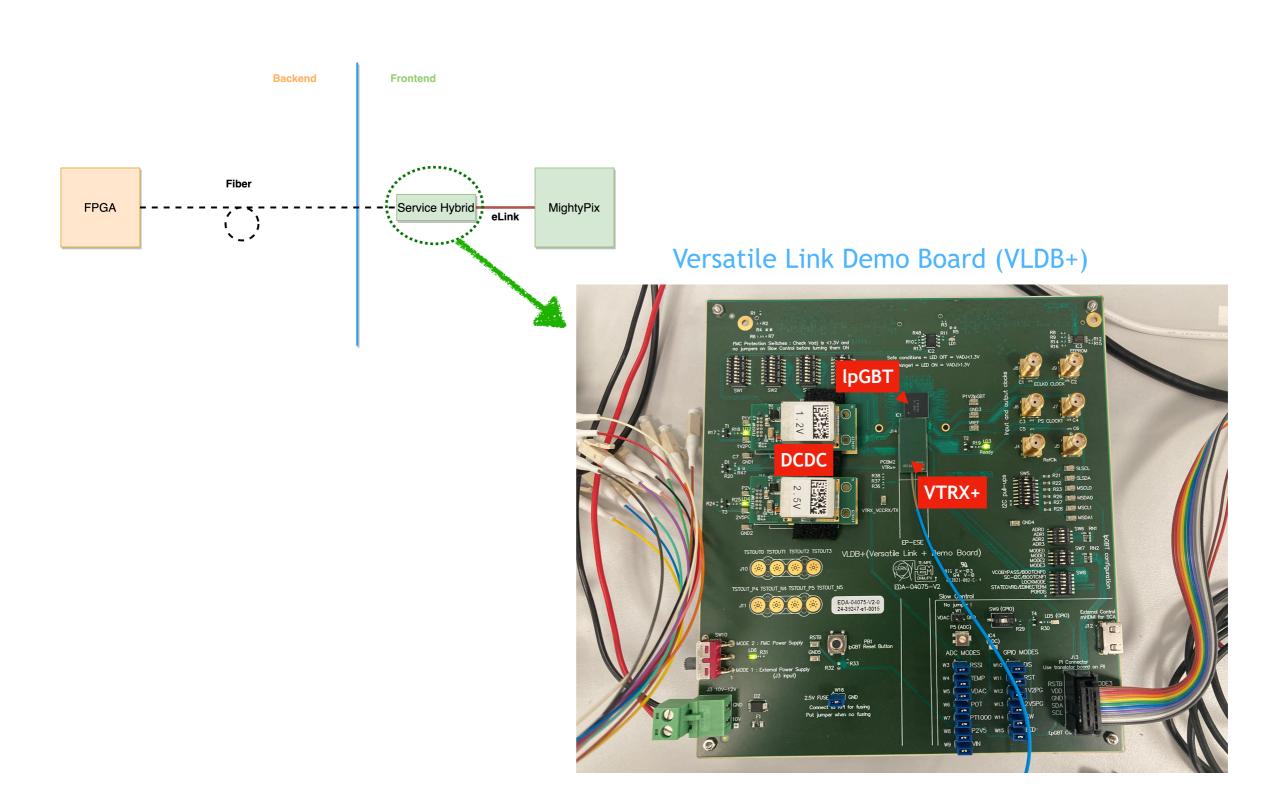

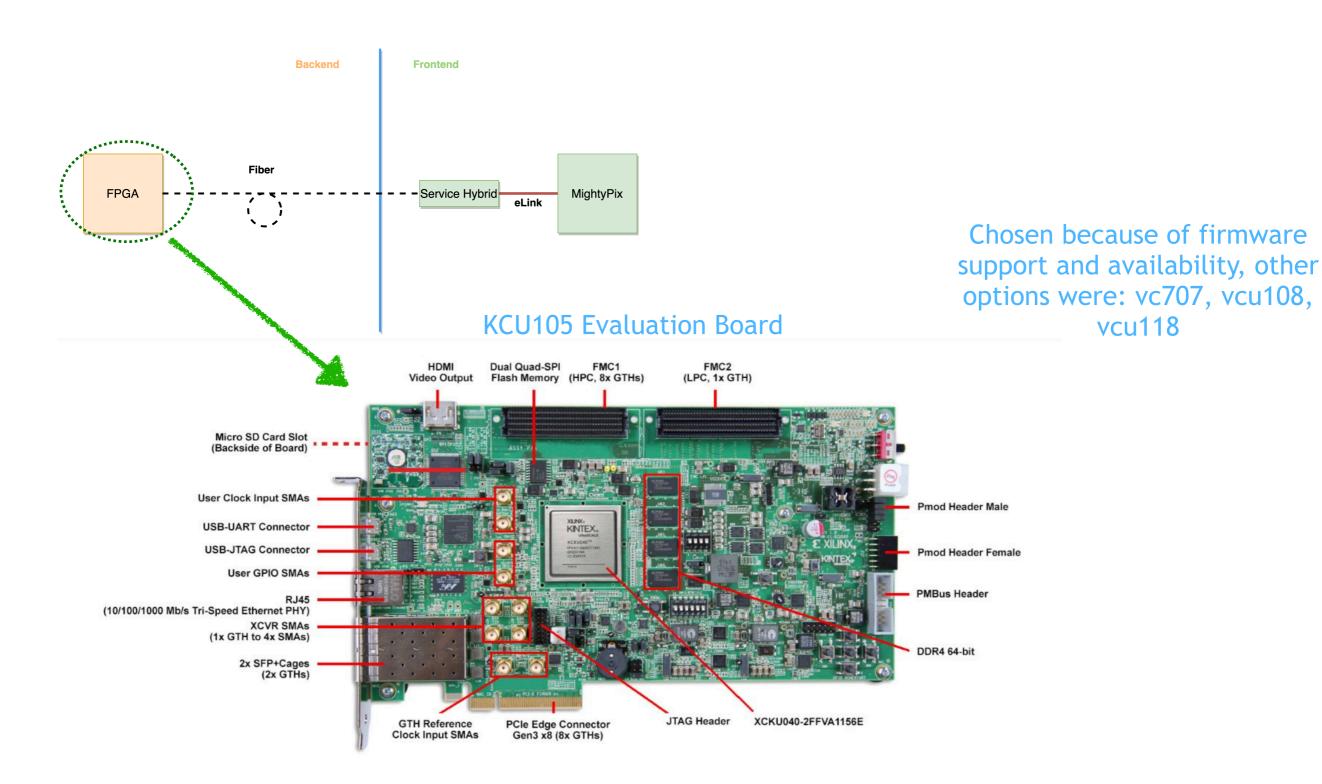

### **Available Hardware**

#### **Available Hardware**

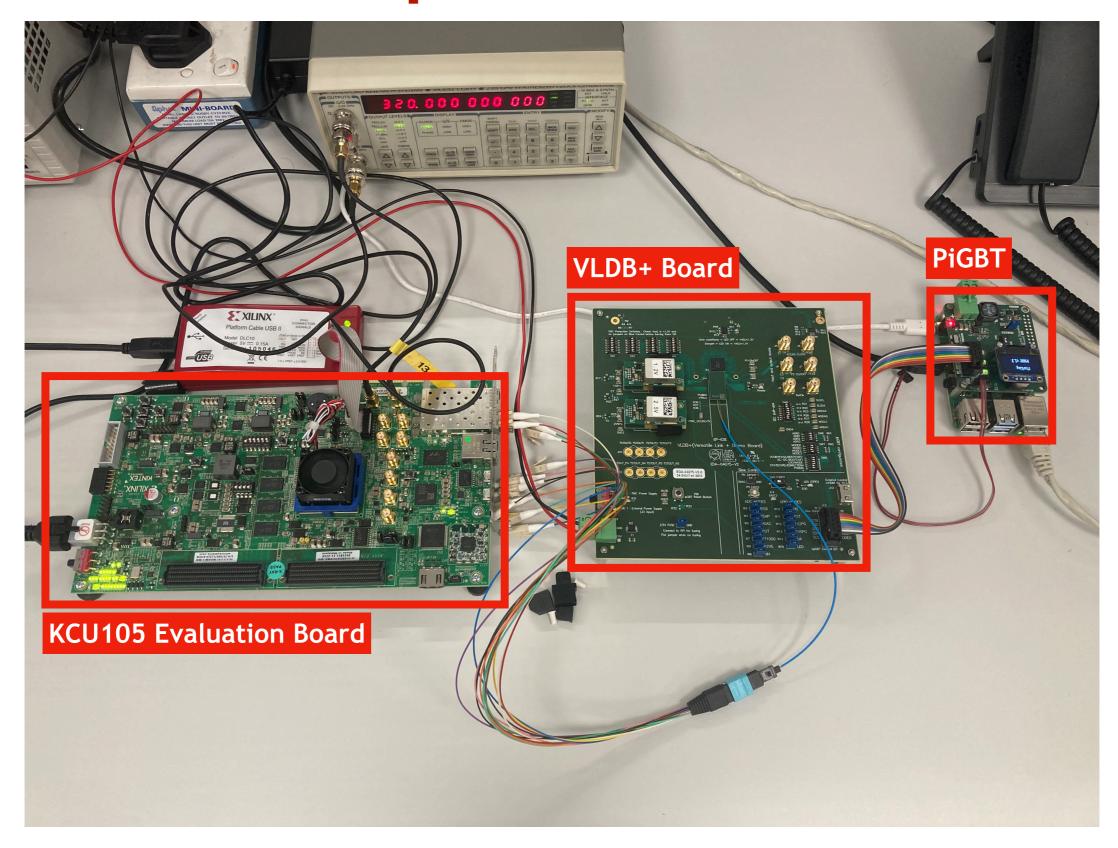

# **Hardware Setup**

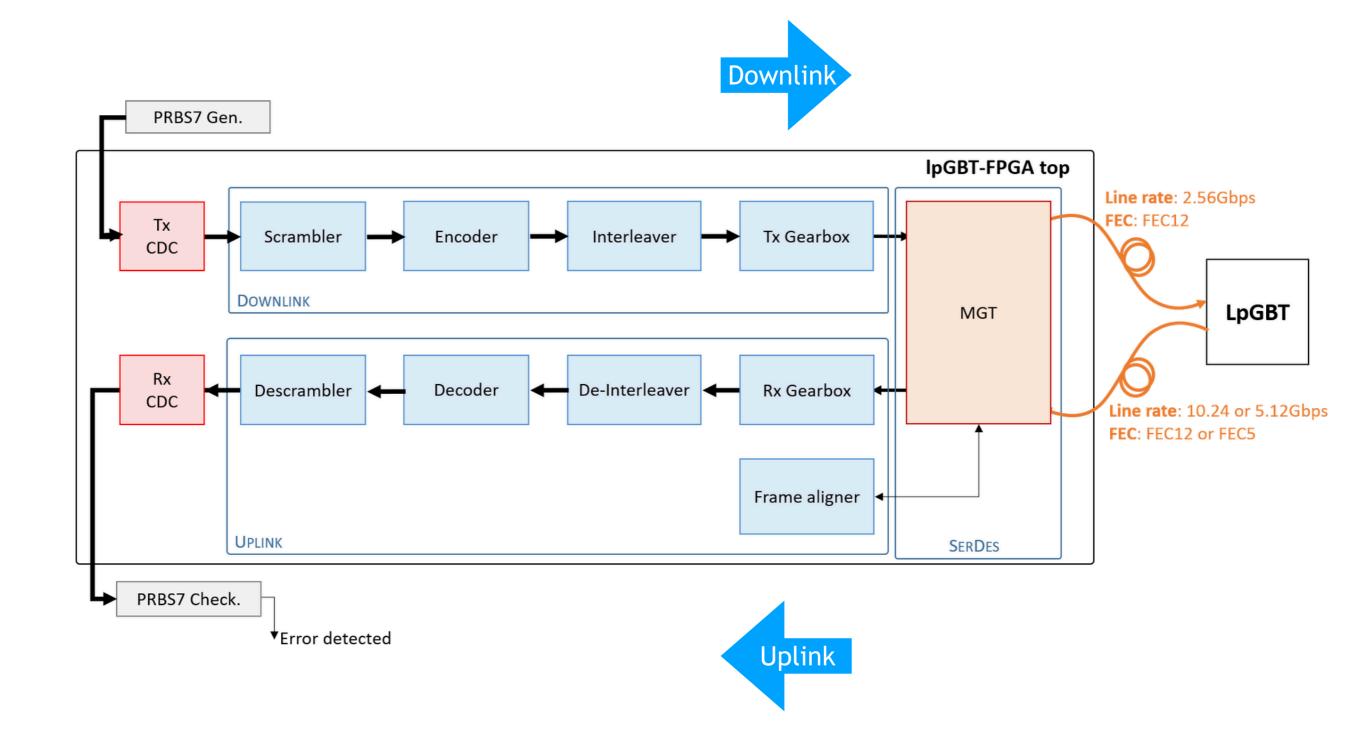

### Firmware Block

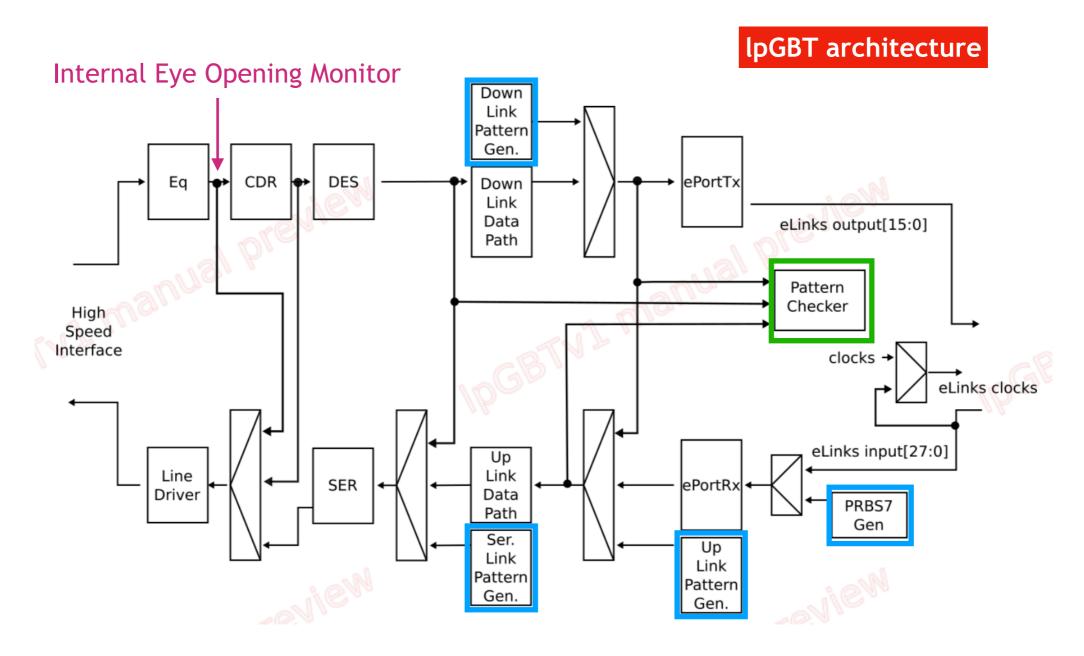

# lpGBT test features

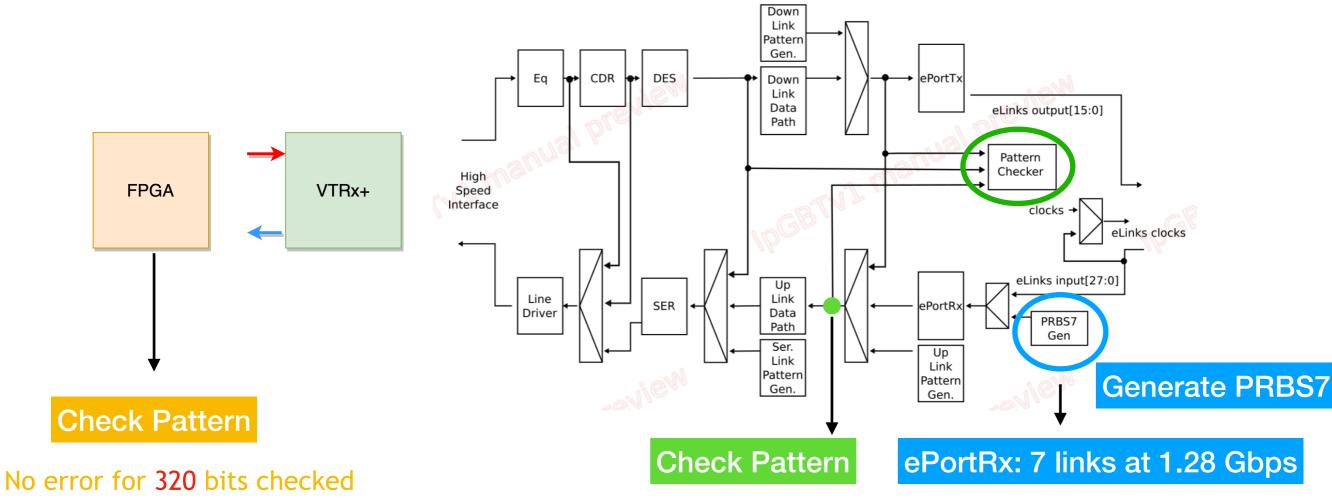

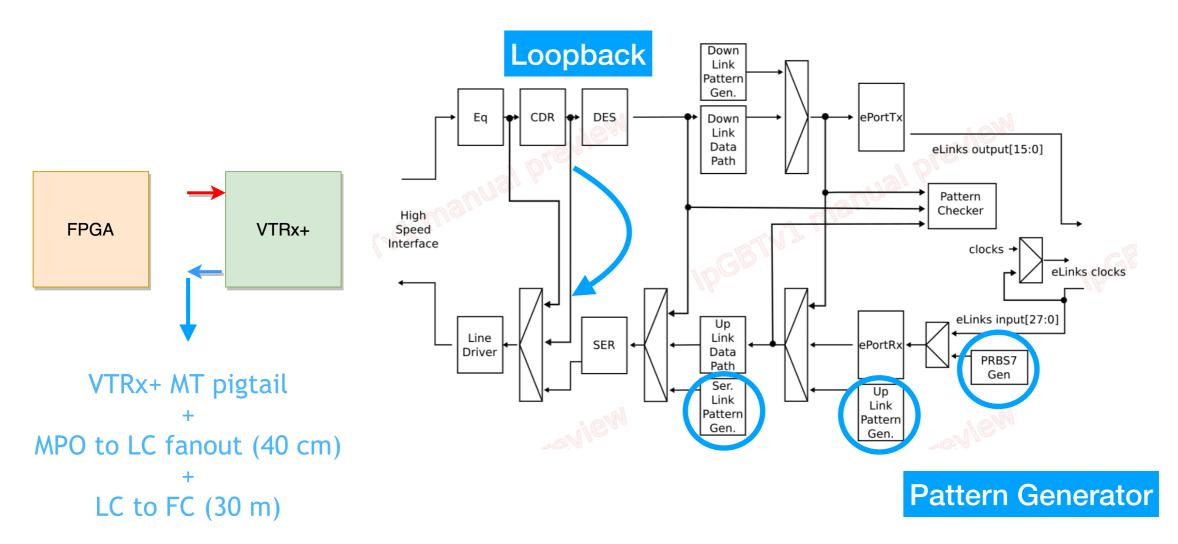

Internal Pattern Generators and Pattern Checkers

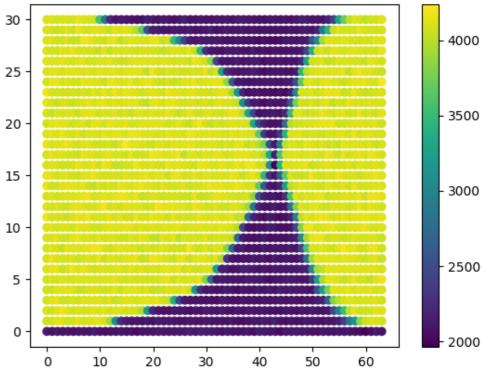

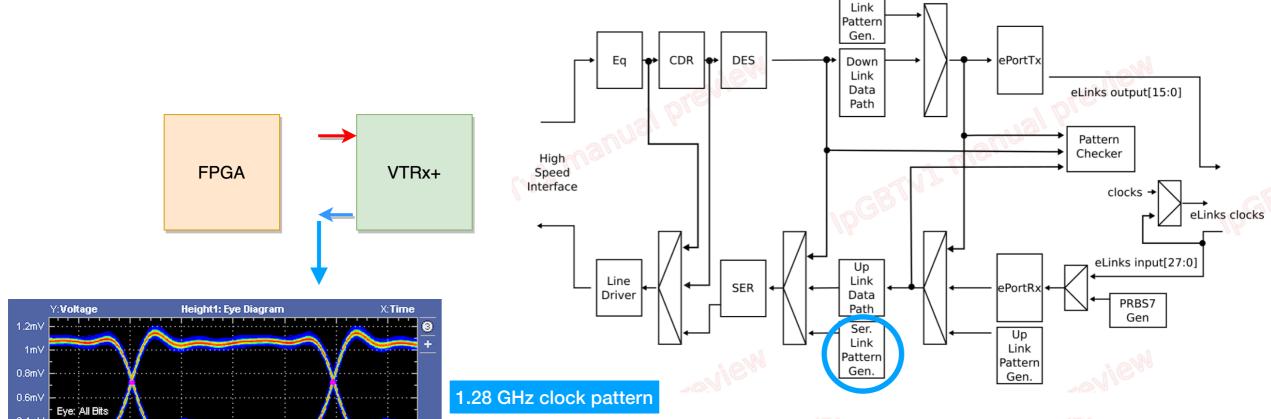

# **Downlink signal quality**

lpGBT architecture

# **Uplink signal quality**

No error for 320 bits checked (per link)

No error for 32M bits checked (per link)

- □ 32 bit checker, for 10 cycles

- Need some firmware development to properly measure BERT

# **Uplink Optical Eye: Setup**

33 GHz Scope

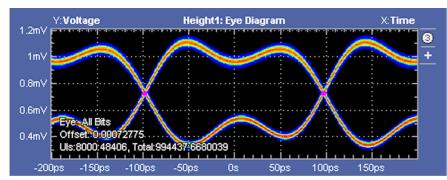

# **Uplink Optical Eye**

200ps

100ps

Uls:6000:23639, Total:87278:425503

2.56 GHz clock pattern

| Y: <b>Voltage</b> |                                       | Height1: E     | Eye Diagram |          | X:Time   |

|-------------------|---------------------------------------|----------------|-------------|----------|----------|

| 1.2mV             | · · · · · · · · · · · · · · · · · · · |                |             |          | 8        |

| 1mV               |                                       |                |             |          | <u>+</u> |

| 0.8mV             |                                       |                |             |          |          |

| 0.6mV             |                                       |                |             | <b>/</b> |          |

|                   | 0.00071927                            | 148439:1936262 |             |          |          |

| -100ps            | -60ps                                 | -20ps          | 20ps        | 60ps     |          |

5.12 GHz clock pattern

| ULSerTestPattern[3:0] | Name          | Description                                                           |

|-----------------------|---------------|-----------------------------------------------------------------------|

| 4'd0                  | DATA          | Normal mode of operation                                              |

| 4'd1                  | PRBS7         | PRBS7 test pattern (x7 + x6 + 1)                                      |

| 4'd2                  | PRBS15        | PRBS15 test pattern (x15 + x14 + 1)                                   |

| 4'd3                  | PRBS23        | PRBS23 test pattern (x23 + x18 + 1)                                   |

| 4'd4                  | PRBS31        | PRBS31 test pattern (x31 + x28 + 1)                                   |

| 4'd5                  | CLK5G12       | 5.12 GHz clock pattern (in 5Gbps mode it will produce only 2.56 GHz)  |

| 4'd6                  | CLK2G56       | 2.56 GHz clock pattern                                                |

| 4'd7                  | CLK1G28       | 1.28 GHz clock pattern                                                |

| 4'd8                  | CLK40M        | 40 MHz clock pattern                                                  |

| 4'd9                  | DLFRAME_10G24 | Loop back, downlink frame repeated 4 times                            |

| 4'd10                 | DLFRAME_5G12  | Loop back, downlink frame repeated 2 times, each bit repeated 2 times |

| 4'd11                 | DLFRAME_2G56  | Loop back, downlink frame repeated 1 times, each bit repeated 4 times |

| 4'd12                 | CONST PATTERN | 8 x DPDataPattern[31:0]                                               |

Down

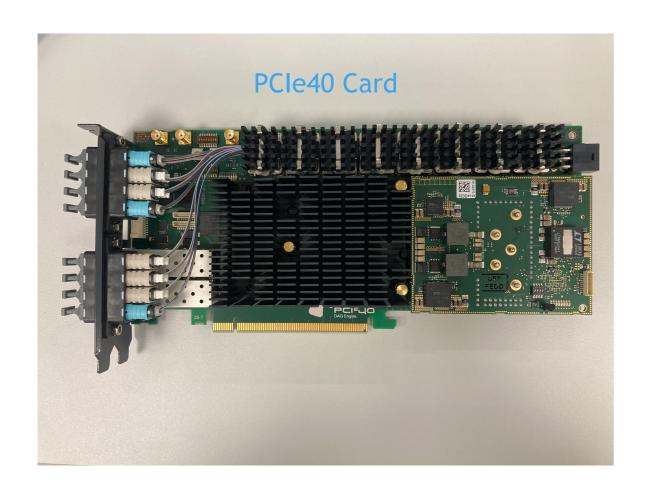

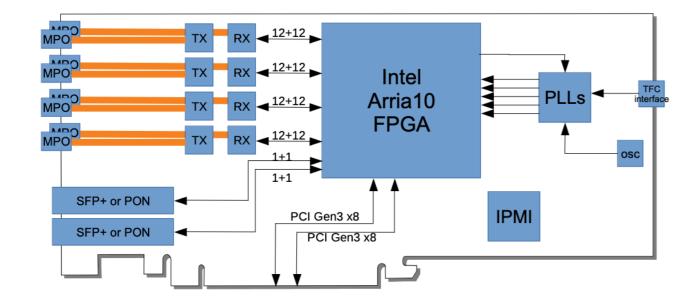

#### LHCb miniDAQ

- PCIe40/PCIe400 based DAQ card will be used in the backend for the upgraded detector

- Developing a LHCb-like miniDAQ system using PCIe40: provides 48+48 bidirectional fibre connection

- lpGBT-FPGA core is under development

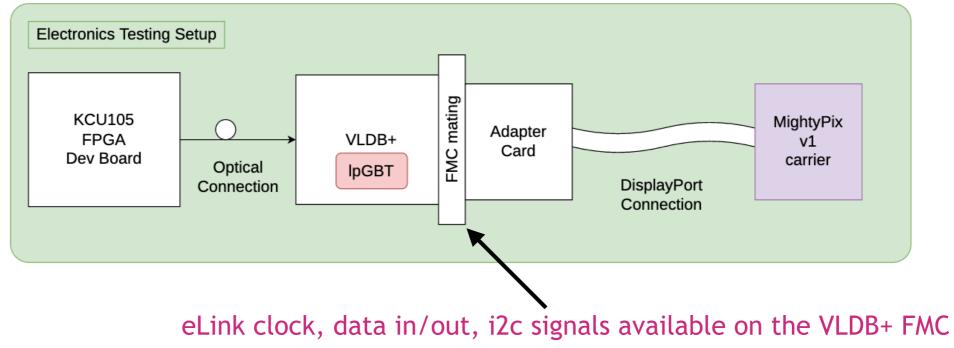

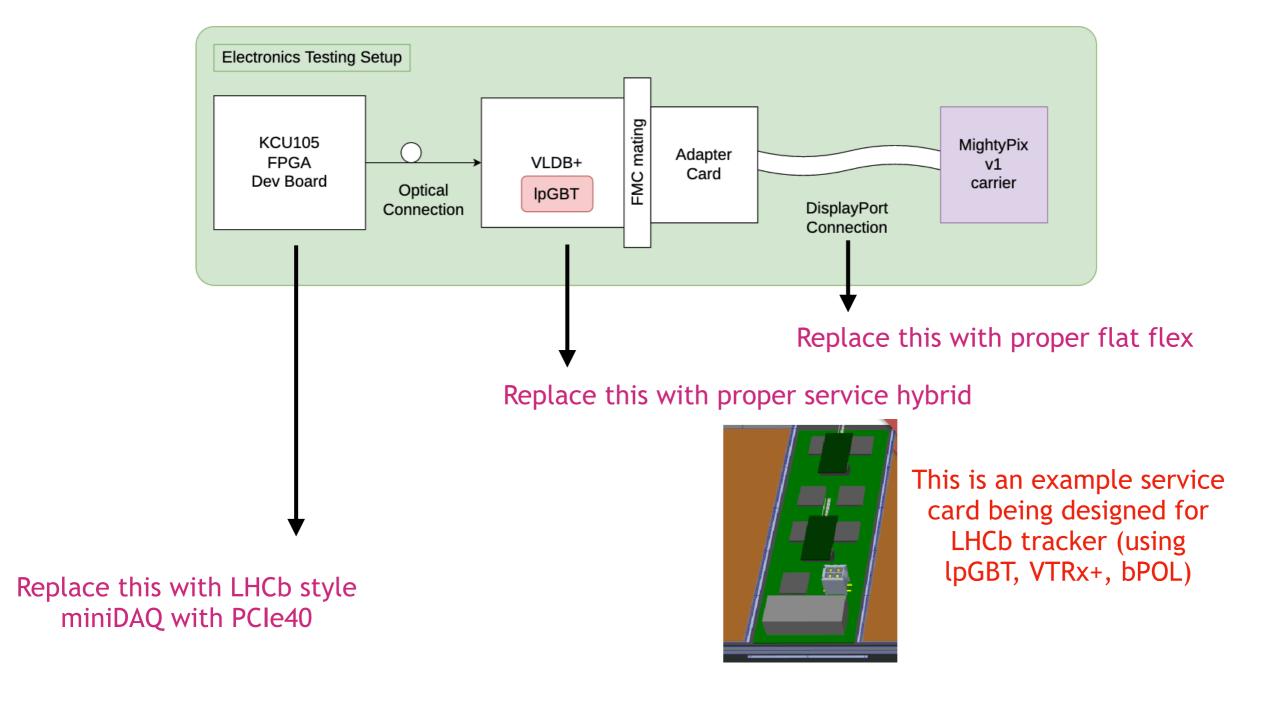

#### DAQ Chain with FE attached

- □ Add MightyPix1 (our FE sensor) on the front-end to have a complete readout chain

- ☐ This setup can also serve as a test bench for eLink (flat-flex) development, and off-chip component testing

Presently I am checking if the FE data-lines are compatible with lpGBT input

#### Final DAQ chain

□ Full system level DAQ chain

## Thank You