# ePIC SVT RDO boards (OB & Disks)

James Glover

ePIC SVT WP4+WP6 Meeting

Wed, 2<sup>nd</sup> July 2025

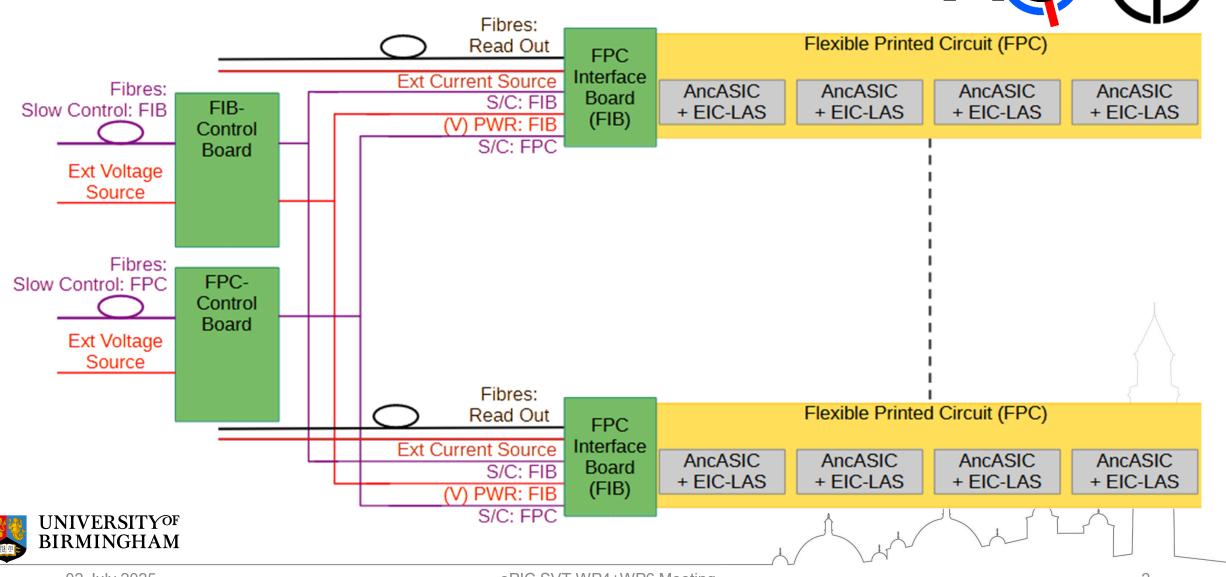

### What we had

# What has changed?

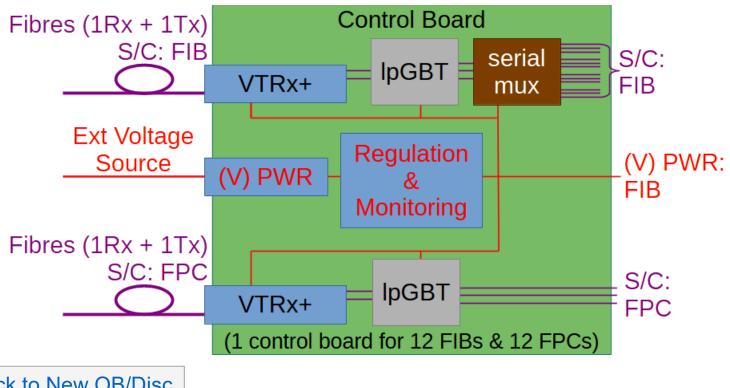

- Previously planning (hoping) to send S/Cs for as many VTRx+ (FIBs) as possible utilise most of the 16 e-links of a lpGBT.

- Has become clear that VTRx+ I<sup>2</sup>C is very specific, and communication will only work via the (3) I<sup>2</sup>C master ports of a IpGBT.

- This greatly reduces the number of VTRx+ (FIBs) controllable by 1 IpGBT – if a 1:4 serial multiplexer is used:

- Reduces from 1(IpGBT): 48(VTRx+) (assuming 4 e-links reserved for onboard use).

- To 1(lpGBT): 12(VTRx+).

- Now, both FPC-CB and FIB-CB would be 1(parent): 12(children)

boards.

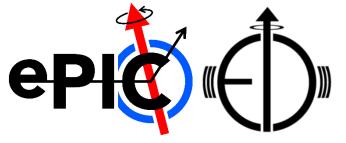

# New OB/Disk Readout Architecture epi

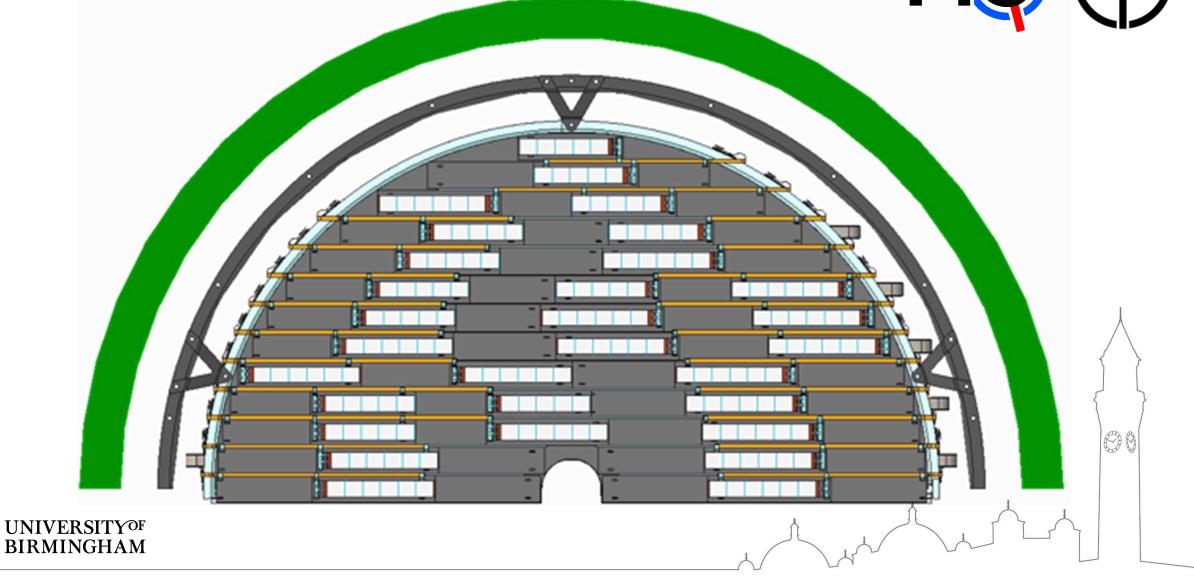

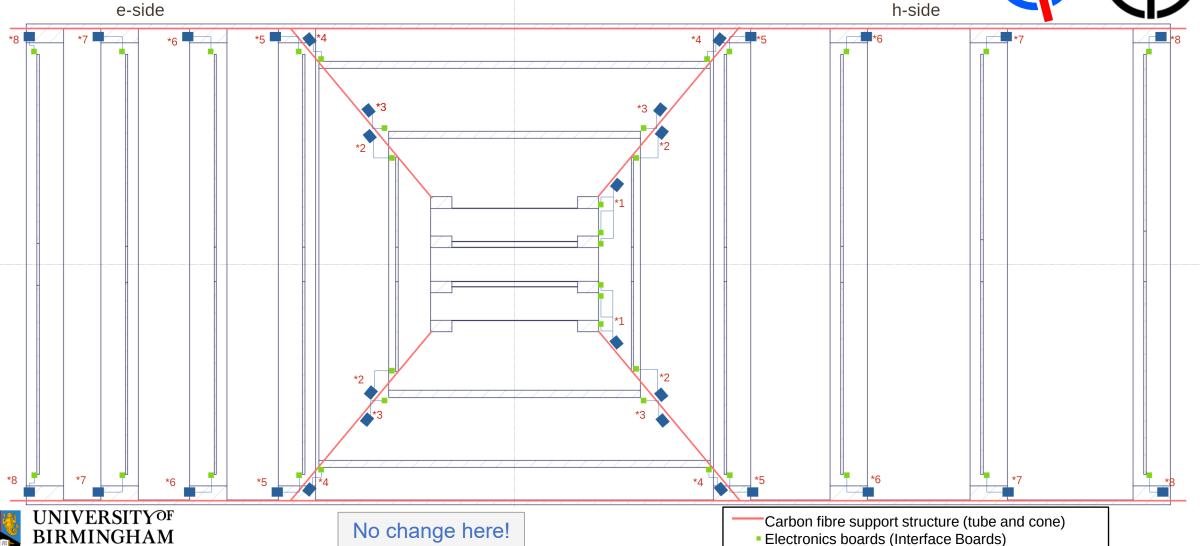

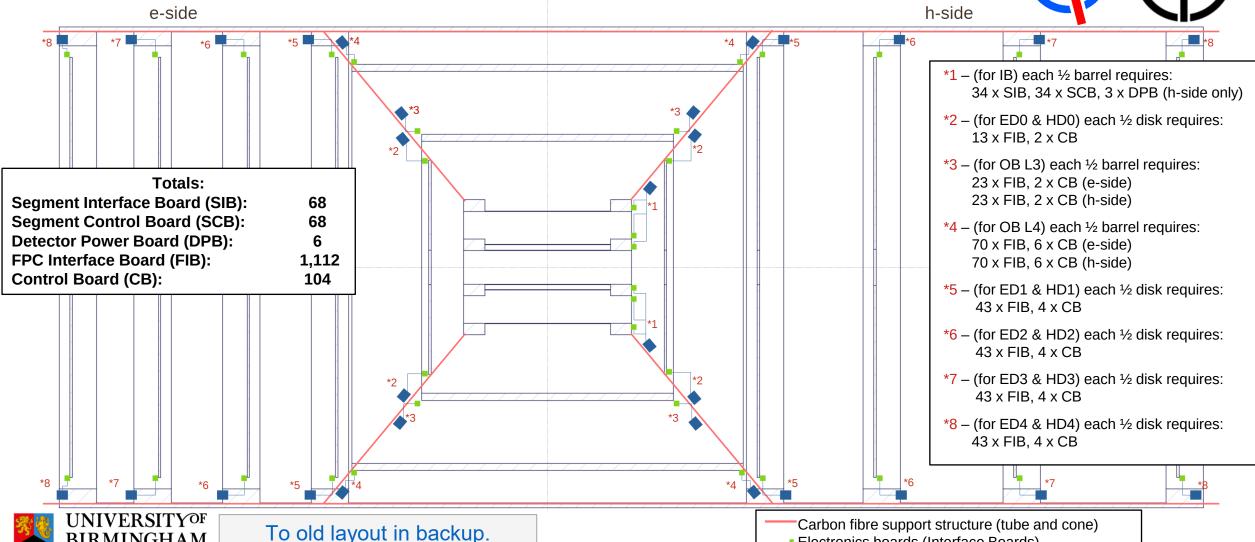

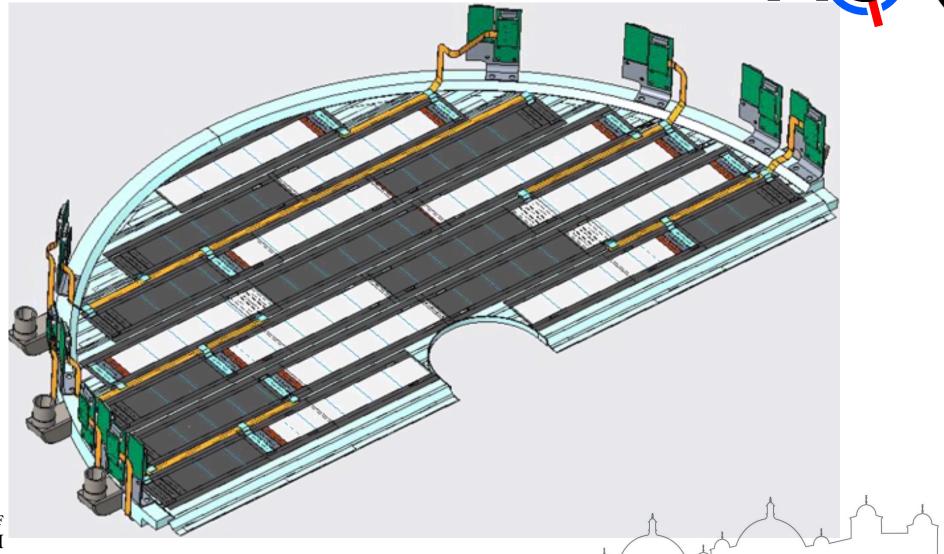

# OB/Disk RDO board layout

■ Electronics boards (Control Boards/Power Boards)

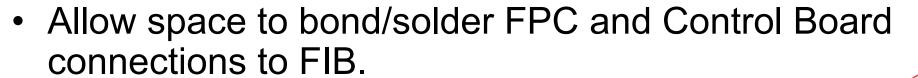

# Approximate FIB dimensions

- Shortest possible total length (5.5 cm) that CERN will produce.

- Prevent damage to VTRx+ pigtail, by mounting total length on the FIB.

Keep the board narrower than 1 EIC-LAS.

~4 mm total package height (incl. PCB).

### Control Board dimensions

- Less constrained than the FIB.

- Roughly same 65 mm length.

- Total length of VTRx+ and pigtail still to be mounted on the PCB.

- Space to bond/solder connections still needed.

- Additional space needed for:

- Power regulation.

- Monitoring.

- $IpGBT(s) \sim 1 cm^2$ .

- Serial multiplexers (FIB Control Board only) typ. <1 cm<sup>2</sup> per mux.

- Such as <u>Texas Instruments TCA9544A</u>.

- (Extra VTRx+ if 2 lpGBTs are needed).

### Control Board dimensions

- Assumed 65 × 17.5 mm additional area needed for 2<sup>nd</sup> VTRx+.

- Assumed 65 × 35 mm additional area to enable the addition of 2 lpGBTs, power regulation & monitoring, and 3 serial multiplexers.

- Total extra area: 65 × 52.5 mm (on top of the FIB dimensions).

- Board dimensions become 65 × 70 mm (same as old FIB-CB).

- Package height could be 20 mm (if DC/DCs are used).

- Consider whethereverything can work with1 lpGBT and 1 VTRx+.

- IpGBT connections will be saturated and limited to 4 e-links for internal use!

- FIB slow controls need to go through the lpGBT's I<sup>2</sup>C master connections (3/lpGBT) and each I<sup>2</sup>C master connects to a 1:4 serail multiplexer.

- 1 Control Board connects to (up to) 12 FIBs.

- FPC slow controls planned to be sent via IpGBT e-links (16/IpGBT).

- 1 Control Board connects to (up to) 12 FPCs (via the FIBs).

- 4 e-links saved for internal CB use.

- All e-links from 2<sup>nd</sup> (FIB S/C) lpGBT are also available for internal use.

Work in progress

Compare with <u>FPC-CB</u> and <u>FIB-CB</u> dimensions in backup.

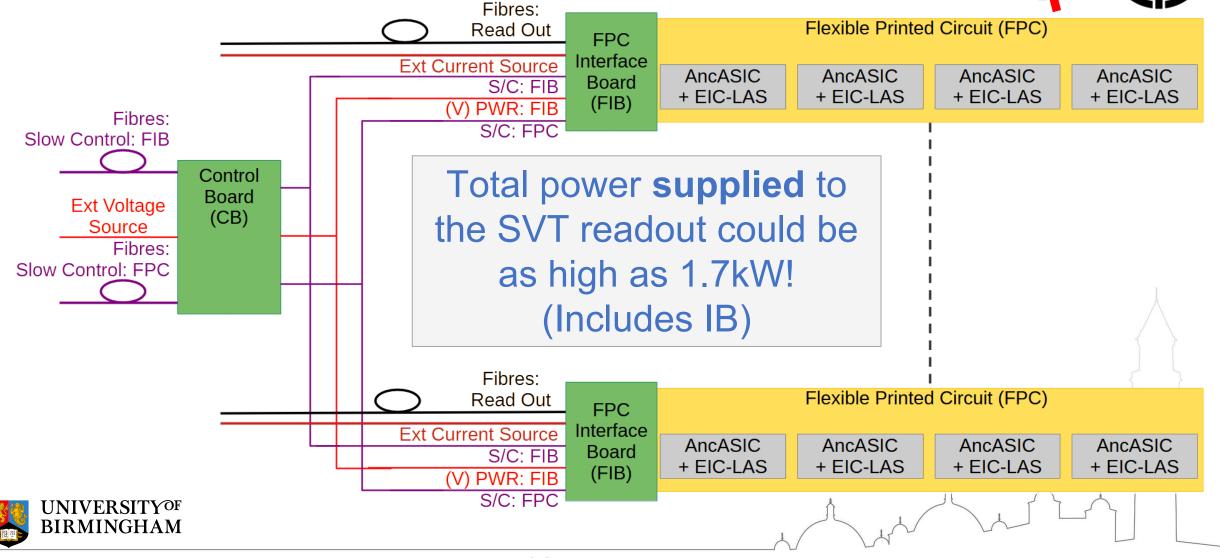

# Powering the Control Board

- On board powering needs: VTRx+, IpGBT(s) and serial multiplexers

- External powering needs: VTRx+ (on up to 12 FIBs)

Work in progress

- Up to 10 W needing to be supplied!

- About 7 W burnt off on the board.

- ~104 of these control boards needed for whole SVT.

- Could be supplied by 54V @ 0.21A.

- 0.57 mm wire diameter needed.

- Assuming aluminium wire and a V-drop of 10% over 100m.

- ~208 wires needed (source and return lines) from PSU to SVT.

Compare with FPC-CB and FIB-CB powering in backup.

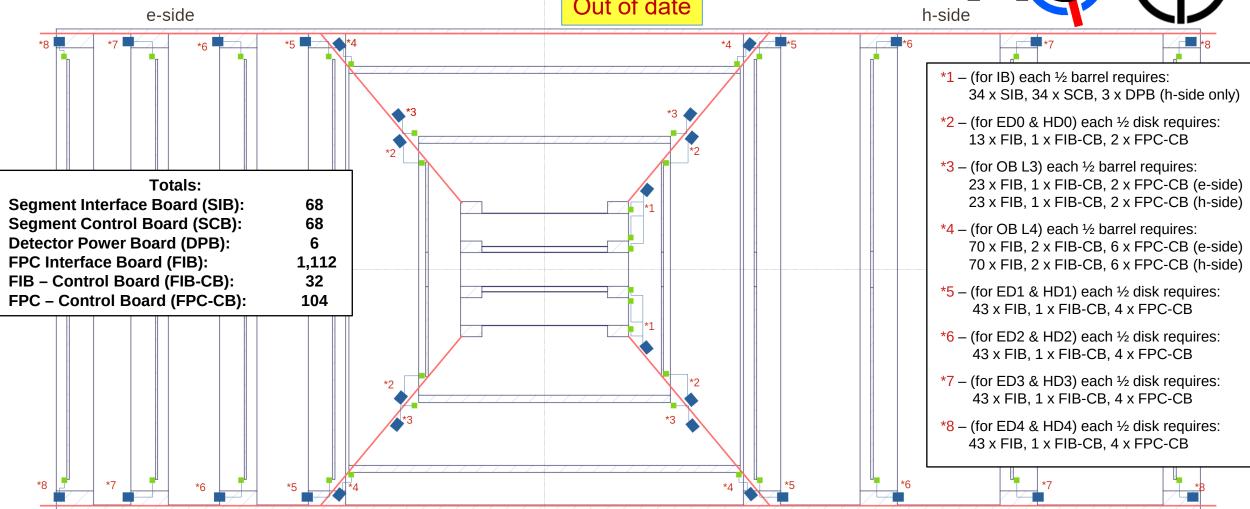

## New OB/Disk RDO board layout

BIRMINGHAM

Electronics boards (Interface Boards)

■ Electronics boards (Control Boards/Power Boards)

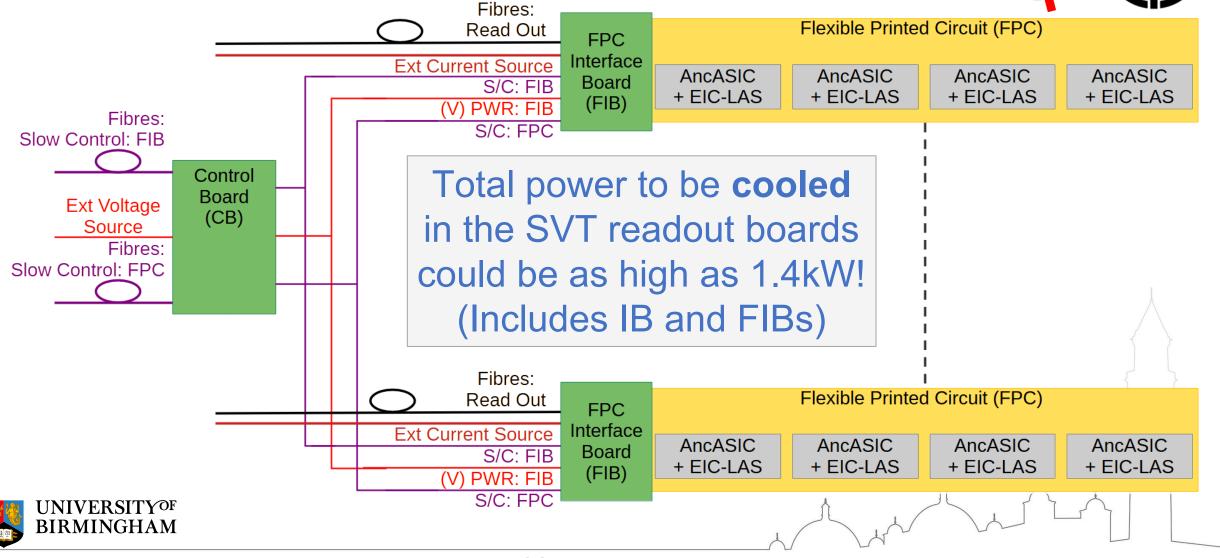

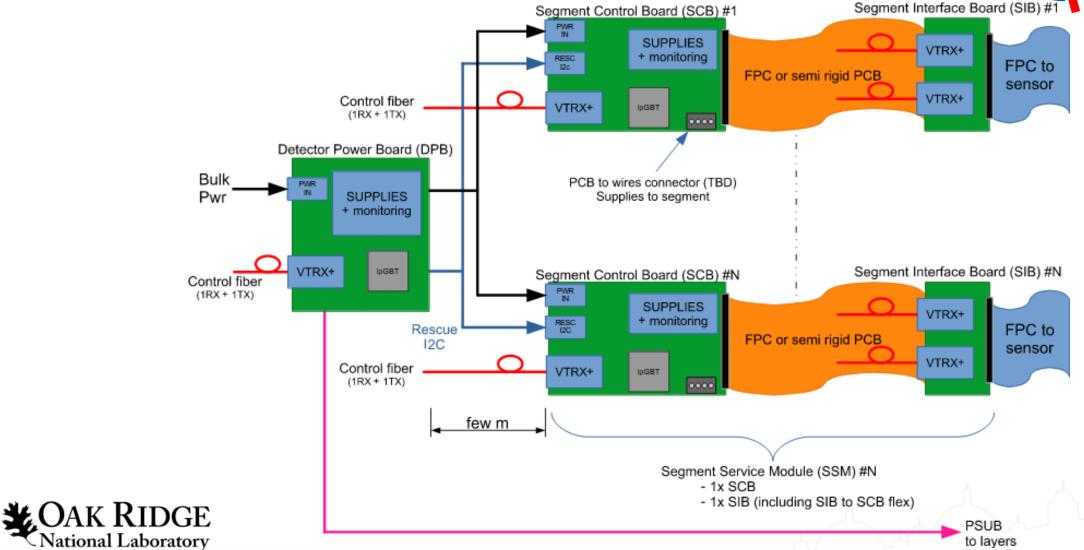

### OB/Disk Readout Architecture

### OB/Disk Readout Architecture

## Summary

Proposed to switch to a single Control Board (CB) from separate FIB-CBs and FPC-CBs.

#### Switch from:

- 104 FPC-CBs @ 65 × 47.5 mm, dissipating ~1.75 W per board.

- 32 FIB-CBs @ 65 × 70 mm, dissipating ~16.5 W per board.

#### To:

• 104 CBs @ 65 × 70 mm, dissipating ~7.1 W per board.

104 CBs @ 65 × 68.61 mm, dissipating ~6.83 W per board would be a like for like area and power match.

# Thank you very much!

Any questions?

# Additional (support) slides

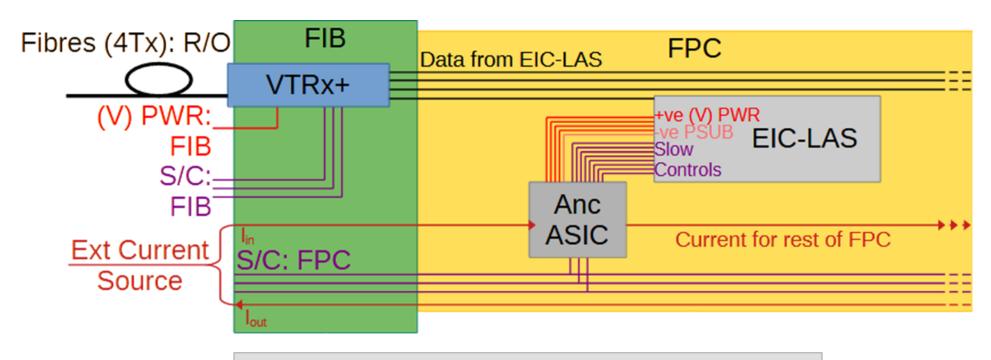

## OB/Disc: FPC Interface Board (FIB)

Back to New OB/Disc Readout Architecture.

- FIB PWR and S/C for the VTRx+ (EIC-LAS data).

- FPC current supply and S/C for AncASIC to translate to 5 power domains (incl. -ve substrate bias) and slow control protocol for EIC-LAS.

### OB/Disc: Control Board

- Use the IpGBT e-links for the FPC S/C commands.

- Use the IpGBT I<sup>2</sup>C master connections for the FIB S/C commands.

Back to New OB/Disc Readout Architecture.

### FPC-Control Board dimensions

- Assumed 65 \* 30 mm additional area to enable the addition of lpGBT, power regulation & monitoring to the area of the FPC Interface Board (FIB).

- Board dimensions become 65 \* 47.5 mm

- Package height could be 20 mm (if DC/DC are used).

- FPC slow controls planned to be sent via IpGBT e-links.

- 1 FPC-Control Board connects to (up to) 12 FPCs (via the FIBs).

- 4 e-links saved for internal FPC-CB use.

Back to CB dimensions.

Out of date

#### FIB-Control Board dimensions

- Assumed 65 \* 22.5 mm additional area to enable the addition of 12 serial multiplexers to the area of the FPC-Control Board.

- Board dimensions become 65 \* 70 mm

- Package height could be 20 mm (if DC/DCs are used).

- If FIB slow controls utilise the 12 lpGBT e-links and each e-link connects to a 1:4 serail multiplexer.

- 1 FIB-Control Board connects to (up to) 48 FIBs.

- 4 e-links saved for internal FIB-CB use.

Back to CB dimensions.

Out of date

# Powering the FPC-Control Board

- Only on board powering needs: VTRx+ and IpGBT ~2W!

- All 2W dissipated on this board.

- ~104 of these control boards needed for whole SVT.

- Could be supplied by 54V @ 40mA.

- 0.25 mm wire diameter needed.

- Assuming aluminium wire and a V-drop of 10% over 100m.

- ~208 wires needed (source and return lines) from PSU to SVT.

Back to CB powering.

Out of date

# Powering the FIB-Control Board

- Only on board powering needs: (many) serial multiplexers.

- External powering needs: up to 48 VTRx+ ~36W!

- Centralised power for up to 48 FIBs.

- About 22W burnt off on the board (water) cooling needed!

- Few of these control boards needed for whole SVT (~32).

- Could be supplied by 54V @ 0.75A.

- 1.1 mm wire diameter needed.

- Assuming aluminium wire and a V-drop of 10% over 100m.

- ~64 wires needed (source and return lines) from PSU to SVT.

Out of date

Back to CB powering.

# FIB quantities

|        | e-side | h-side | Total |

|--------|--------|--------|-------|

| L3     | 46     | 46     | 92    |

| L4     | 140    | 140    | 280   |

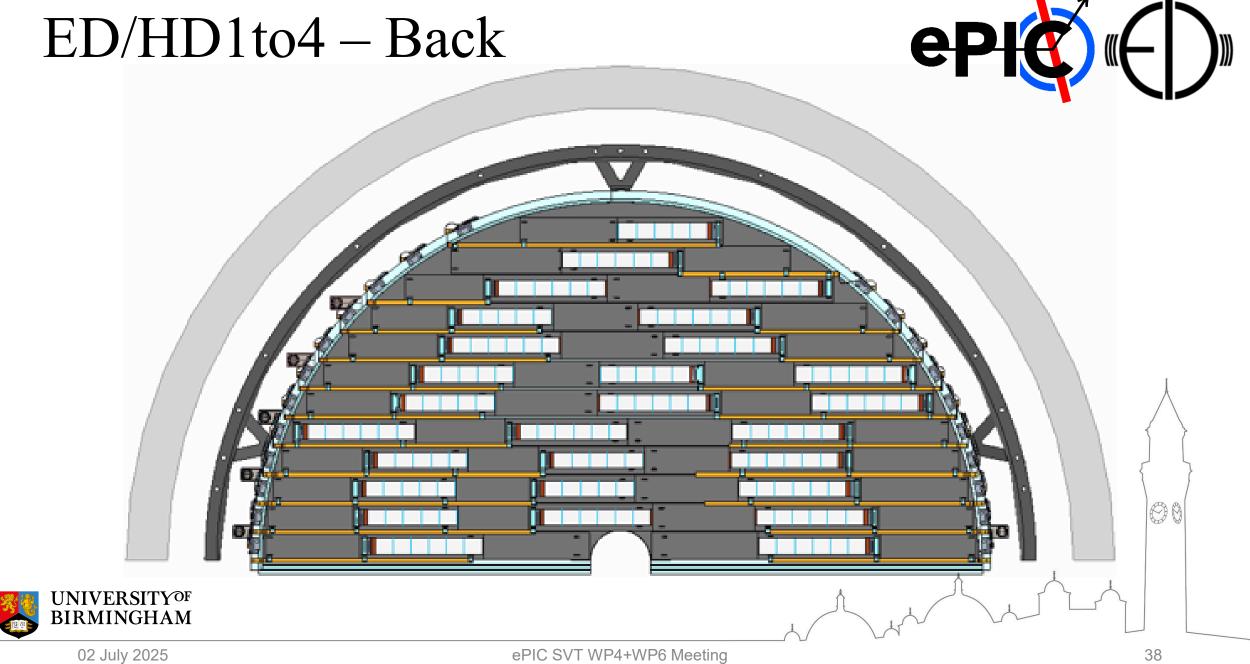

| ED/HD0 | 26     | 26     | 52    |

| ED/HD1 | 86     | 86     | 172   |

| ED/HD2 | 86     | 86     | 172   |

| ED/HD3 | 86     | 86     | 172   |

| ED/HD4 | 86     | 86     | 172   |

|        | •      |        | 1,112 |

Work in progress

## Control Boards

|        | e-side | h-side | Total |

|--------|--------|--------|-------|

| L3     | 4      | 4      | 8     |

| L4     | 12     | 12     | 24    |

| ED/HD0 | 4      | 4      | 8     |

| ED/HD1 | 8      | 8      | 16    |

| ED/HD2 | 8      | 8      | 16    |

| ED/HD3 | 8      | 8      | 16    |

| ED/HD4 | 8      | 8      | 16    |

|        |        |        | 104   |

Work in progress

# Old OB/Disk RDO board layout Out of date Out of date

UNIVERSITY<sup>OF</sup> BIRMINGHAM

Back to new layout.

- Carbon fibre support structure (tube and cone)

- Electronics boards (Interface Boards)

- Electronics boards (Control Boards/Power Boards)

### Current Source – PSU channels

Current assumptions on the number of SP chain needed in the SVT (OB + Disks) is ~1,100

- Each of these need a current of >1.5 A.

- If copper wire is acceptable, wire diameter of >3.8 mm needed!

- 5% power loss over 100m.

- 10% power loss could bring this down to 2.7 mm diameter.

- Aluminium would require a larger diameter.

- >2,000 wires needed (source and return lines) from PSU to SVT.

Work in progress

#### IB Readout Architecture

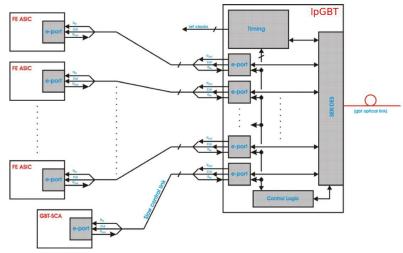

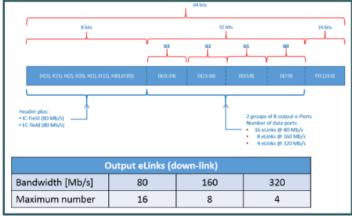

# lpGBT Protocol

- Front Ends connect to "e-links"

- The fiber protocol includes "Forward Error Correction"

- Downlink runs at 2.56 Gbps

- Downlink frame is 64bit wide, of which 32 bits are payload

- 1.28 Gbps payload

- Up to 16 e-links @ 80 Mbps

- Uplink runs at either 10.24 Gbps or 5.12 Gbps

- Uplink frame is either 128bit or 256bit

- 256bit frame contains 192bits of payload (7.68 Gbps)

- Up to 24 e-links at either 160 Mbps or 320 Gbps

#### Downlink Line Rate: 2.56 Gbps

Line Rate: **2.56 Gbps**32 out of 64 bits are data:

Payload = **1.280 Gbps**

#### Data Uplink

192 out of 256 bits are data: Payload = **7.680 Gbps**

| Input eLinks (up-link)   |     |      |     |       |     |       |      |     |      |       |     |      |

|--------------------------|-----|------|-----|-------|-----|-------|------|-----|------|-------|-----|------|

| Up-link bandwidth [Gb/s] |     | 5.12 |     |       |     | 10.24 |      |     |      |       |     |      |

| FEC coding               |     | FEC5 |     | FEC12 |     |       | FEC5 |     |      | FEC12 |     |      |

| Bandwidth [Mb/s]         | 160 | 320  | 640 | 160   | 320 | 640   | 320  | 640 | 1280 | 320   | 640 | 1280 |

| Maximum number           | 28  | 14   | 7   | 24    | 12  | 6     | 28   | 14  | 7    | 24    | 12  | 6    |

|                   |      | 5.12 Gbps |      | 10.24 Gbps |  |

|-------------------|------|-----------|------|------------|--|

| Field             | FEC5 | FEC12     | FEC5 | FEC12      |  |

| Frame [bits]      |      | 128       |      | 256        |  |

| Header [bits]     |      | 2         |      | 2          |  |

| IC [bits]         |      | 2         |      | 2          |  |

| EC [bits]         |      | 2         |      | 2          |  |

| D [bits]          | 112  | 96        | 224  | 192        |  |

| FEC [bits]        | 10   | 24        | 20   | 48         |  |

| LM [bits]         | 0    | 2         | 6    | 10         |  |

| Correction [bits] | 5    | 12        | 10   | 24         |  |

| # of eLink groups | 7    | 6         | 7    | 6          |  |

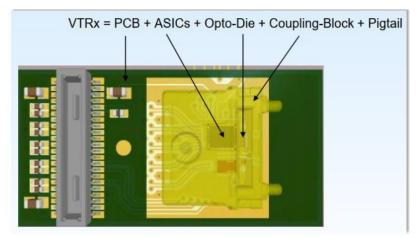

### VTRx+ Front-end Module

#### Versatile

Up to 4 Tx + 1 Rx, configurable by masking channels

#### Miniaturised

20 x 10 x 2.5 mm

#### Pluggable

Electrical connector

#### Data-rate

Tx: up to 4×10 Gb/s, Rx: 2.5 Gb/s

#### Environment

Temperature: -35 to + 60 °C

Total Dose: 100 Mrad

Total Fluence: 1x10<sup>15</sup> n/cm<sup>2</sup> and 1x10<sup>15</sup> hadrons/cm<sup>2</sup>

#### Status

- Pre-production ongoing

- Solving problems with module assembly

- Alignment of optical components

- Ramping up to 2k modules/month in 2023

#### VTRx+ connectors

Versatile Link

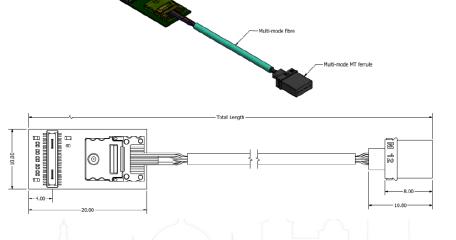

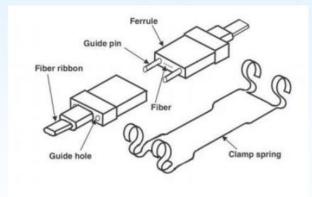

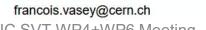

#### 1.2 VTRx+ Pigtail

#### From:

https://indico.cern.c h/event/799025/con tributions/3486288/ Pigtail being finalized

- Rad hard fibre

- 5 individual fibres in loose tube

- MT termination

- Not dismountable

Dense connectivity at expense of handleability

Or with MT to MPO adapter

if you have space

TWEPP, 3 Sep 2019

Ž.

29

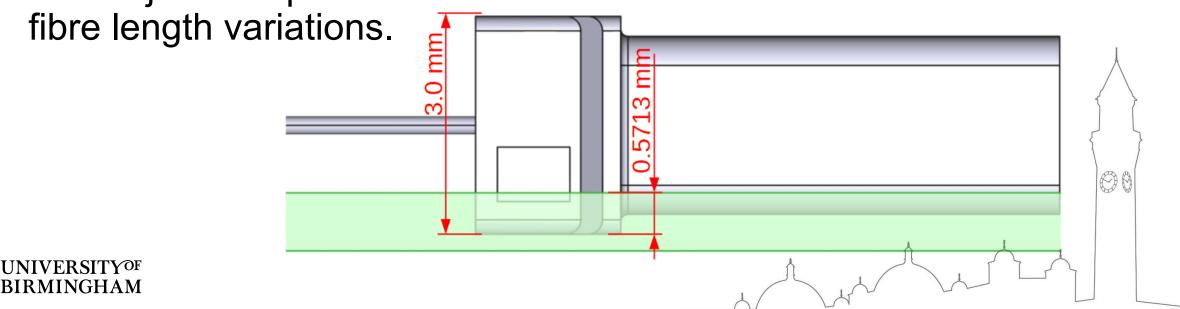

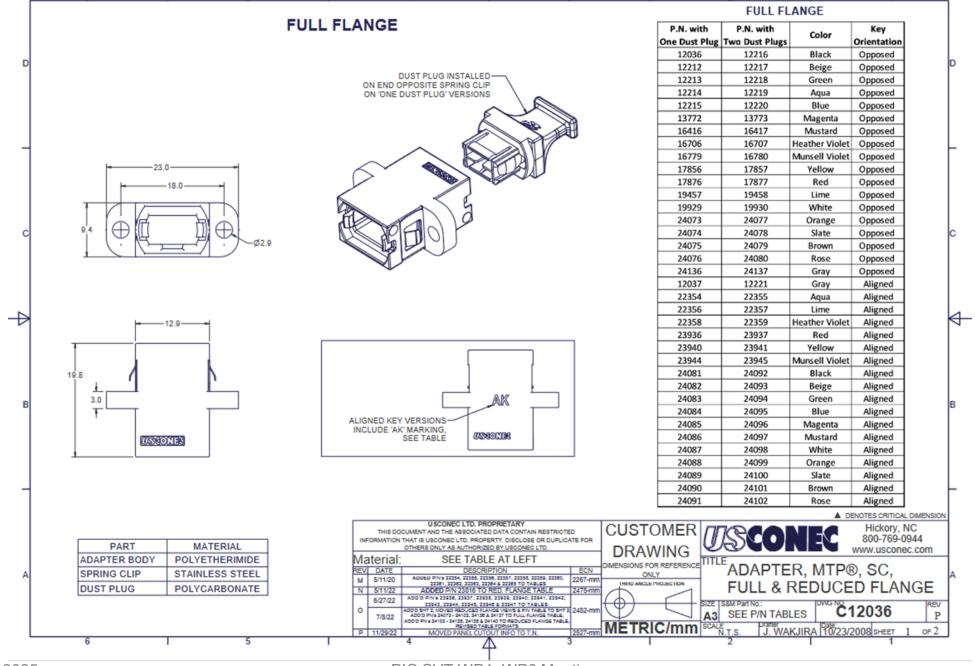

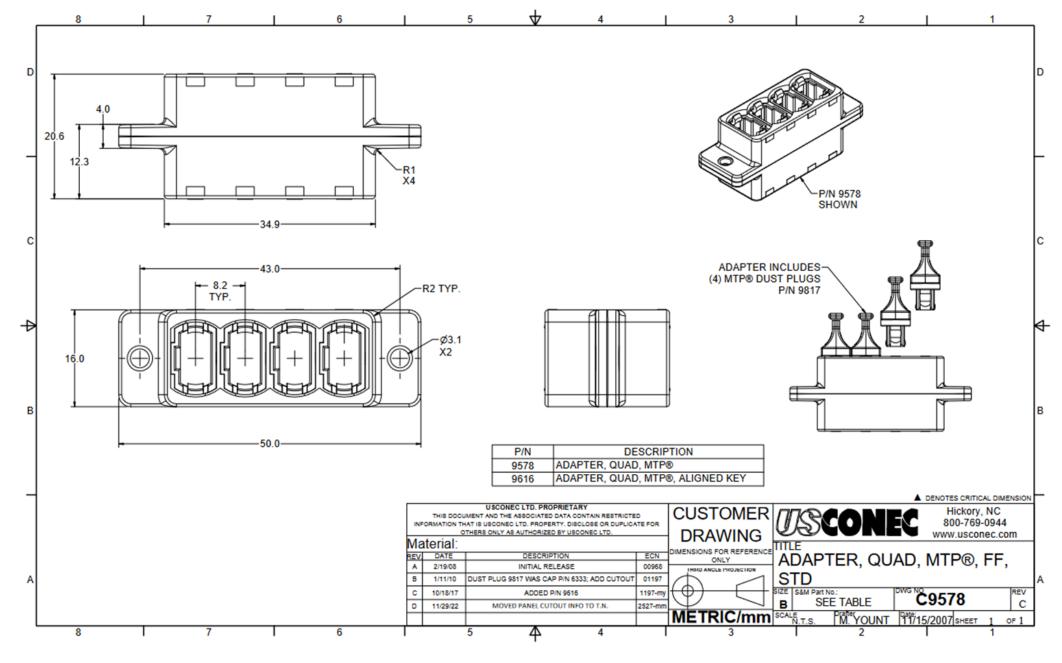

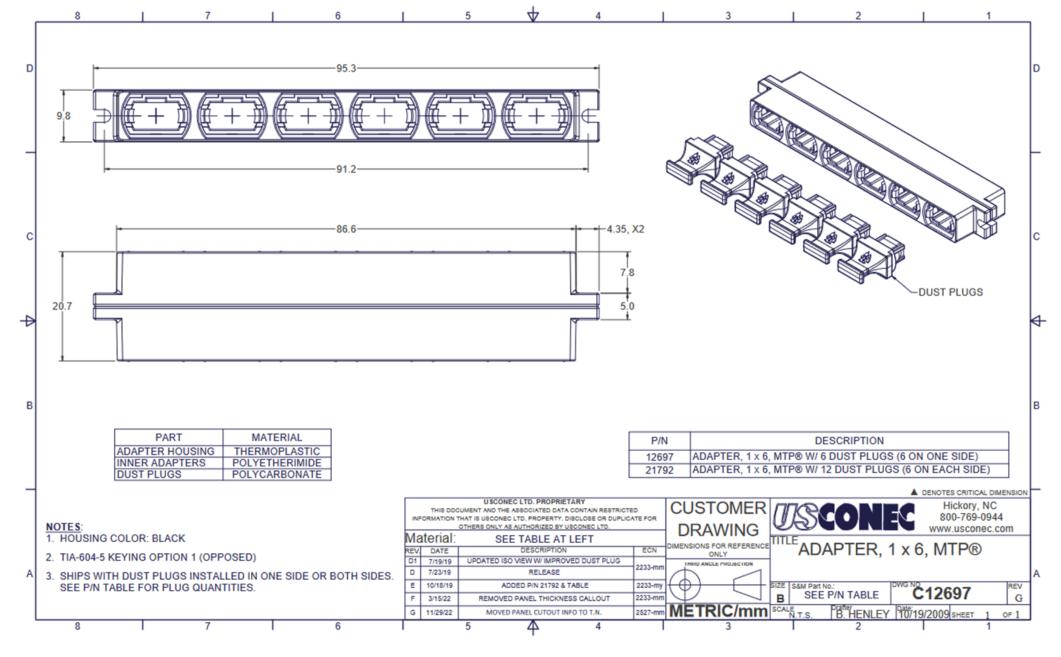

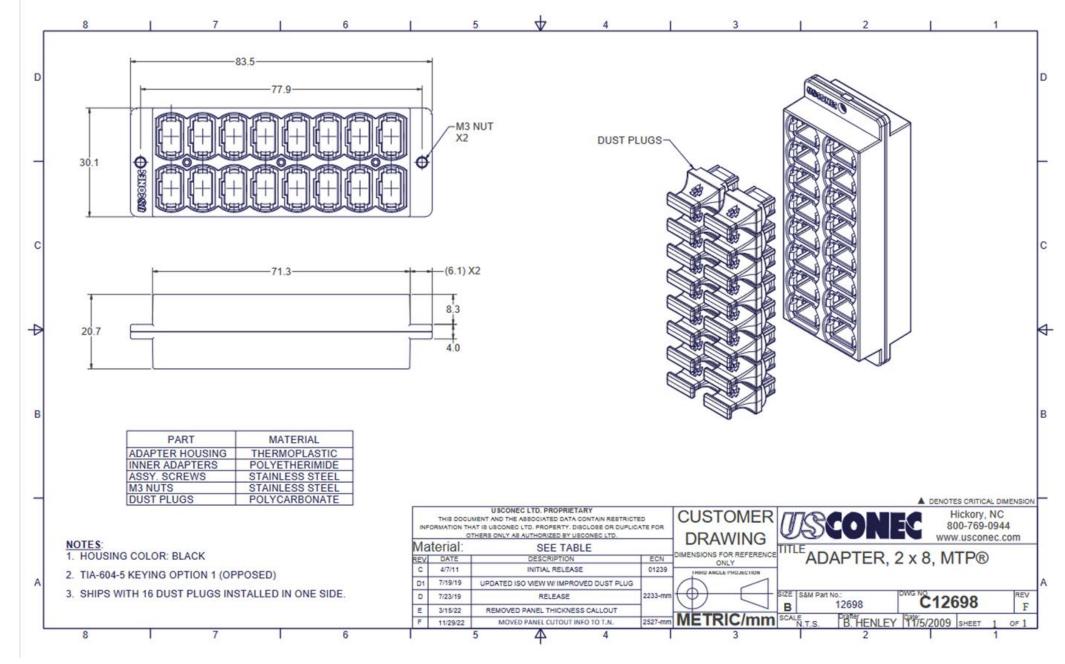

### Connector issue

- The connector that CERN supply on the end of the fibres is thicker than the VTRx+ with clip.

- Fibres cannot lay completely flat.

Need to look at options for mounting the connector to the PCB with adjustable position – to account for connector thickness and

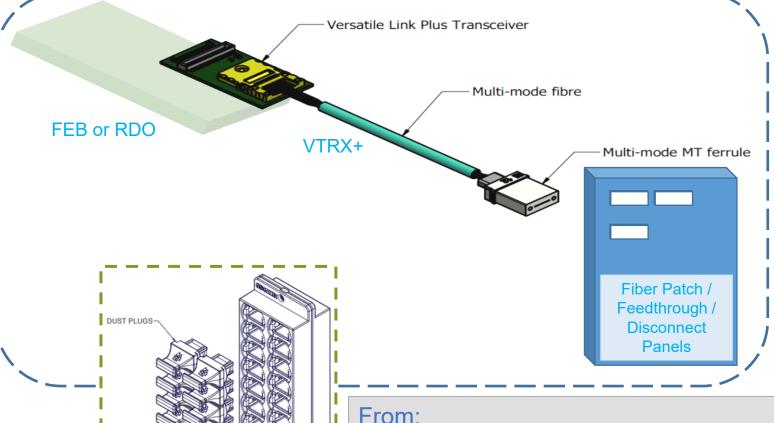

#### Services – VTRX+

- Recently switch all applicable detectors over from RDOs to VTRX+ modules

- Modules will be placed on each detector

- The modules can only push the signal up to 2m in length so there needs to be a fiber patch to convert to MTP fiber

- Each module gets 1 fiber patch, locations will vary from detector to detector

Total VTRX+ modules needed listed

below

| Sub-Detector | Qty  |

|--------------|------|

| SVT          | 1579 |

| MPGD EE      | 64   |

| MPGD HE      | 64   |

| MPGD IB      | 128  |

| MPGD uRwell  | 384  |

| TOF Disk     | 212  |

| TOF Barrel   | 288  |

| dRICH        | 1242 |

| pfRICH       | 68   |

Fiber Patch

Panel

ePIC SVT WP4+WP6 Meeting

02 July 2025

https://indico.bnl.gov/event/24729/contr

ibutions/97310/attachments/57760/991

91/TIC%20Meeting%2024.10.07.pptx

# ED/HD0 – Back

## ED/HD1to4 – Front