# eRD109 Update - H2GCR0C3A

Norbert Novitzky (ORNL) With a lot of help from Miklos Czeller, Gabor Nagy and Shihai Jia

ORNL is managed by UT-Battelle LLC for the US Department of Energy

### Some future tests

### Finally starting to sum:

- The summing board is designed

- There is a switch to 'sum' 1-8 SiPM's, using the BIC 4x4 SiPM array for this

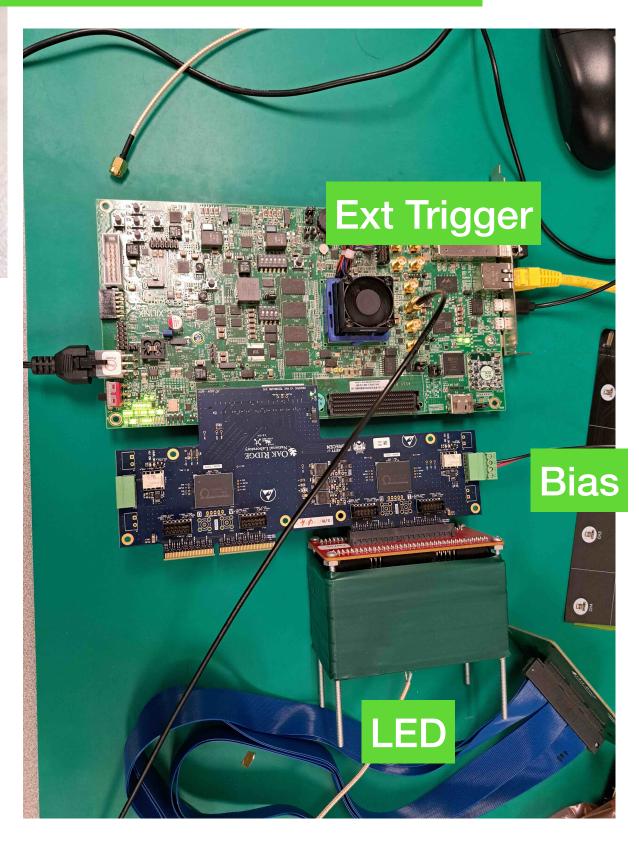

- We are starting the testing with the LED setup

### LED calibration circuit:

- We saw a nice LED signal from the PWO4 tests

- Testing now with the BIC SiPM array and external function generator

- We rerouted the SiPM pulser from the H2GCROC to the FPGA

#### Switches for the summing

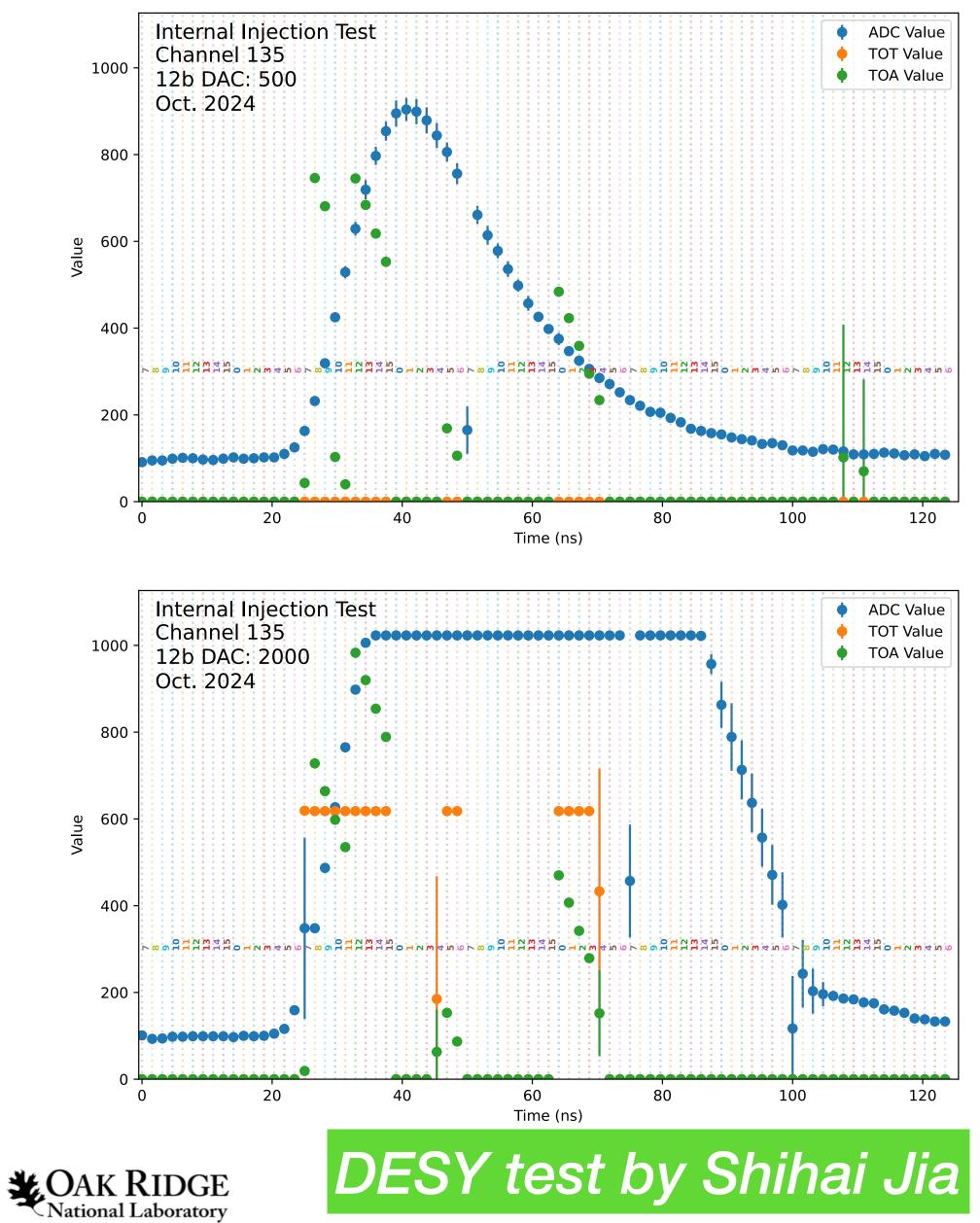

### Internal injection and TOA

- It appears for clock phases 0,1,2,3,4, the ToA and ToT values will shift by one bunch crossing

- Structure stems from each TDC being composed of 3 stages:

- + 2-bit grey counter LSB ≈ 6.25 ns

- Coarse 5-bit TDC LSB ≈ 200 ps

- Fine 3-bit TDC LSB ≈ 25 ps

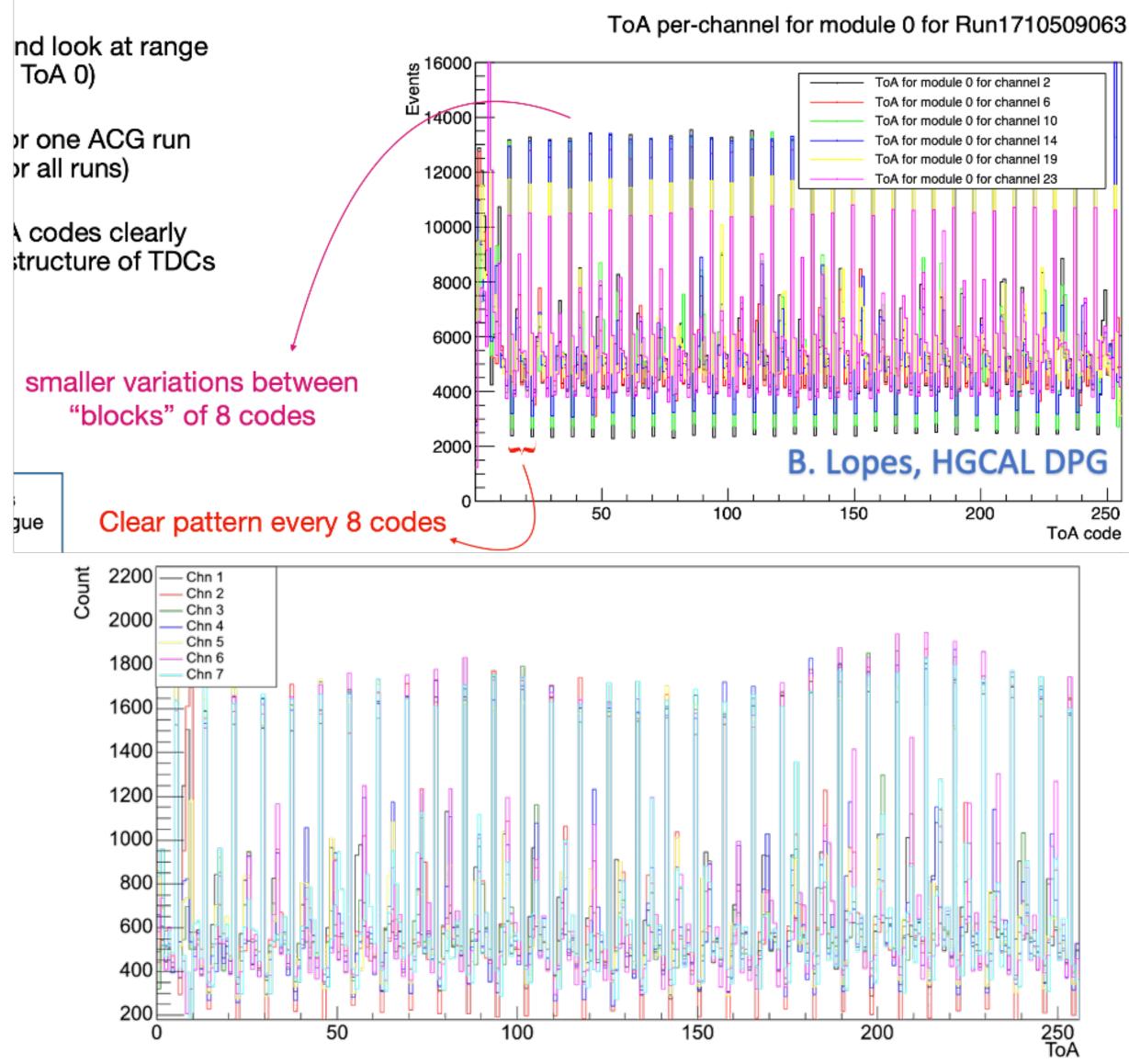

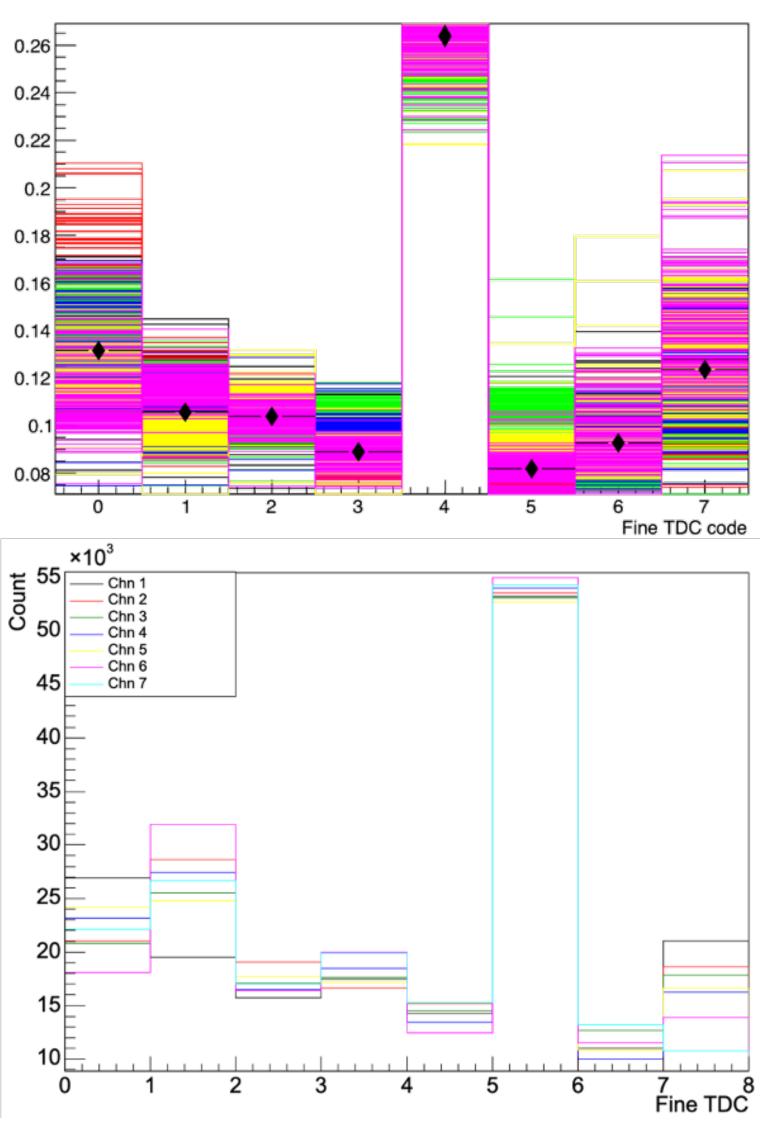

# ToA calibration – fine TDC

#### ToA per-channel for module 0

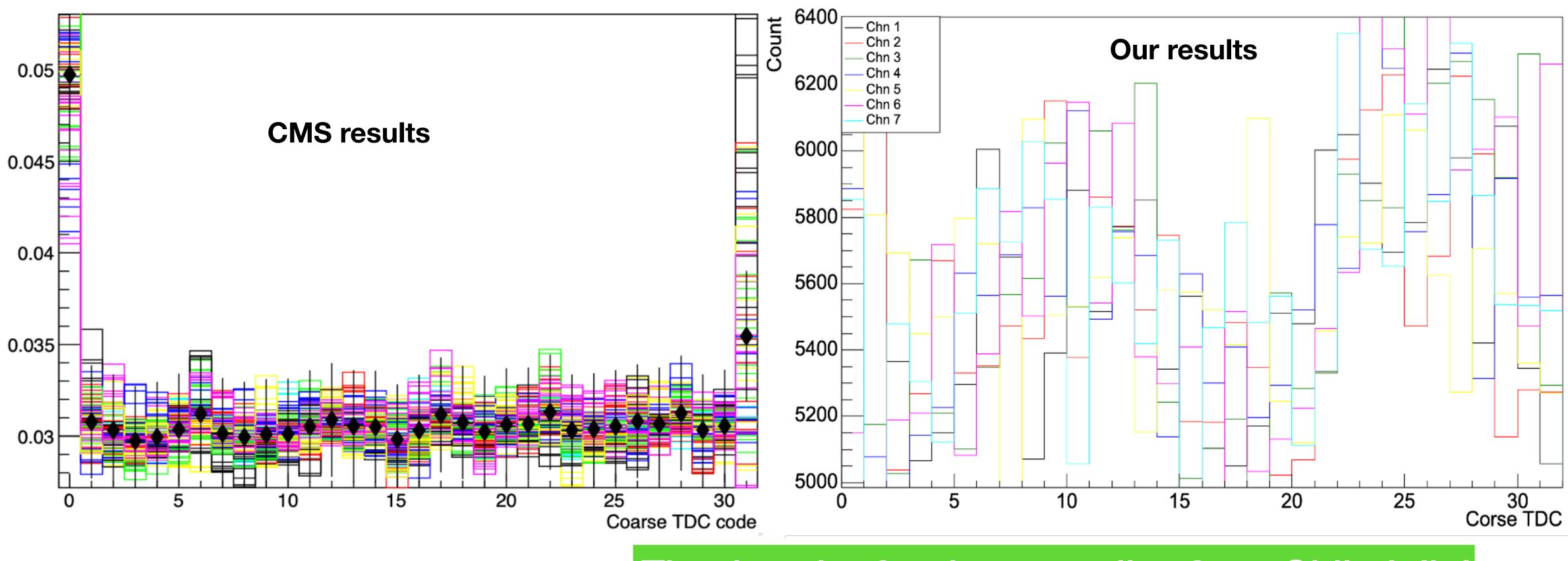

## ToA calibration – coarse TDC

Ideal fine TDC coverage:

|                            | 000 | 001 | (   | 010 | 011 100 |    | 101 | 110 | 111 |

|----------------------------|-----|-----|-----|-----|---------|----|-----|-----|-----|

| What it really looks like: |     |     |     |     |         |    |     |     |     |

|                            | 000 | 001 | 010 | 011 | 1       | 00 | 101 | 110 | 111 |

Thanks a lot for these studies from Shihai Jia!