# FEBs for ePIC MPGDs Technical and organizational choices

Irakli Mandjavidze

Irfu, CEA Saclay Gif-sur-Yvette, 91191 France

MPGD-DSC general meeting 5/Dec/2024

- Considered readout architecture

- Low voltage powering

- Frontend partitioning

- Space constraints

- Summary

### <u>cea</u> irfu

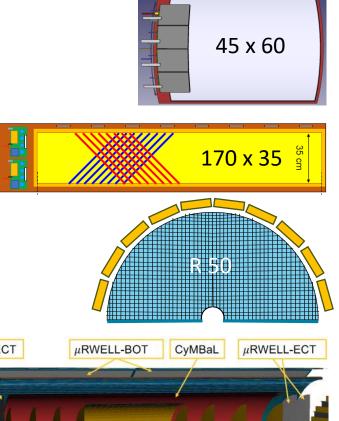

## Reminder on MPGD sub-systems and channel counts

- Cylindrical Micromegas Barrel Layer : CyMBaL : ~30k channels

→ 32 tiles of 1024 channels each

- µRWELL Barrel Outer Tracker : µRWell-BOT : ~100k channels

- $\rightarrow$  24 modules of 4 096 U-V strips each

- µRWell End Cap Tracker : µRWell-ECT : ~30k channels

→ 8 half-disks of 4 000 X-Y strips each

- ~160k-channel heterogeneous system

- $\rightarrow$  Micromegas, µRWell, barrel, endcap, curved, planar, circular

- Common approach to acquire data from different types of ePIC MPGDs

- $\rightarrow$  Use same frontend ASIC

- Salsa under development

- $\rightarrow$  Share frontend design between groups

- Adapt form factor if needed

#### Electron-Ion Collider

irakli.mandjavidze@cea.fr

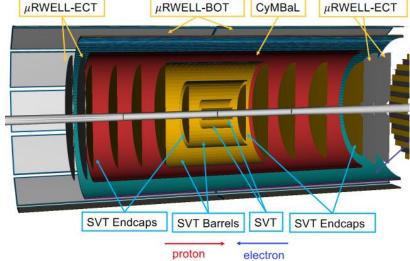

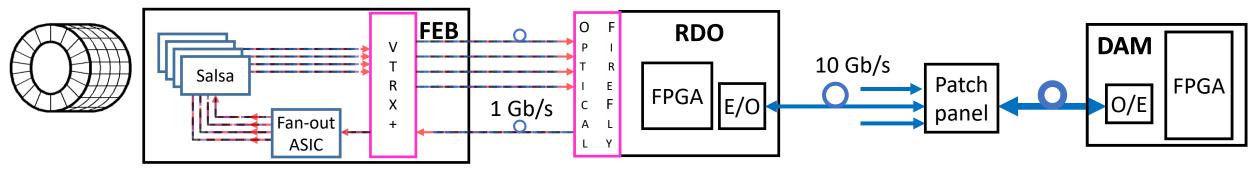

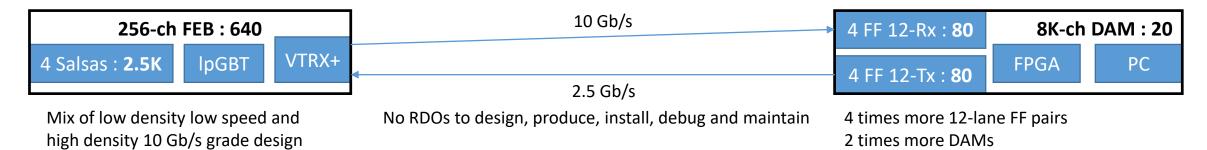

• Option 1 : FEB-RDO-DAM based on direct Salsa-VTRX+ interface

• Option 2 : FEB-DAM based on IpGBT-Vtrx+ interface

### <sup>222</sup> <sup>irfu</sup> 160K-ch MPGD readout configurations and component count

#### • Option 1 : FEB with direct Salsa-VTRX+ interface

Low density 1 Gb/s grade design

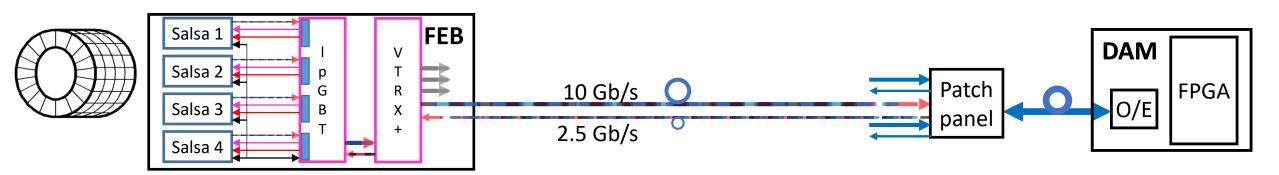

#### • Option 2 : FEB with direct DAM interface

### Power

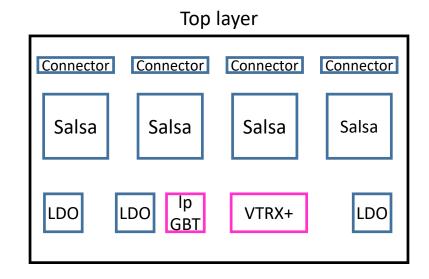

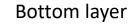

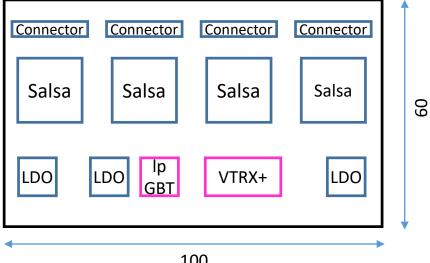

#### irfu cea 256-channel IpGBT-based FEB for CyMBaL : components

- Assuming 16 x 16 ball 1 mm pitch BGA package for Salsa

- Low profile 40-pin connectors for input signals over micro-coaxial cables

- Active components on both sides of the board

- Length and width give an idea

- Height of the board

- $\rightarrow$  Need to accommodate cooling

- $\rightarrow$  Need to include mechanical fixture for VTRX+ connector

- The fragile optical pigtail to be secured within the board

- On-board linear low dropout regulators

- Radiation-hard magnetic field tolerant DC/DC converters ۲

- $\rightarrow$  On a companion board

- $\rightarrow$  Count on common collaboration efforts

- Type, surface including air core, height, shielding, cooling

### 256-channel IpGBT-based FEB : power

- Raw power budget with minimal margin : ~6.8 W

- $\rightarrow$  27 mW / ch

- $\rightarrow$  1.5V 6.7 W

- $\rightarrow 2.8V 0.2W$

- Assume 8.5 W for safety : 25% extra

- $\rightarrow$  33 mW / ch

- $\rightarrow$  1.5 V 5.6 A

- $\rightarrow$  2.8 V 90 mA

- Where to place DC/DC converters ?

| FEB components and their power consumption |

|--------------------------------------------|

|--------------------------------------------|

| Component       | Vin<br>V | Current<br>mA | Power<br>mW | Comment                         |

|-----------------|----------|---------------|-------------|---------------------------------|

| Salsa 1         | 1.2      | 1 000         | 1 200       | 1 E m M/ch                      |

| Salsa 2         |          | 1 000         | 1 200       | 15 mW/ch                        |

| LDO Salsa 1-2   | 1.5      | 2 000         | 600         | Can use 2 LDOs to avoid hotspot |

| Salsa 3         | 1.2      | 1 000         | 1 200       | 1 E m M//ch                     |

| Salsa 4         |          | 1 000         | 1 200       | 15 mW/ch                        |

| LDO Salsa 3-4   | 1.5      | 2 000         | 600         | Can use 2 LDOs to avoid hotspot |

| IpGBT           | 1.2      | 420           | 500         | Probably 25% overestimated      |

| LDO lpGBT/VTRX+ | 1.5      | 440           | 130         |                                 |

| VTRX+           | 1.2      | 20            | 25          |                                 |

|                 | 2.5      | 70            | 175         |                                 |

| LDO VTRX+       | 2.8      | 70            | 20          |                                 |

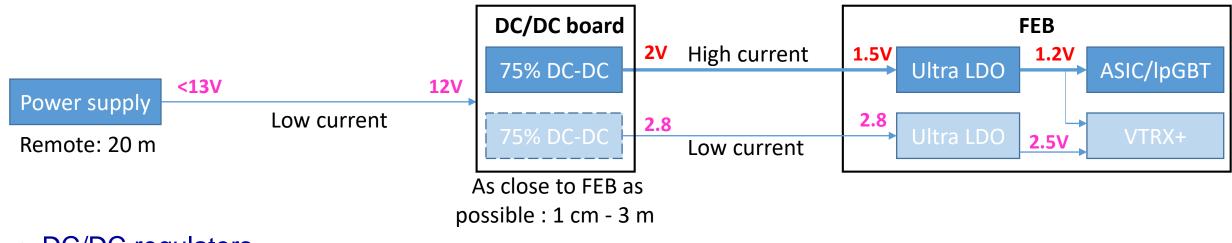

# **FEB power distribution example** Reminder : https://indico.bnl.gov/event/22316/contributions/87363/attachments/52727/90159/240215\_IM\_MpgdPower.pdf

- DC/DC-based LV distribution: to be magnetic field tolerant

- $\rightarrow$  Remote power supply distributes 12V with a low voltage drop over ~20 m cables

- Say less than 1V

- $\rightarrow$  Low cross-section power cables

- The lower the drop the lower the power dissipation in cables but the large is their cross-section

### DC/DC regulators

- $\rightarrow$  Might be bulky and a source of EMI

- Space + extra material for shielding

- $\rightarrow$  Distribute high current for 1.2V power

- Should be close to FEBs

- Avoid significant power drop and power dissipation in cables

- Avoid pickup noise and ground-loops

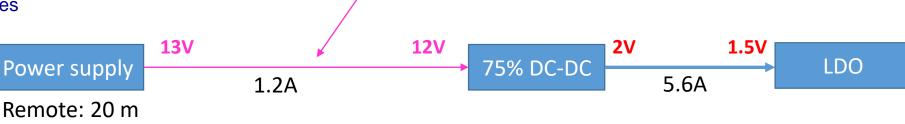

# LV cables from power supply to DC/DC regulators

- Assumptions:

- $\rightarrow$  Remote LV power supply 20 m away

- $\rightarrow$  1V voltage from between LVPS and DC/DC regulators

- 13V LVPS output voltage for 12V DC/DC input

- $\rightarrow$  75% DC/DC efficiency

- 1.2 A over LVPS cables

- LVPS power : 15 W / FEB

- $\rightarrow$  60 mW / channel

- Remember : 15 mW / channel for Salsa !

- $\rightarrow\,$  Power dissipation (loss) over LVPS cables : 1.2 W

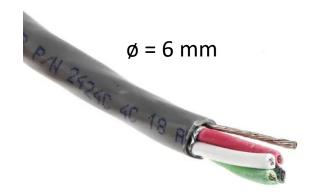

### LVPS cables cross-section 0.8 mm<sup>2</sup> or 18 AWG

- $\rightarrow\,$  Cable harness with two power cables and two sense wires

- $\rightarrow$  Alpha Wire 2424C : commercial harness including shield and coating : ø = 6 mm

- Reminder : there are 160 CyMBaL FEBs

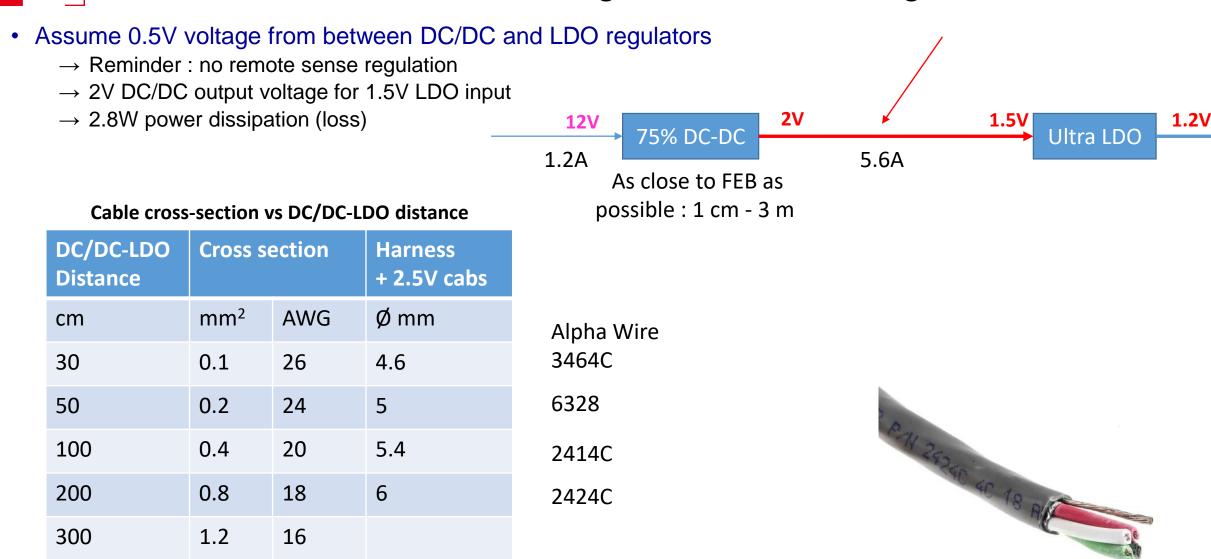

## LV cables from DC/DC regulators to LDO regulators

- Reminder : there are 640 MPGD FEBs with tailored power cable assemblies

- If possible, having DC/DC board next to FEB is preferred

irakli.mandjavidze@cea.fr

cea irfu

### Power components

- Studies within the ePIC collaboration to have common approach / solution to power the frontends

- $\rightarrow$  Magnetic field and mild radiation tolerant

- $\rightarrow$  Lead by Tim Camarda and Gerard Visser

- CERN power components

- $\rightarrow$  DC/DC regulators

- bPOL48

- bPOL12

- $\rightarrow$  Linear LDO regulator

- from CMS : high power for 1.2V Salsa and IpGBT

- Linear LDO regulator : low power LinPOL12 for 2.5V VTRX+

- $\rightarrow$  ePIC-wide and personal contacts : confirmation of availability in needed quantities

- MPGD needs

- 1 500 DC/DC regulators and possibly LinPOL12

- 3 000 CMS LDO

- But do we even need radiation tolerant components, can commercial components be used ?

- $\rightarrow$  e.g. MIC69303 (RT) linear regulator from Microchip

- $\rightarrow$  The PreTDR figures for radiation are extremely low : 0.4 krad after 10 years

- Magnetic field is a real issue

→ Saclay counts on ePIC-wide developments, final design and validation, on guidance for adaptation to our needs

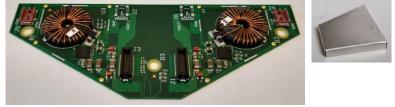

bPOL12V module prototype with custom coils and shield

© P. Aspell, CERN; S. Caregari, NSU Taiwan

### Frontend partitioning

### Height : ~10 mm

• Protect fragile VTRX+ and its pigtail by containing it within the FEB

Short pigtail / on board

Fibers of adapted length between patch panels

Short pigtail / on board

- → Common practice for commercial FireFly components in industry and VTRX predecessor in HEP community

- → Can limit pigtail length options to very few if not to 1 value : as small as farthest placement from front panel

- Potential to have a common pool of VTRX+ components for all subsystems

- $\rightarrow$  Easier maintenance

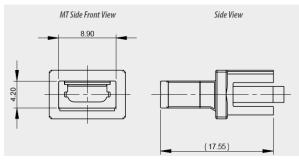

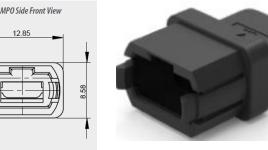

#### • MT-MPO low-profile adapter from Senko : 7P5-SM-1

$\rightarrow$  8.6 mm height

VTRX example

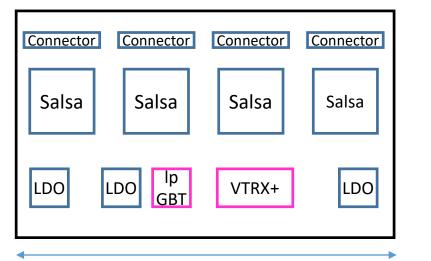

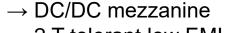

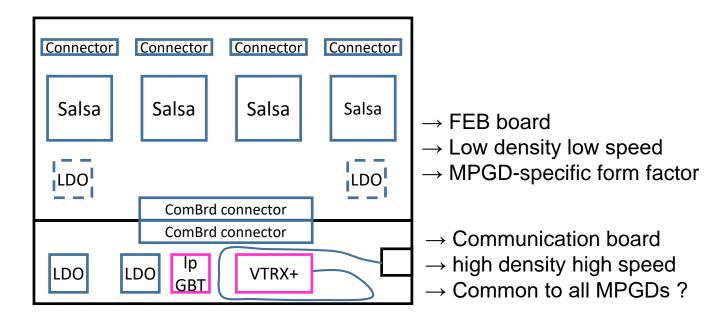

### <sup>222</sup> <sup>irfu</sup> Illustration of CyMBaL lpGBT-based FEB organization options

#### • Single board

100

- $\rightarrow$  Complex high density high speed

- $\rightarrow$  MPGD-specific form factor

- $\rightarrow$  2 T tolerant low EMI

- $\rightarrow$  Common to all MPGDs ?

60

Mezzanine approach

#### irfu Illustration of CyMBaL IpGBT-based FEB organization options cea

#### Single board

100

- $\rightarrow$  Complex high density high speed

- $\rightarrow$  MPGD-specific form factor

- DC/DC board whereabouts to be studied

#### Companion board approach

$\rightarrow$  board-to-board or board-to-cable (flex) connections

## <sup>222</sup> <sup>irfu</sup> Instead of summary : what could be done as work sharing?

- Readout architecture

- $\rightarrow\,$  Choice to be done : 2-stage IpGBT-based or 3-stage RDO-based

#### • FEB

- $\rightarrow$  Frontend electronics partitioning based on space constraints

- $\rightarrow\,$  FEB and communication board design

- Saclay has an expertise

- Low voltage powering

- $\rightarrow\,$  Common approach for low power distribution

- $\rightarrow$  DC/DC board design

- Saclay expects support from groups actively involved in powering studies

- Adaptation for MPGD

- Colling

- $\rightarrow\,$  No particular studies have been conducted at Saclay

- Only frontends have been discussed so far but there is much more

- $\rightarrow$  Backend (hardware), firmware and software adaptation

- $\rightarrow\,$  Run control, slow control and monitoring

- Consolidate readout specifications mostly concerns Salsa

- $\rightarrow\,$  Make sure they suit MPGD requirements

- $\rightarrow$  Make sure envisaged calibration and monitoring means are adequate

- $\rightarrow$  Timeline...

#### • Collaboration meeting at Frascati could be a good opportunity to discuss these questions ?

### Backup

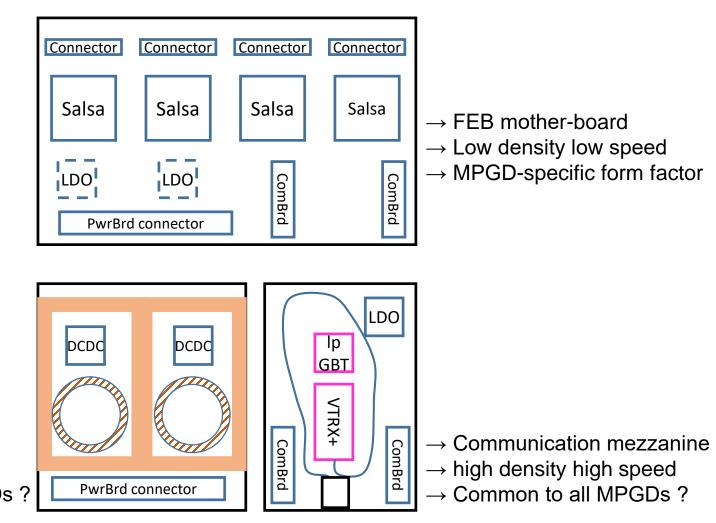

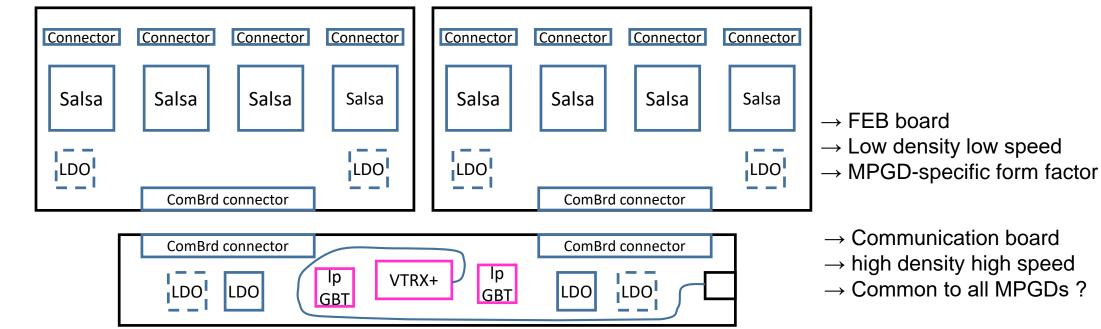

### <sup>222</sup> <sup>irfu</sup> Illustration of CyMBaL lpGBT-based FEB organization options

Shared communication board approach

- $\rightarrow$  Short board-to-cable (flex) connections

- Requires less VTRX+ components and fiber optic cables

- $\rightarrow$  2 VTRX+ optical outputs used

- $\rightarrow$  Need to understand if detector curvature permits

- DC/DC board whereabouts to be studied

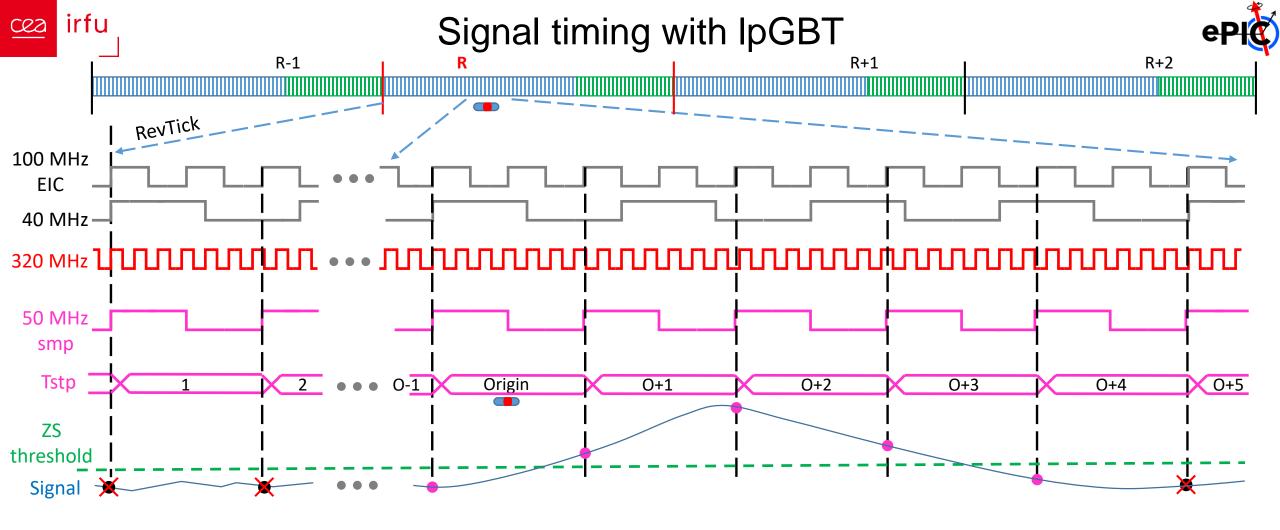

• Periodic "Sync" command generated when EIC and 40 MHz clocks are in phase

- $\rightarrow$  RevTick in this example

- $\rightarrow\,$  Allows phase alignment and monitoring of clocks within Salsa

#### • In this example Salsa is programmed to keep one sample before and after threshold crossing

$\rightarrow$  Salsa data for the signal : FrameCounter, Tstp(O-1) Smp(O-1) Smp(Origin) Smp(O+1) Smp(O+2) Smp(O+3)