# INTT various updates

## **National Central University/RIKEN**

### Dec 13th, 2024 INTT meeting

### Cheng-Wei Shih,

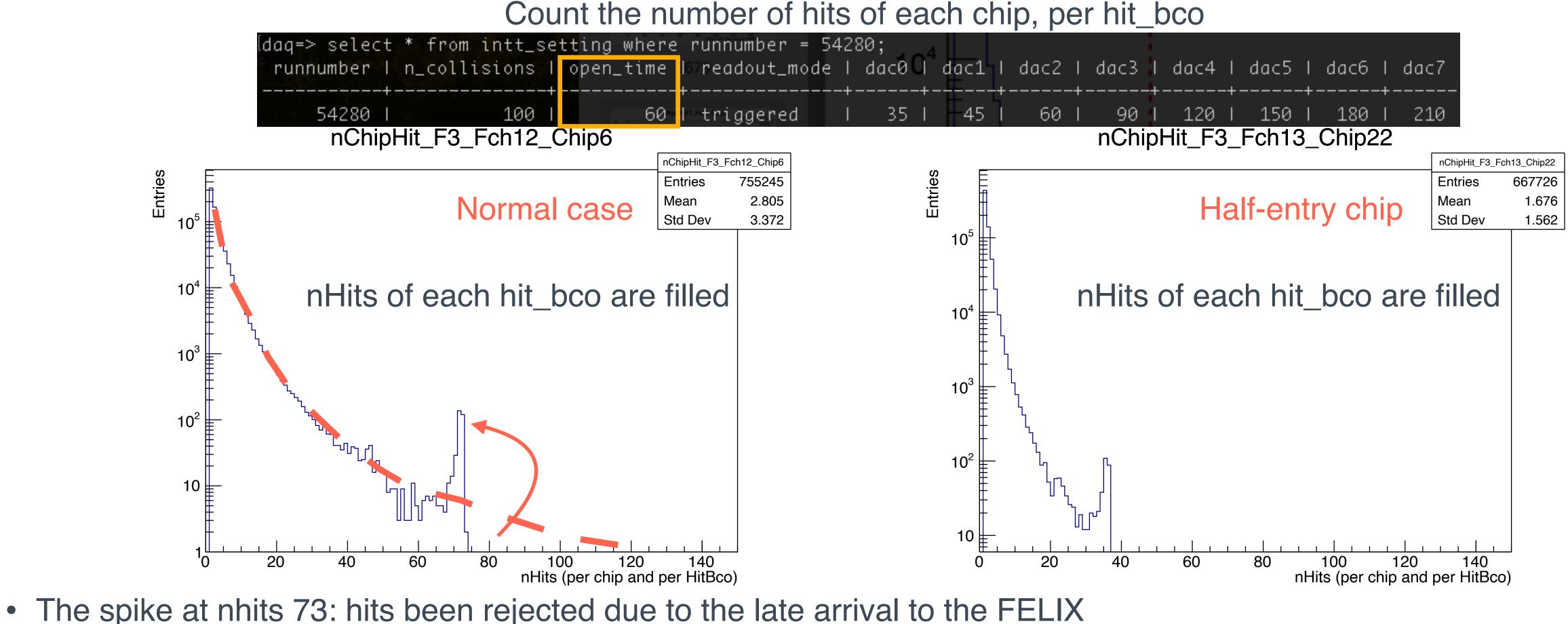

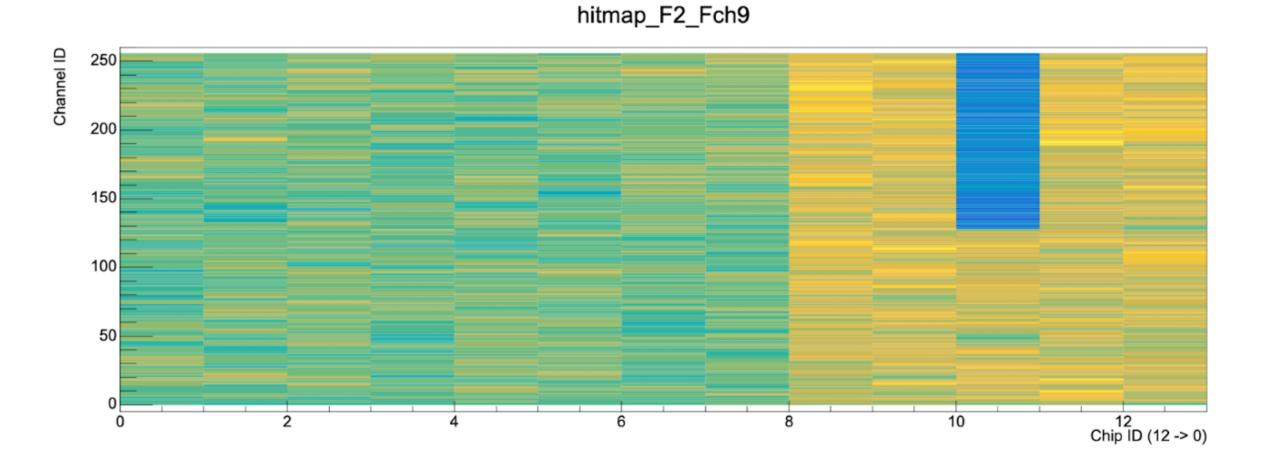

# Chip Occupancy

# With HitQA and CloneHit Removal (CloneHit: same FELIX, FELIX\_ch, chip\_id, chan\_id, hit\_bco)

In some extreme case, not all the hits are kept by the FELIX

- The maximal number of hits of each chip and per hit\_bco is 73

- Half-entry chips have similar structures  $\rightarrow$  Hit missing happened before FELIX (at chip)

INTT meeting

Cheng-Wei Shih (NCU, Taiwan)

Code can be found in GitHub

INTT has hit saturation issue

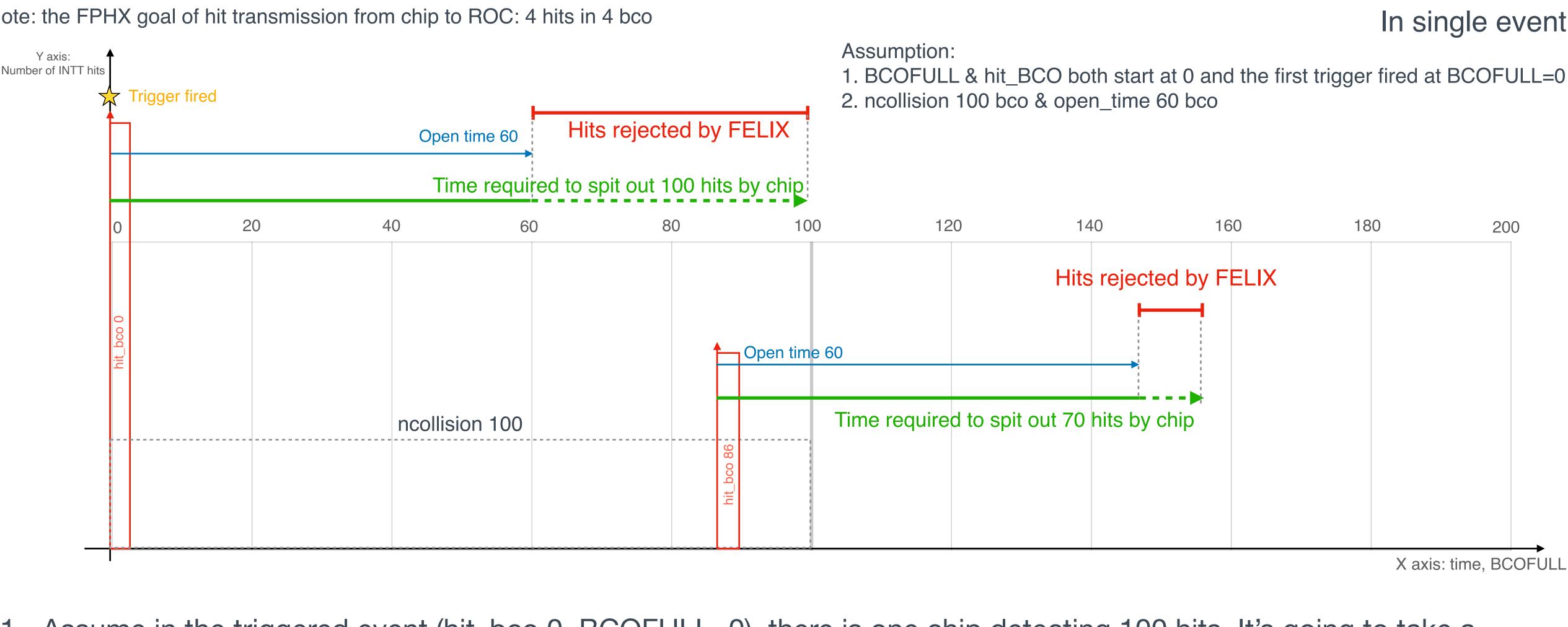

Note: the FPHX goal of hit transmission from chip to ROC: 4 hits in 4 bco

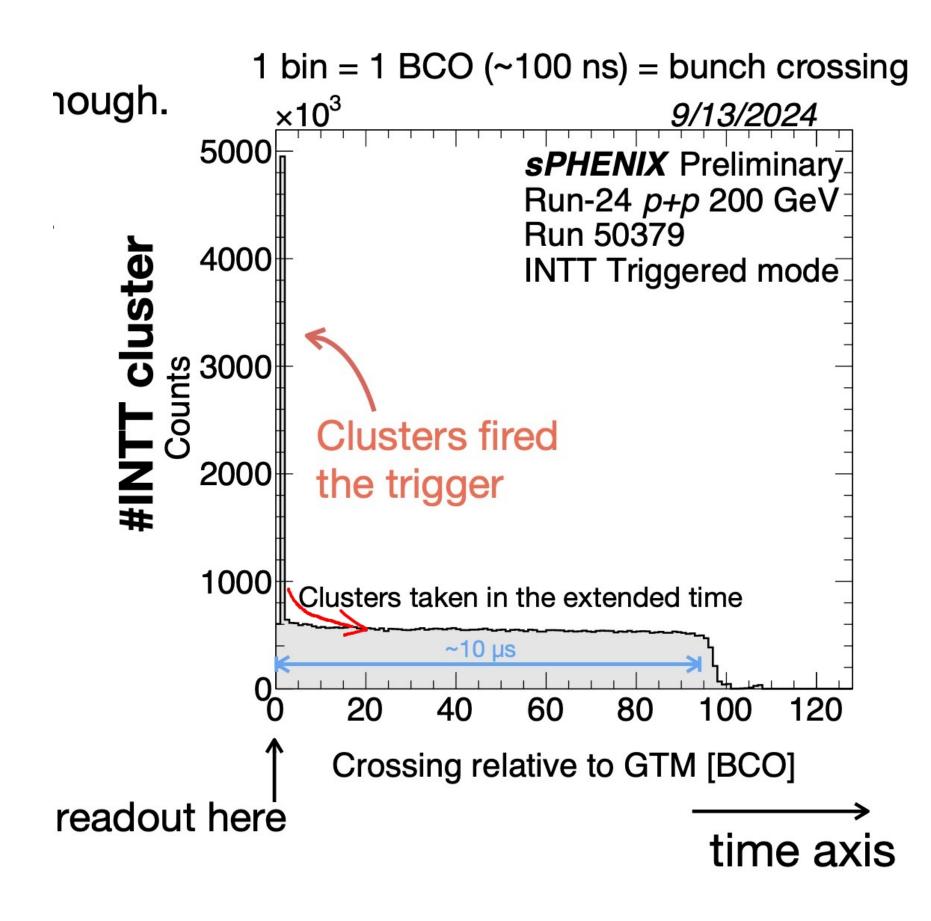

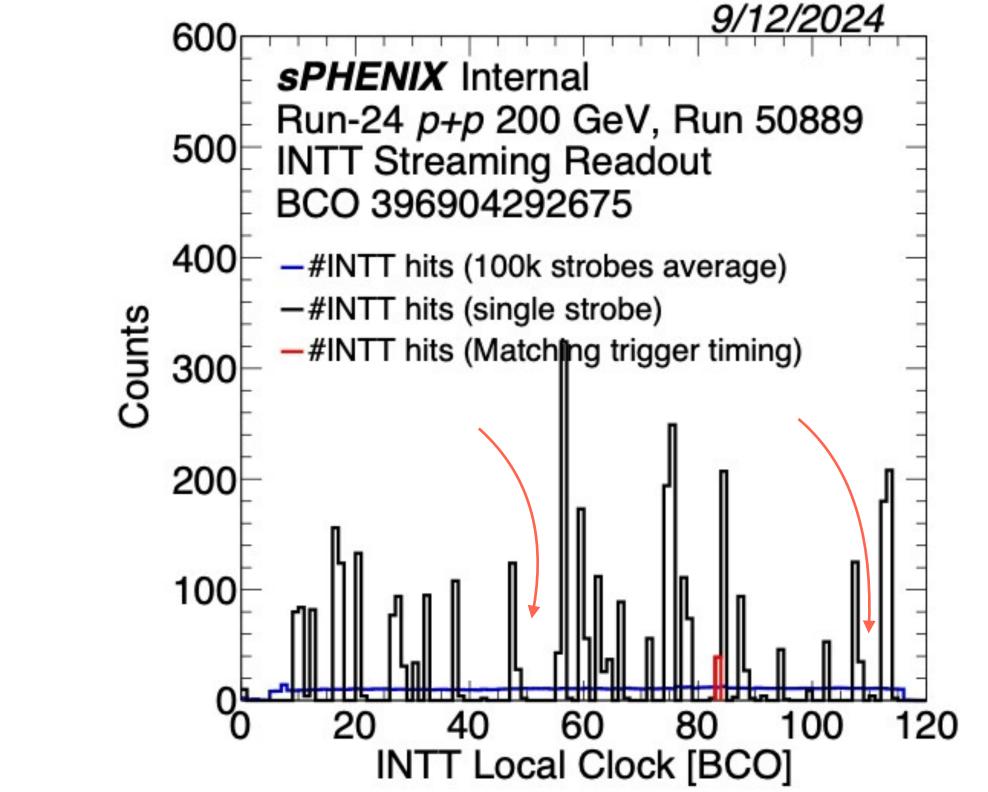

- period of time (~ 100 BCO) to send out all the hits

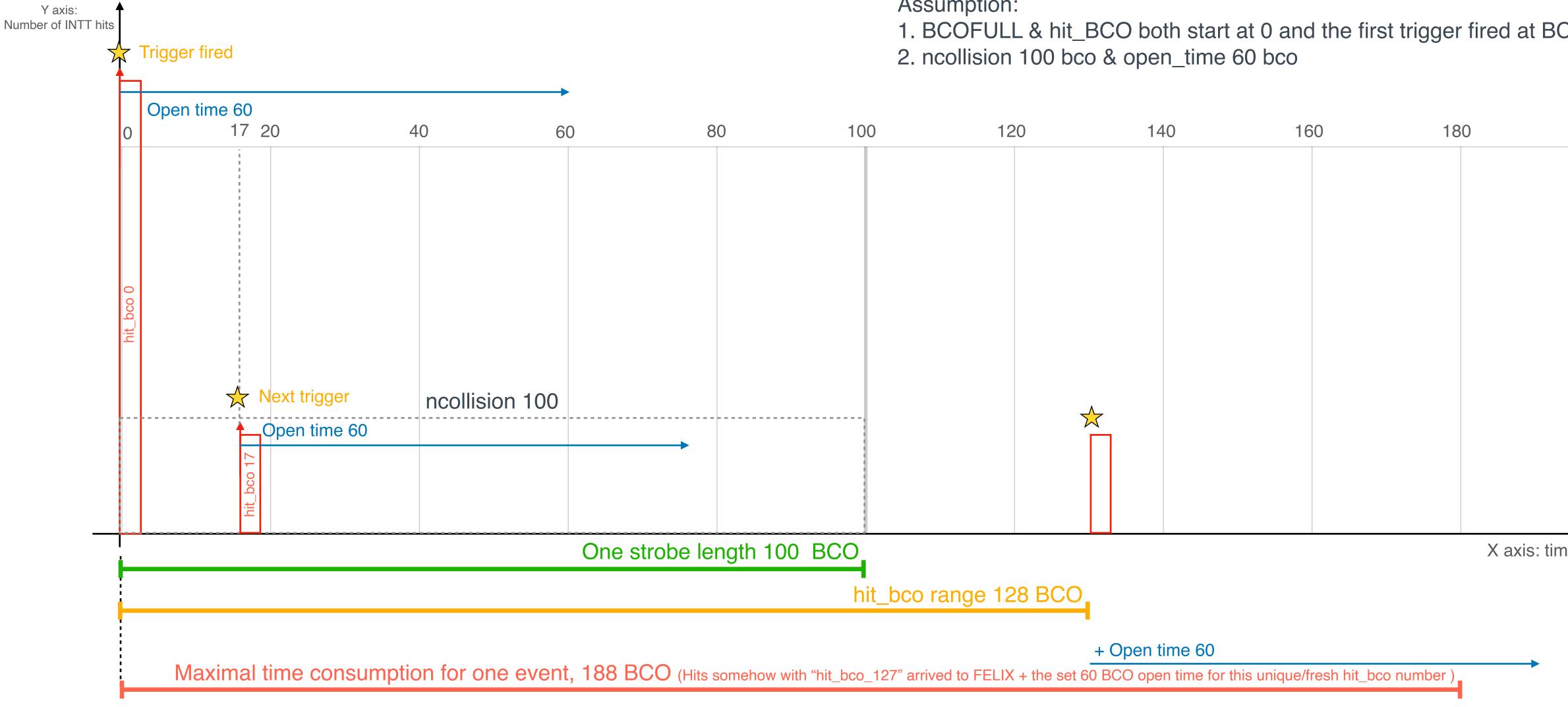

- 2. When FELIX detects the first hits with the "hit\_bco\_0", it's going to open a certain time window (controlled by open\_time) to accept the hits with "hit\_bco\_0", vice versa.

- 3. Assuming open\_time is 60. There will be  $\sim$  40 hits that cannot make it to arrive at the FELIX on time. They are therefore dropped by FELIX

1. Assume in the triggered event (hit\_bco 0, BCOFULL=0), there is one chip detecting 100 hits. It's going to take a

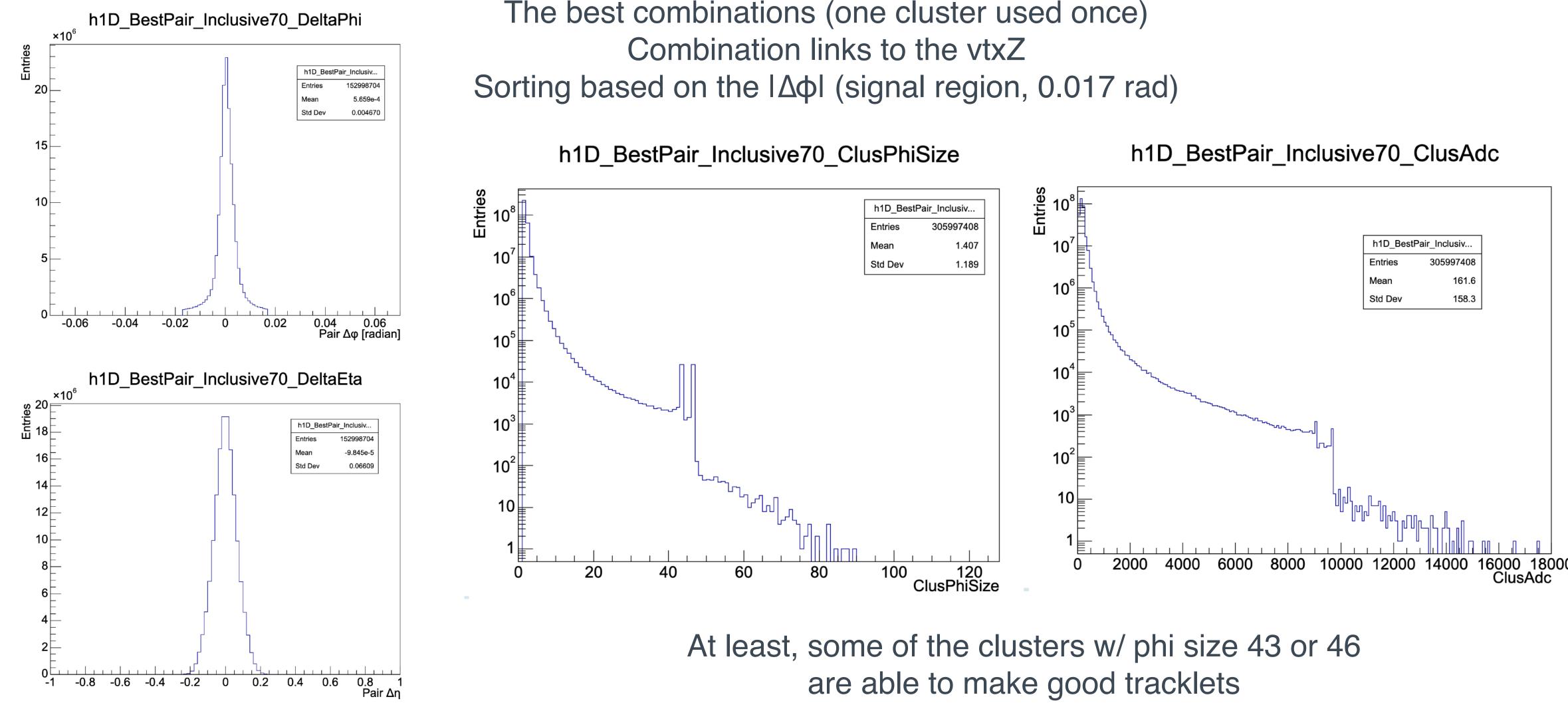

# The behaviors of the used clusters

### -2 cm < MBDz - INTTz < 3 cm && Centrality 0-70%

**INTT** meeting

Cheng-Wei Shih (NCU, Taiwan)

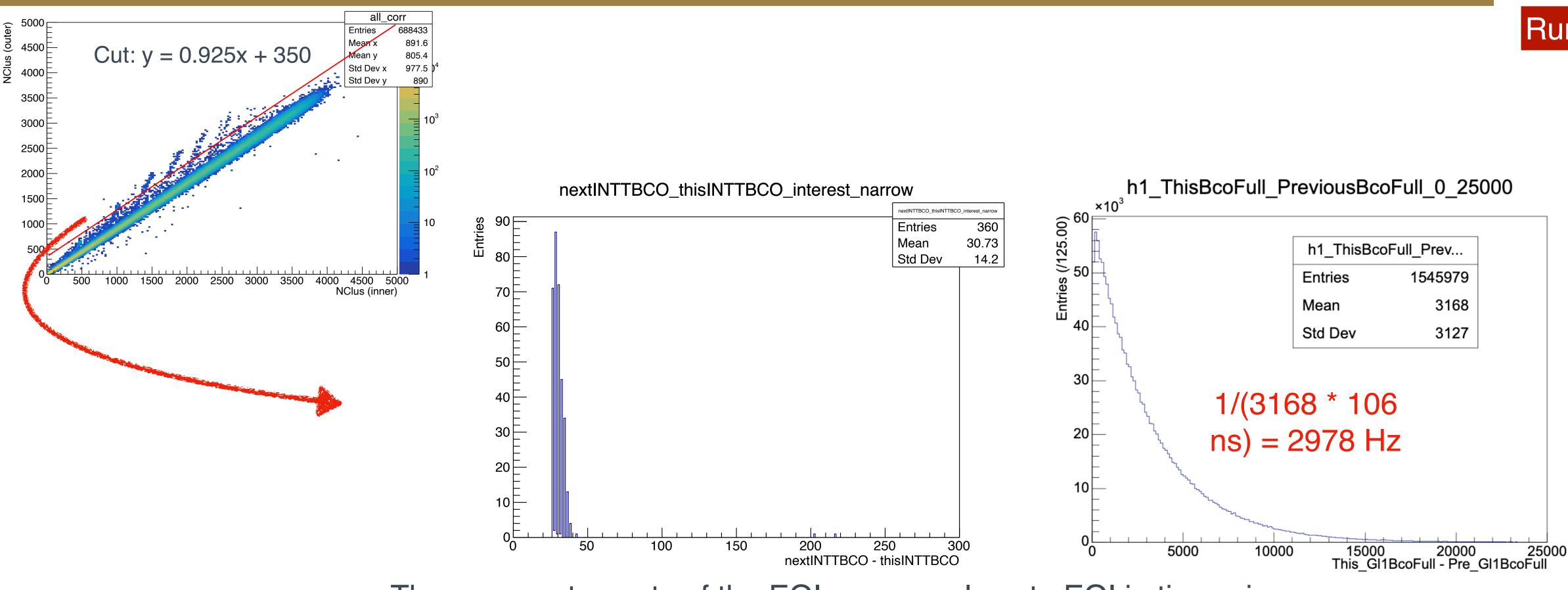

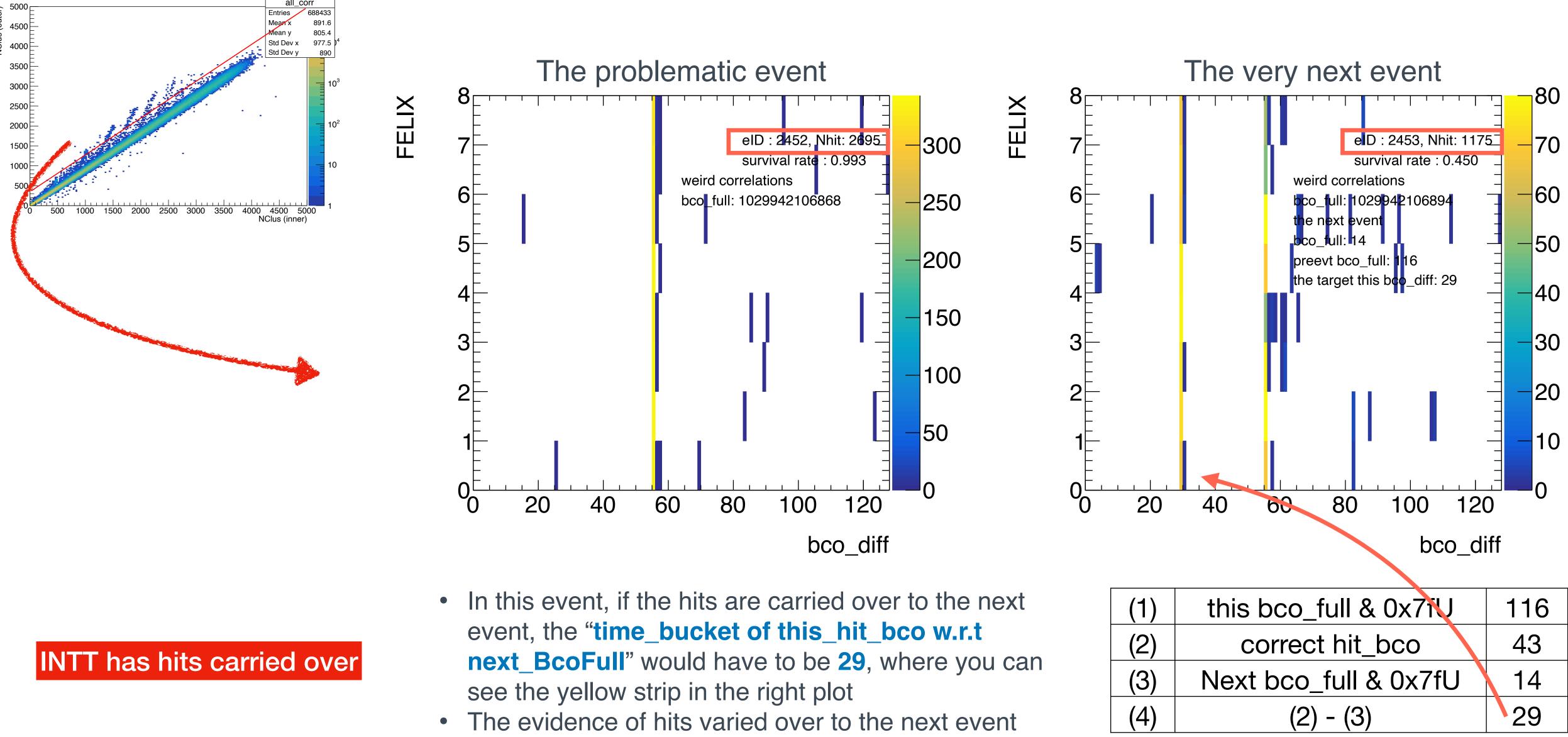

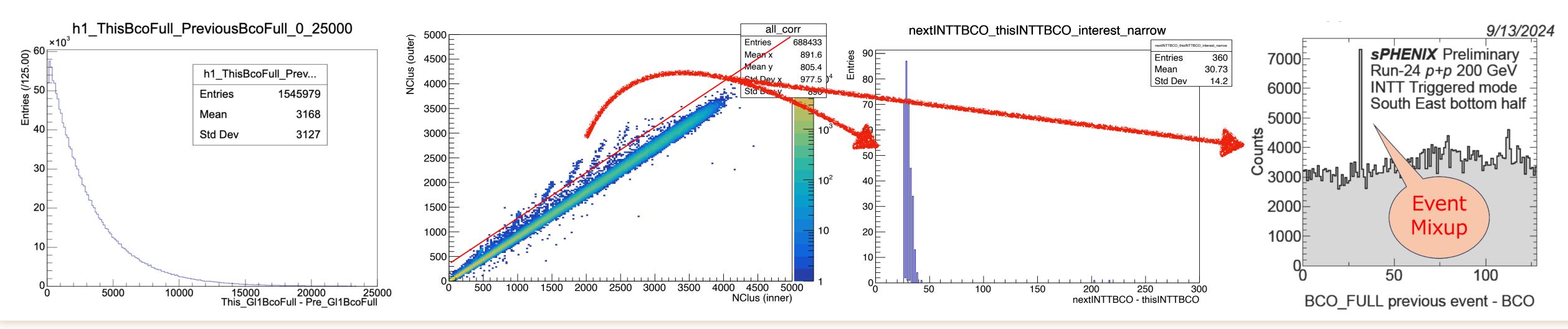

# Hit carried over issue

The very next events of the EOI are very close to EOI in time wise

Hypothesis: Hits in FELIX been assembled with INTTheader (INTT\_bcofull) and sent out to the down stream. Since FELIX receives new trigger, the previous INTT\_bcofull is overwritten. The hit assembly continues, but with the new INTT\_bcofull

INTT meeting

```

Can we probably just have a simple "BCOFULL_diff" cut?

```

```

Cheng-Wei Shih (NCU, Taiwan)

```

# Hit carried over issue

SPHE

Note: the FPHX goal of hit transmission from chip to ROC: 4 hits in 4 bco

- BCOs. Raul will check what will happen if next trigger conflicts with FELIX open\_time

- The current explanation might not be applicable on the Run23 data, needed to be answered

Assumption:

- 1. BCOFULL & hit\_BCO both start at 0 and the first trigger fired at BC

## According to Raul, he didn't expect that the next trigger would be sent to subsystems within ~2

Cheng-Wei Shih (NCU/RIKEN)

| COFULL=0    |

|-------------|

| 200         |

|             |

|             |

|             |

|             |

|             |

| ne, BCOFULL |

|             |

| 200         |

|             |

|             |

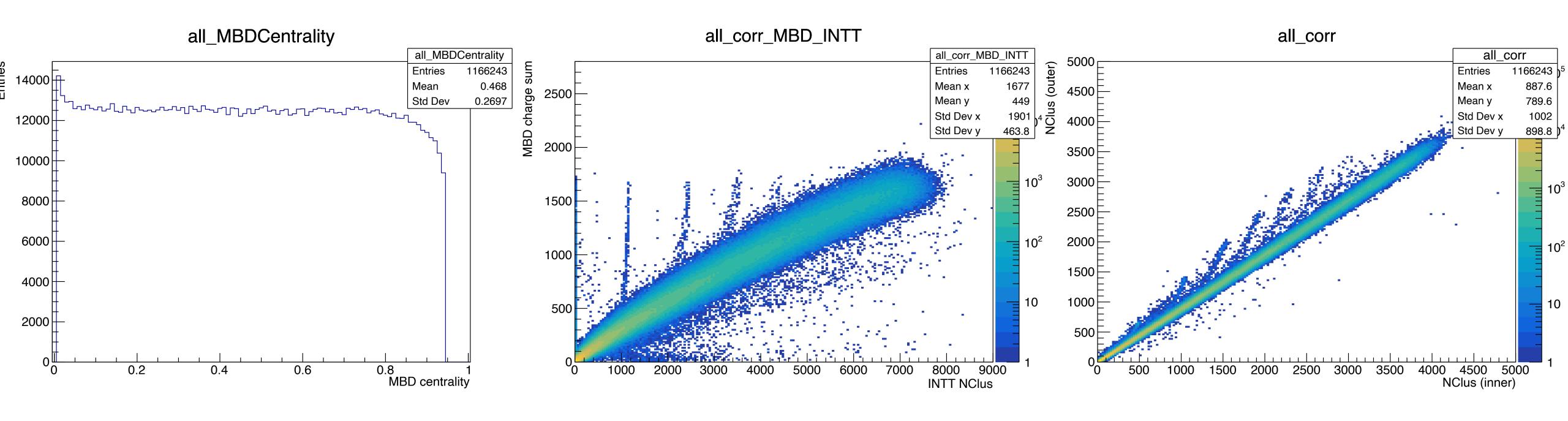

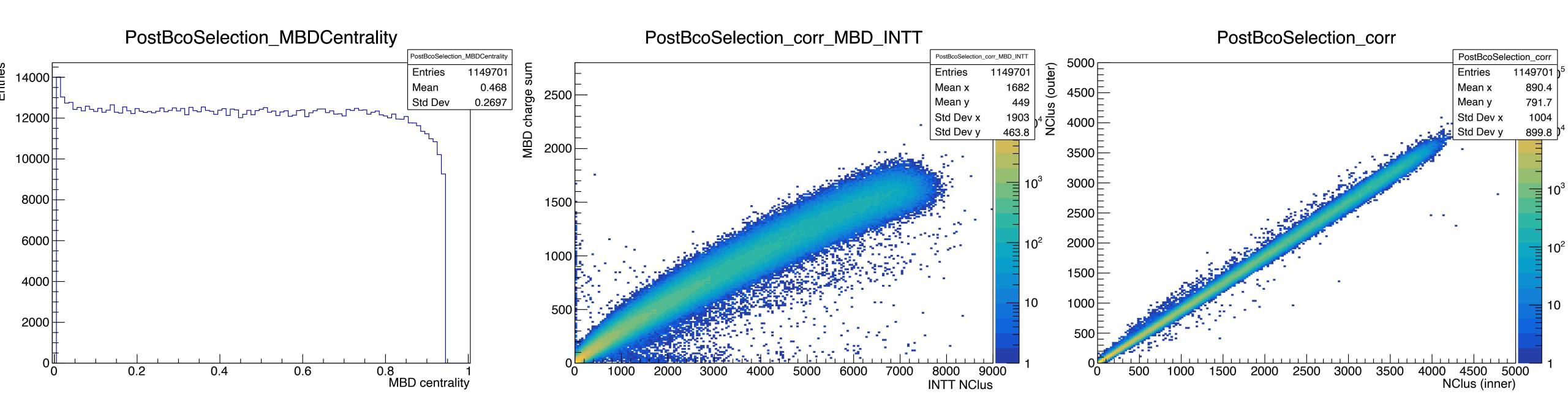

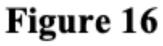

## Selection on the event BCO spacing

INTT meeting

### Only evens with -10 cm < MBD\_z\_vtx < 10 cm are included

## Selection on the event BCO spacing

### Only evens with -10 cm < MBD\_z\_vtx < 10 cm are included Events w/ NextInttBcoFull - ThisInttBcoFull > 61 are kept

16,542 out of 1,166,243 events are excluded  $\rightarrow$  1.42%

Cheng-Wei Shih (NCU, Taiwan)

INTT meeting

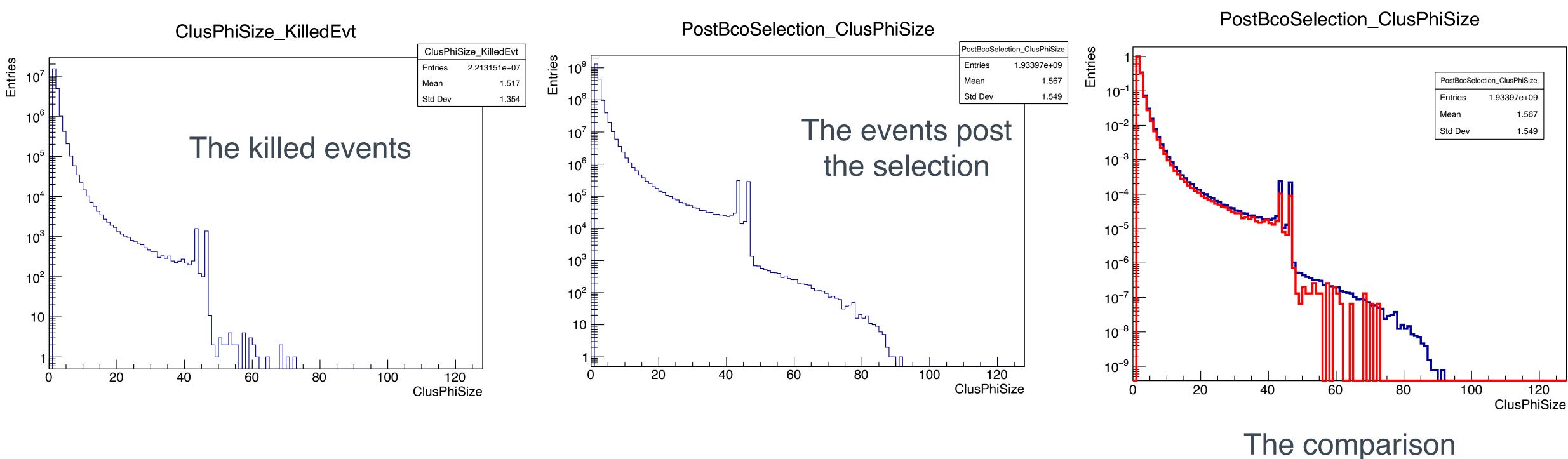

# cluster phi size distributions

### Only evens with -10 cm < MBD\_z\_vtx < 10 cm are included Events w/ NextInttBcoFull - ThisInttBcoFull > 61 are kept

INTT meeting

Cheng-Wei Shih (NCU, Taiwan)

(normalized by the first bin)

### Don't get confused, the hit carried over issue is independent to the hit saturation issue

# What are the plans for Run 2025?

- Hit Saturation issue

- Increase the open\_time to the maximum (128 BCOs)

- Need to check the chip/ROC overflow flag and other runs in run24 AuAu

- Do the open\_time scan in Run25 if possible

- Hit carried over issue

- Proposed the hard-coded busy (say 200 BCOs)...? (Trigger rate reduction)

- See the following slides

- Dynamic busy implementation in the FELIX...? (Trigger rate reduction)

- Might be better, but need to have the firmware update

- How to proceed? Rachid  $\rightarrow$  BNL  $\rightarrow$  Instrumentation department  $\rightarrow$  RIKEN? (2 months process?)

- Note: <u>Carnival Festival: Feb. 28th to Mar. 8th, 2025</u>

- First collision: Mar 24th 2025

- etc.)

- Can be done in parallel

- Or any other ideas other than these two...?

- different from our needs. And TPC/MVTX can already handle the hit-carried-over issue (it's happening)

INTT meeting

Cheng-Wei Shih (NCU, Taiwan)

- In either cases, we need to inform and get the approval from the operation board people (Rosi, Kin, John, JaeBeom,

• Note: the dynamic busy for TPC is the implementation on the buffer boxes as TPC sends too much data there. It's

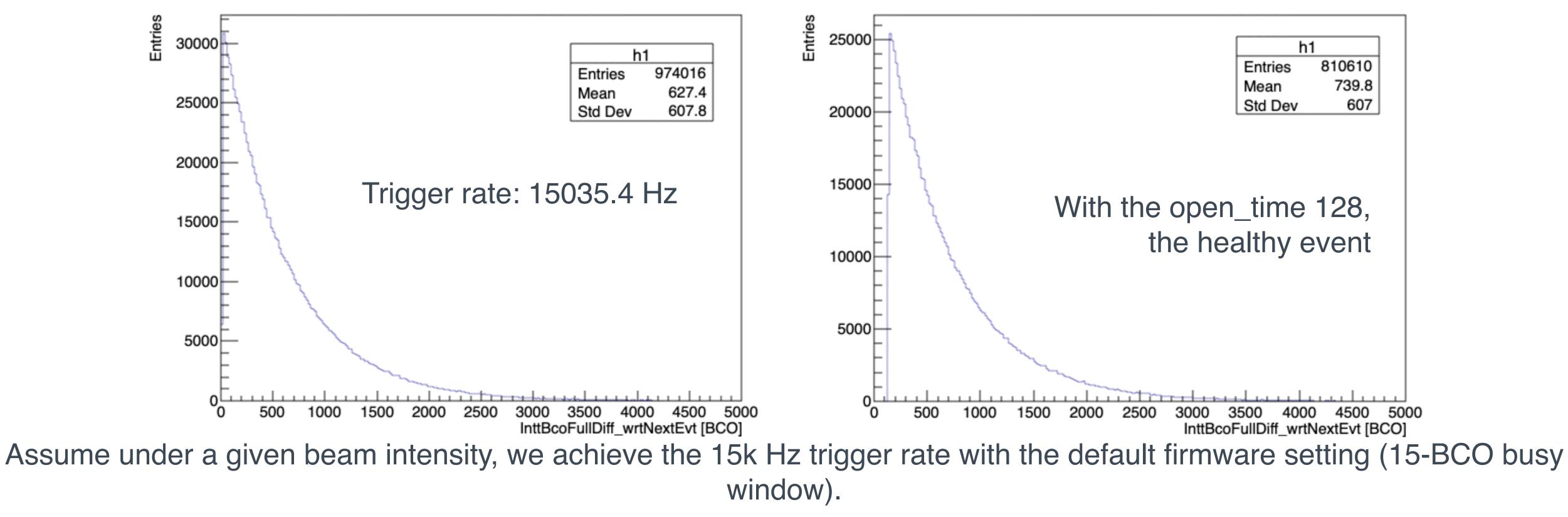

## The plan for Run 2025

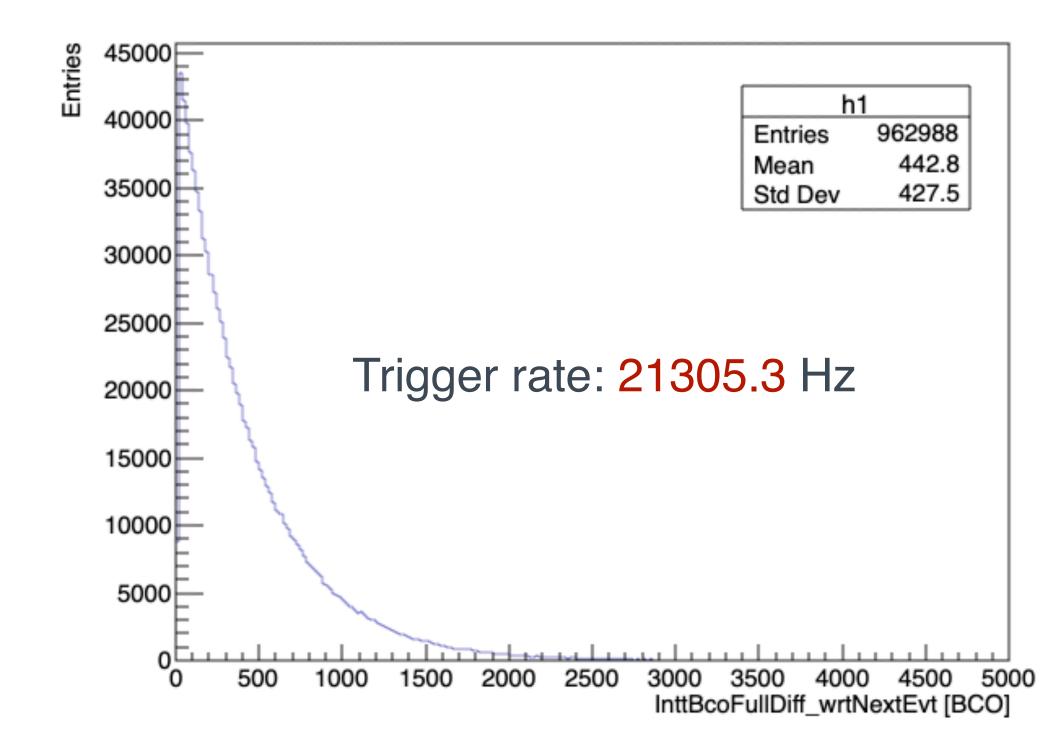

If we do nothing but just to increase the open time to maximal to mitigate the hit saturation Under the same beam intensity and scale\_down (same random generator, `TMath::Exp(-0.00163\*x)`)

With the current hard-coded 15 BCO busy

The events with InttBcoFullDiff\_wrtNextEvt > 128 BCOs is (974016-810610)/974016 = 16.8% of events can have the hitscarried-over issue

Cheng-Wei Shih (NCU, Taiwan)

INTT meeting

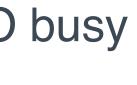

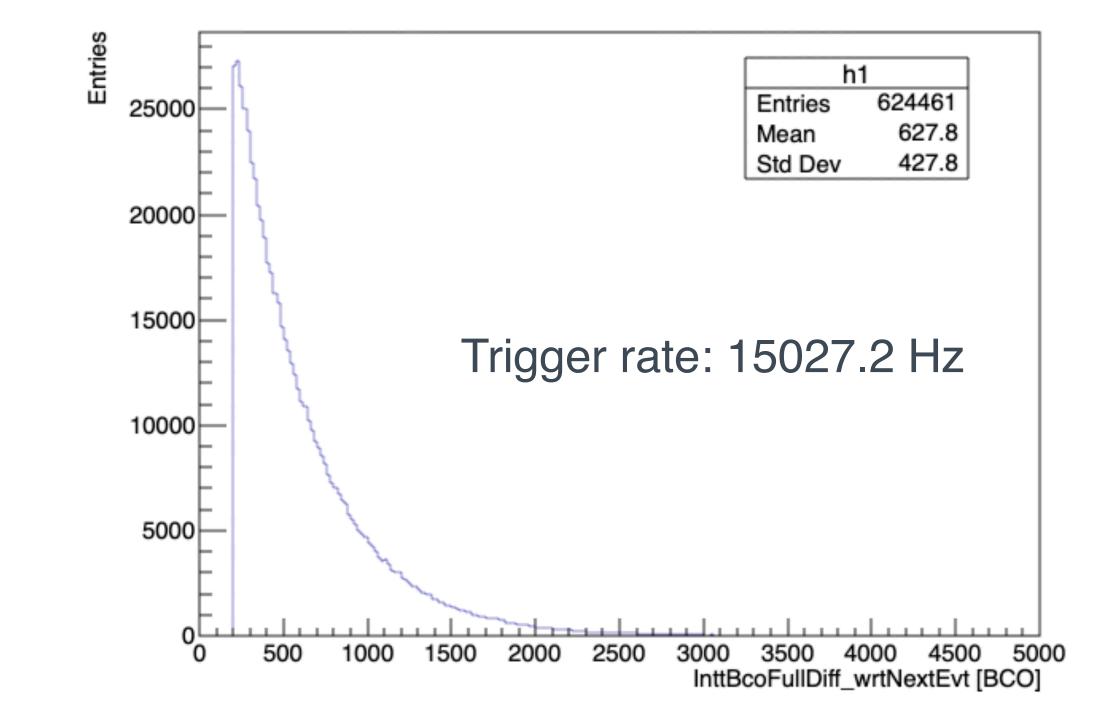

## The plan for Run 2025

If we propose to the sPHENIX to increase the hard coded GTM busy window from 15 BCOs  $\rightarrow$  200 BCOs Under the same beam intensity and scale\_down (same random generator, `TMath::Exp(-0.00163\*x)`)

With current hard-coded 15 BCO busy

Assume under a given beam intensity, we achieve the 15k Hz trigger rate with the default firmware setting (15-BCO busy window), if now we change the busy window to [200 BCO], the trigger rate drops to 11.6k Hz.

Cheng-Wei Shih (NCU, Taiwan)

#### With hard-coded 200 BCO busy

Additional 253,426 of events are killed  $\rightarrow$  26%

## The plan for Run 2025

If we propose to the sPHENIX to increase the hard coded GTM busy window from 15 BCOs  $\rightarrow$  200 BCOs

With the current hard-coded 15 BCO busy

To make the case with the busy window 200 BCO achieve 15k Hz, we will need to have the [beam\_intensity x scale\_down] 1.42 times higher. Scale\_down factor is already zero → Need beam intensity increased 1.42 times higher

INTT meeting

#### With hard-coded 200 BCO busy

# One more thing we should do before Run25 SPHENX

- A long standing question (1+ year), what caused the hit-carried-over issue in Run23?

- I hope it can be explained by the same hypothesis we came up with Run24 AuAu

- If it's not the case, it's more worrisome

- We need to

- 1. Pick up the single run in run23 with evident hit-carried-over issue

- 2. Check the event bco spacing distribution of that run

- What is the fraction of events with event bco spacings within 50 BCOs?

- 3. Plot the internal multiplicity correlation, inner-outer NClus (Nhits?)

- 1. Come up with a cut for selecting the outliers

- 2. Plot the 1. event-bco-spacing distribution and dist. of {pre\_bcofull hit\_bco}

#### INTT meeting

This is for the hit-carried-over issue

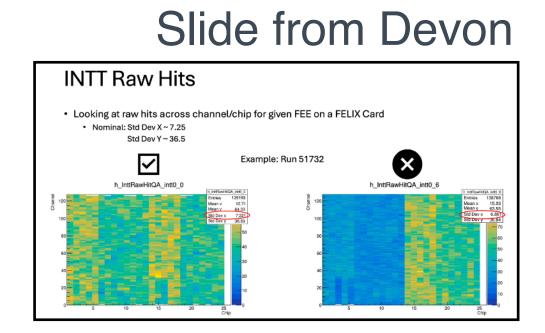

# The requests from the tracking group

- Representative(s) in the <u>daily</u> tracking meeting - Multiple people share the load? Joseph, Takashi, Cheng-Wei, Jaein and more?

- The good run list (streaming runs especially, their targets for QM25) - Devon Loomis is working on the INTT good run list [indico link]

- - Luckily I called in yesterday

- Due to ~zero communication b/w tracking group and INTT group?

- I have talked to Devon, probably Jaein can contact him and report in the tracking meeting

- The hit-carried-over issue for the p+p runs

- Streaming runs first and the triggered+extended runs - How to check the streaming data? Reconstruct the trigger bco\_full first?

**66** INTT group will check the data to confirm it.

Great. That is VERY important for any Run24 analysis. Please do and give a presentation in the O2O meetings.

- General comment, we need to be more active in the tracking meeting...

- Cheng-Wei Shih (NCU, Taiwan)

# Quantify the hits moved to the next bin...?

The timing resolution of INTT is limited by the performance FPHX chip What important here is to understand the fraction of the hits moved to the next bco due to the imperfect coarse/fine delay settings

Another input to the tracking group?

Cheng-Wei Shih (NCU, Taiwan)

# Quantify chip timing stability?

### INTT timing reliability chip by chip

It's discovered that it is actually possible that some INTT chips could have timing been off during the data taking

If the hot channel mask algorithm is done without the bco\_diff cut in the first place, such problem can not be revealed

INTT meeting

#### Another input to the tracking group?

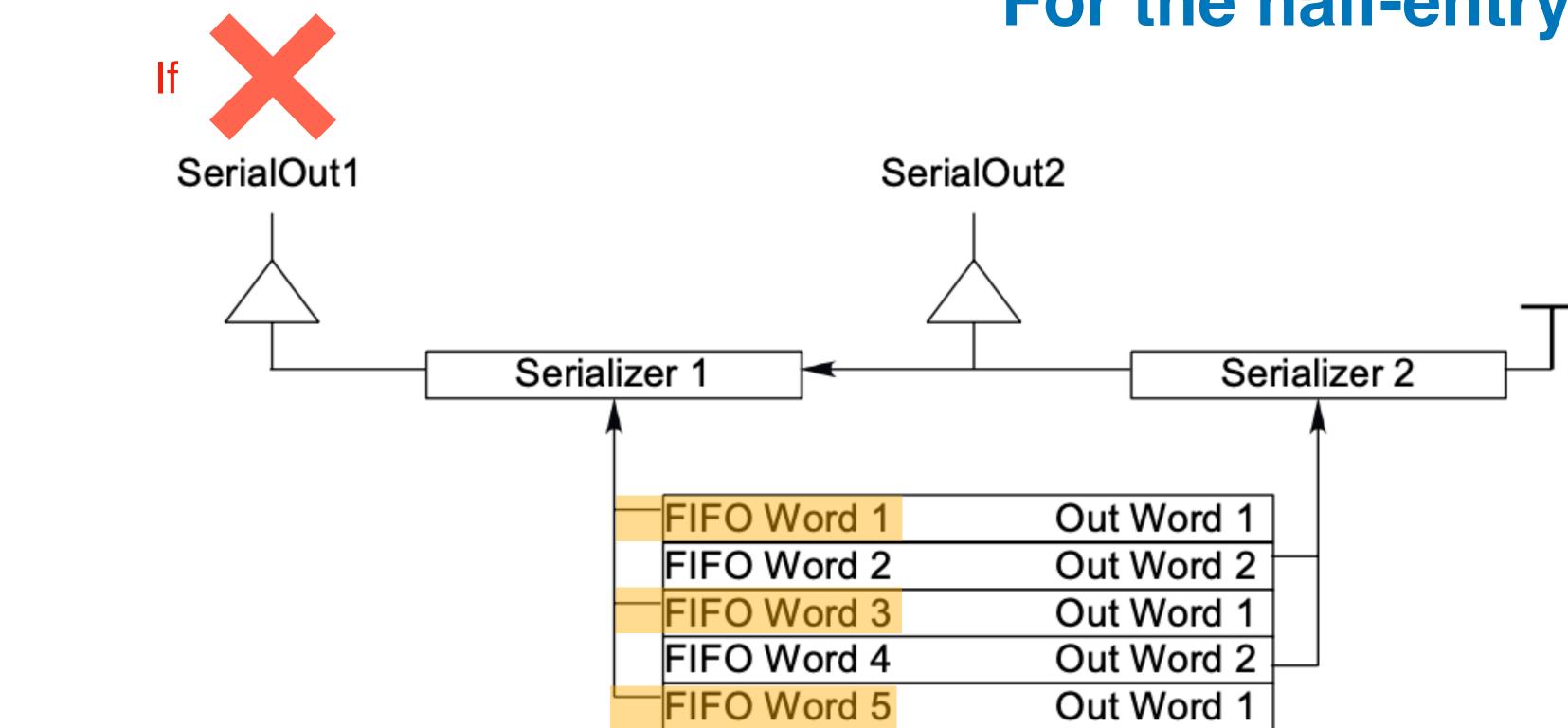

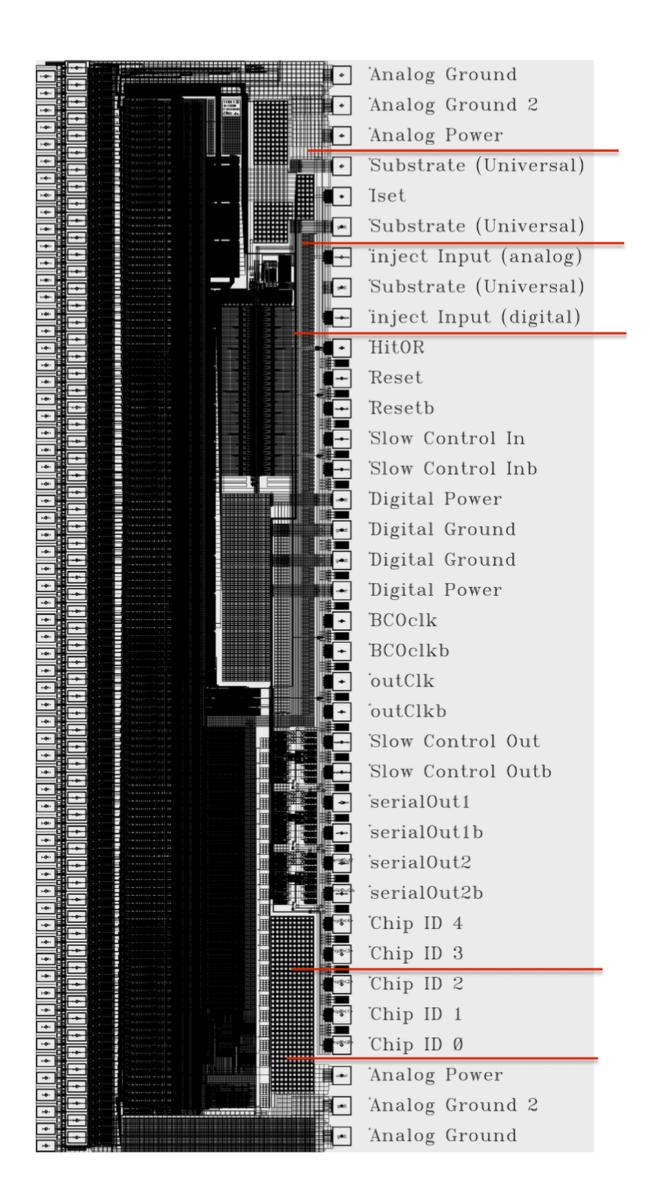

# FPHX chip, serializers

If it's SerialOut1 dead, there is no hope to recover the half-entry chip by changing the `Digital Control setting`

INTT meeting

Cheng-Wei Shih (NCU, Taiwan)

### For the half-entry chip recovery

#### **Figure 16 - The Serializers**

# The open questions of INTT

- Fraction of hits moved to next of BCO bin (Due to the imperfect coarse/fine delay) INTT chip timing stability (the chip timing can shift, is it a severe issue ?) Coarse delay scan practice (Have some data with different coarse-delay settings aiming at improving the INTT timing resolution, we will need to practice it for the run 2025

- preparation)

- INTT good run list (streaming first, then triggered for p+p) INTT hit-carried-over issue (in AuAu and p+p, and mitigation strategy) Threshold setting of run 2025 (the current one underestiamtes real spectrum)

- Hit saturation in Run 2025

- Calibration data analysis (artificial charge injection to chips)

- The discrenapcy between data and MC (Simulation optimization)

- **INTT** radiation damage

- **INTT** geometry optimization

- (Sort like closed)

- Spikes at 43 and 46 of cluster phi size distribution Ο

- hit saturation issue Ο

<u>Google doc link</u>

## Summary

- INTT has the issues of hit saturation and hit carried over

- The two issues are more like independent

- We need to have the strategy for the run 25

- We also need to check the Run23 data to solid our understanding based on Run24

- We have few requests from the tracking group

- Representatives

- Good run list {streaming runs}

- Check hit carried over issue of streaming (and triggered) p+p runs Need to be active in the tracking meeting

- We still have several open questions, and some of them could be very important but not yet have people looking into

SPHE

Back up

## The landau-Gaussian convolution for edep dist. fit SPHENIX

• 3 materials relevant to the Landau-Gaussian-convolution function fit on the energy deposit distribution in the google drive

> However, the effects of atomic binding of the electrons have been disregarded in both the Landau and Vavilov theories. The theories can be improved by using a modified cross section to take into account the electron binding energy.<sup>13</sup> The modified energy-loss distributions can be expressed as the convolution of a Gaussian function with a Landau or Vavilov distribution, respectively.<sup>8,10,14</sup> Thus  $\int_{-\infty}^{+\infty} f_{L,V}(\Delta',x)$

$$f(\Delta,x)=(1/\sigma\sqrt{2\pi})\int$$

The reason why people used the Landau-Gaussian-convolution function for fitting the edep distribution instead of pure single Landau function is to address the "effect of atomic binding of the electrons", as stated in the paper.

$$\times \exp[-(\Delta - \Delta')^2/2\sigma^2]d\Delta',$$

(3)

# Higher beam background in Run25

GY

MC

#### Glenn Young 對所有人說 上午 2:31

how thick is the absorber, in terms of interaction lengths? Less than around 2 interaction lengths will increase the number of hadrons coming out relative ot the number going in i.e. a hadron amplifier. I.e. how damped-down is the hadron shower that the stray beam particle creates?

#### Mickey Chiu 對所有人說 上午 2:33

I think one of the absorbers being considered is 120 cm polyethylene, which is about 1.36 int. lengths.

As JH mentioned, for the MVTX this works anyway since even though there are more particles, they get scattered around enough. Other detectors will likely see an increase in backgrounds.

I'm looking into the implications for the MBD, and the troublesome thing is an increase of secondaries from the au+au collisions. The number of int. lengths in front of the MBD increases from ~0.1 to 1.0 at the most forward angles.

#### INTT meeting

#### Cheng-Wei Shih (NCU, Taiwan)

#### SPHE

# BNL housing for run 2025

Dear sPHENIXers,

I know everyone is worried about their travel budgets, but the success of Run 25 depends on having folks at BNL, not only for shifts but to serve as detector experts and other key personnel! To help with this, especially given the uncertainty in the length of the run, we would like to coordinate housing arrangements to use everyone's travel budgets efficiently. First, there are some **funds available** to help cover housing costs at BNL. These funds are limited and will be distributed on a **first-come**, **first-served basis**.

Please note that these funds can only be used to support the housing costs of individuals who are: US Citizens, Green Card Holders or B1/H1B Visa Holders. To request funding, please email me (<u>rosijreed@lehigh.edu</u>) and Peter Steinberg (<u>steinberg@bnl.gov</u>) with your request for funding.

If you want to request an apartment for your group, please email Christine Nattrass (cnattras@utk.edu) and me (rosijreed@lehigh.edu) with the number of bedrooms you need and the potential arrival/departure dates for your group.

With shift sign-up starting **January 6**, you should soon be able to determine when your personnel will be needed at Brookhaven for shifts, but many folks should already know due to their expert requirement. We have created a Google Sheet for individuals to input their specific details. Even if a group apartment is requested, have folks fill this out so we can coordinate.

Please submit all housing requests for spring and summer stays by **January 31st**. Earlier requests are strongly encouraged, particularly for summer requests, as housing tends to fill up quickly. We will assist with fall housing coordination as well, though those arrangements can be made later.

Note that apartments are \$47, \$36, or \$29 per day (per bedroom) for 2, 3, 4 bedroom apartments at the monthly rate compared to the dorms at \$68 per day, so we can really conserve people's budgets if we work together.

So for example, if group A has 2 shifters that will spend 2 weeks at BNL and group B has 2 shifters that will spend the following 2 weeks at BNL if they share a 2 bedroom, the cost would be \$1407 per group, instead of \$2040 per group if the shifters stayed in the dorms. Housing is willing to split receipts, though we want to minimize the number of different receipts per apartment so try to coordinate within your group.

If you have any questions, please don't hesitate to reach out.

Cheng-Wei Shih (NCU, Taiwan)

### We need to take the action as soon as possible

## Apple-to-apple comparison?

- High rate run in run 23 AuAu?

- different

- And see the behavior the fish-bone?

| runnumber | runtype | brtimestamp         | ertimestamp         | updatetimestamp | eventsinrun | marked_invalid | has_comment | qcomment | trigger_rate           | round                                  |

|-----------|---------|---------------------|---------------------|-----------------|-------------|----------------|-------------|----------|------------------------|----------------------------------------|

| 23901     | beam    | 2023-07-27 00:38:16 | 2023-07-27 00:38:53 |                 | 26994       | -1             | 0           |          | 729.5675675675675676   | 0.617                                  |

| 23902     | beam    | 2023-07-27 00:41:06 | 2023-07-27 00:42:07 |                 | 54046       | -1             | 0           |          | 886.00000000000000000  | 1.017                                  |

| 23903     | beam    | 2023-07-27 01:08:11 | 2023-07-27 01:09:05 |                 | 42592       | -1             | 0           |          | 788.7407407407407407   | 0.900                                  |

| 23904     | beam    | 2023-07-27 01:11:15 | 2023-07-27 01:12:20 |                 | 92495       | -1             | 0           |          | 1423.00000000000000000 | 1.083                                  |

| 23905     | beam    | 2023-07-27 01:21:15 | 2023-07-27 01:26:27 |                 | 968137      | -1             | 0           |          | 3103.0032051282051282  | 5.200                                  |

| 23906     | beam    | 2023-07-27 01:30:31 | 2023-07-27 01:36:51 |                 | 1147432     | -1             | 0           |          | 3019.5578947368421053  | 6.333                                  |

| 23907     | beam    | 2023-07-27 01:40:36 | 2023-07-27 01:46:59 |                 | 1172162     | -1             | 0           |          | 3060.4751958224543081  | 6.383                                  |

| 23910     | beam    | 2023-07-27 04:02:20 | 2023-07-27 04:04:06 |                 | 50472       | -1             | 0           |          | 476.1509433962264151   | 1.767                                  |

| 23911     | beam    | 2023-07-27 04:06:59 | 2023-07-27 04:13:01 |                 | 1232167     | -1             | 0           |          | 3403.7762430939226519  | 6.033                                  |

| 23912     | beam    | 2023-07-27 04:15:59 | 2023-07-27 04:21:40 |                 | 1097876     | -1             | 0           |          | 3219.5777126099706745  | 5.683                                  |

| 23913     | beam    | 2023-07-27 04:24:02 | 2023-07-27 04:30:32 |                 | 836609      | -1             | 0           |          | 2145.1512820512820513  | 6.500                                  |

| 23914     | beam    | 2023-07-27 04:33:02 | 2023-07-27 04:38:39 |                 | 854458      | -1             | 0           |          | 2535.4836795252225519  | 5.617                                  |

| 23915     | beam    | 2023-07-27 04:43:39 | 2023-07-27 04:49:39 |                 | 892075      | -1             | 0           |          | 2477.9861111111111111  | h.pdf 6.000                            |

| 23916     | beam    | 2023-07-27 04:52:22 | 2023-07-27 04:58:03 |                 | 882601      | -1             | 0           |          | 2588.27272727272727272 | tEdge <b>5,6</b> 83                    |

| 23917     | beam    | 2023-07-27 05:00:32 | 2023-07-27 05:06:17 |                 | 928719      | -1             | 0           |          | 2691.9391304347826087  | HitC5, 750net                          |

| 23918     | beam    | 2023-07-27 05:09:16 | 2023-07-27 05:11:40 |                 | 60886       | -1             | 0           |          | 422.819444444444444    | 2.400                                  |

| 23919     | beam    | 2023-07-27 05:16:31 | 2023-07-27 05:22:19 |                 | 898983      | -1             | 0           |          | 2583.2844827586206897  | 5.800                                  |

| 23920     | beam    | 2023-07-27 05:23:01 | 2023-07-27 05:23:48 |                 | 32258       | -1             | 0           |          | 686.3404255319148936   | - <sup>HITC</sup> 0.783 <sup>∩el</sup> |

| 23921     | beam    | 2023-07-27 05:29:39 | 2023-07-27 05:35:14 |                 | 890837      | -1             | 0           |          | 2659.2149253731343284  | _HitC5,583nel                          |

| 23922     | beam    | 2023-07-27 05:39:05 | 2023-07-27 05:44:56 |                 | 972576      | -1             | 0           |          | 2770.8717948717948718  | _HitC5.850neF                          |

| 23923     | beam    | 2023-07-27 05:47:09 | 2023-07-27 05:52:56 |                 | 939211      | -1             | 0           |          | 2706.6599423631123919  | HitC5,783nel                           |

/sphenix/tg/tg01/commissioning/INTT/data/evt\_files/beam/beam\_intt{0..7}-00023911-0000.evt ncollision 4, open\_time 35, DAC0 18

### • If the trigger rate is too low that there trigger span is longer than 1000, then it can be

# Distributions of the excluded events

### Only evens with -10 cm < MBD\_z\_vtx < 10 cm are included Events w/ NextInttBcoFull - ThisInttBcoFull > <u>61</u> are kept

16,542 out of 1,166,243 events are excluded  $\rightarrow$  1.42%

Cheng-Wei Shih (NCU, Taiwan)

INTT meeting

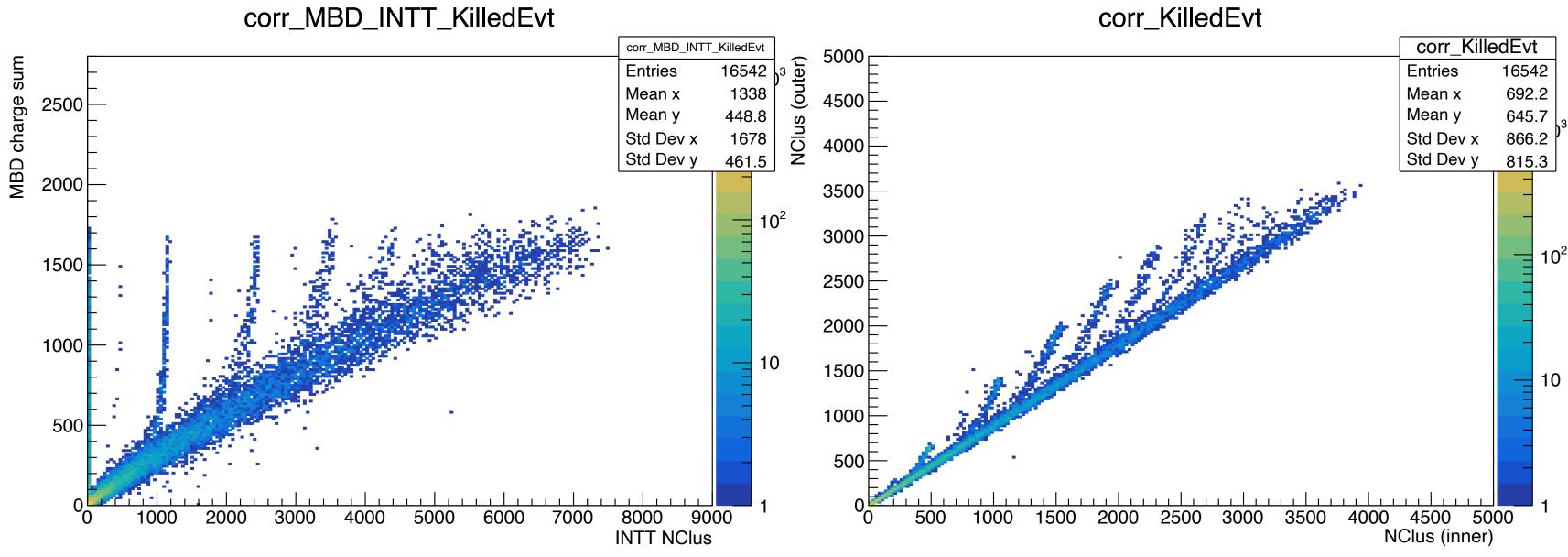

## Proposed selection: correlations, post cut

Only evens with -10 cm < MBD\_z\_vtx < 10 cm are included Events w/ NextInttBcoFull - ThisInttBcoFull > 61 are kept

### Here shows you the killed events

16,542 out of 1,166,243 events are excluded  $\rightarrow$  1.42%

Cheng-Wei Shih (NCU, Taiwan)

INTT meeting

SPHE

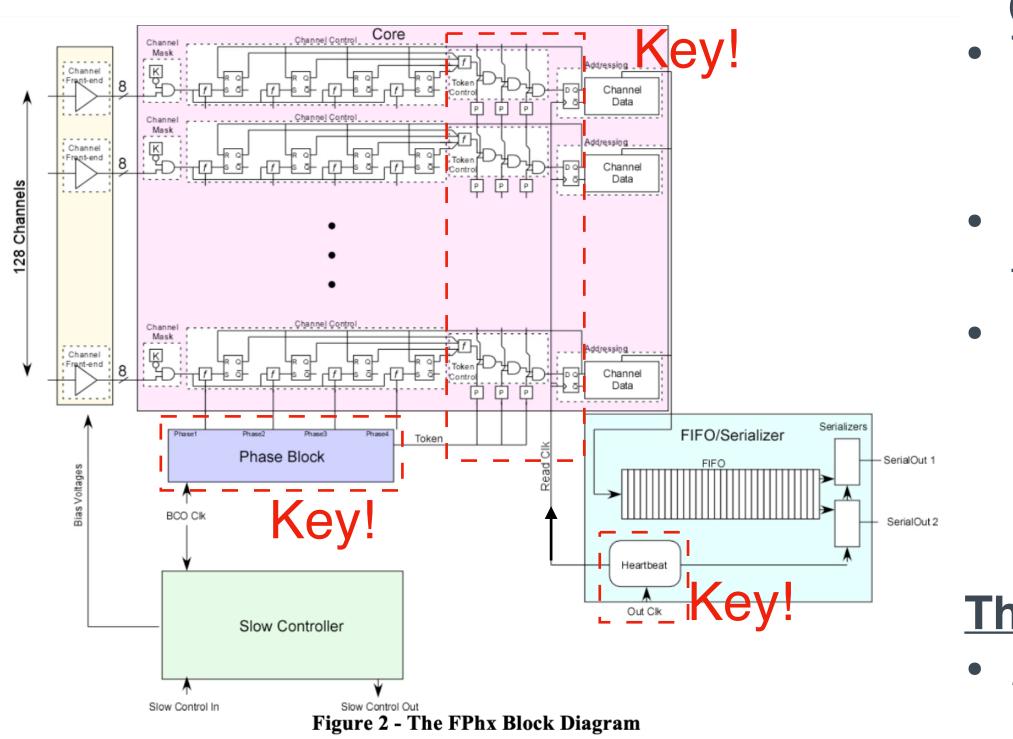

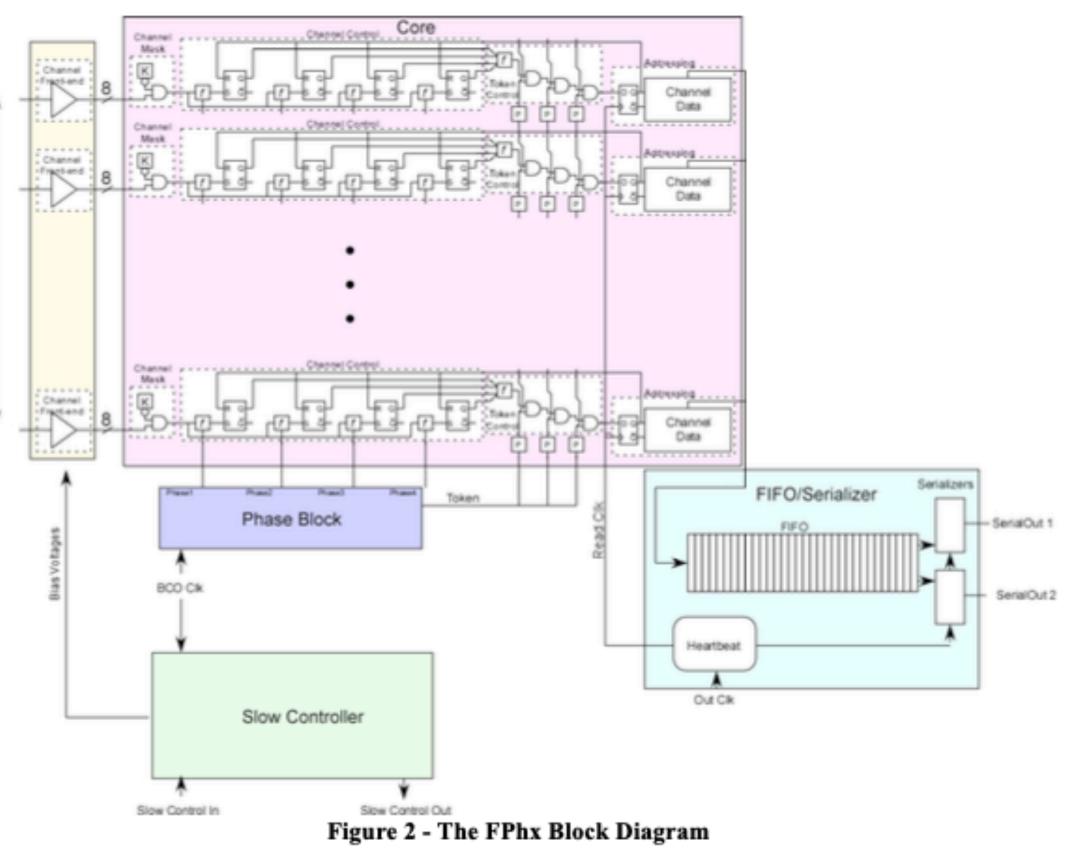

# FPHX chip manual - goal of FPHX

### Phase Block

A primary requirement of the FPhx architecture is that it be able to read out within four beam cross-over periods an event that contained four hit strips. In other words, regardless of activity level, long latency cannot be tolerated. Hits must be sensed, amplified, discriminated, captured, sorted, serialized and read out of the chip. Moreover, the requirements do not allow for dead time, so if an FPhx chip receives an event in beam cross-over period "N", it must be able to deal with an event in beam cross over period "N+1" and in beam cross-over period "N+2", etc.

> Requirement of PHENIX FVTX: read out 4 hits in 4 BCOs and no dead time

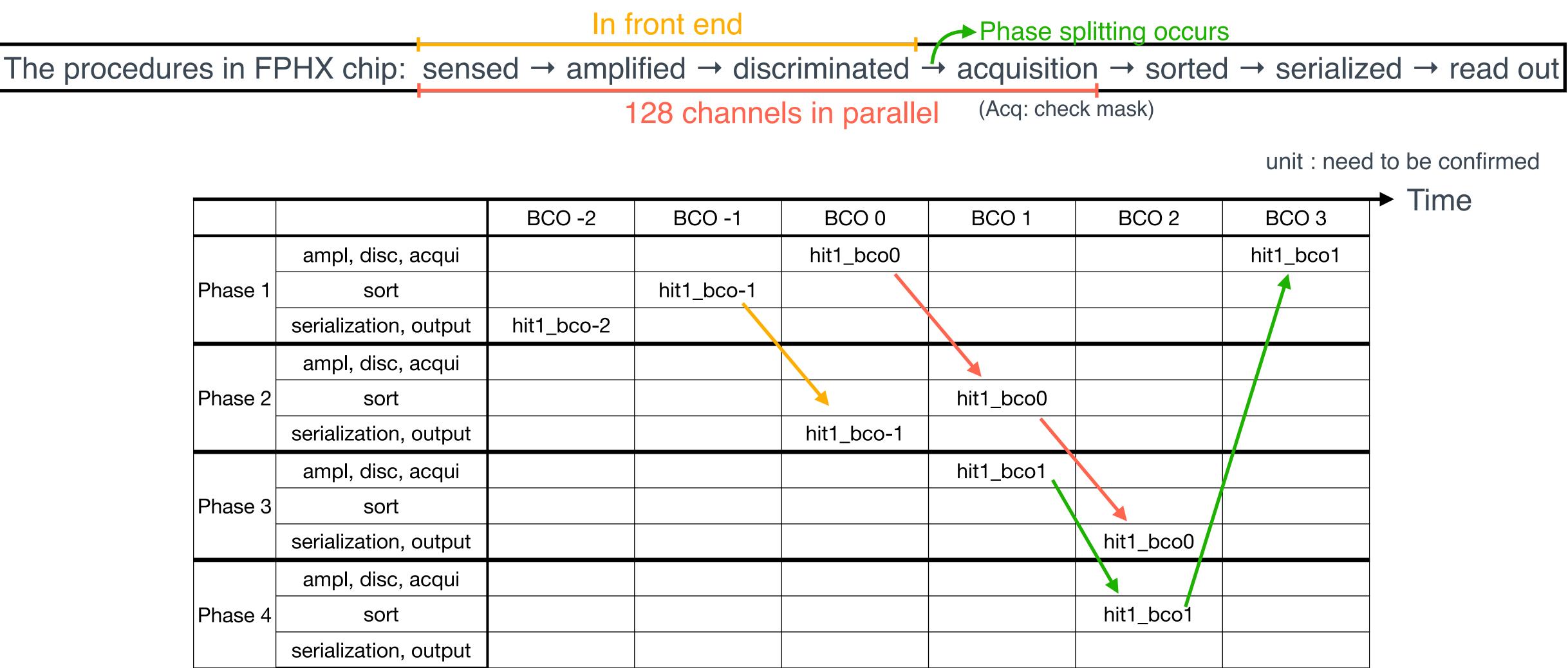

The procedures in FPHX chip: sensed  $\rightarrow$  amplified  $\rightarrow$  discriminated  $\rightarrow$  acquisition  $\rightarrow$  sorted  $\rightarrow$  serialized  $\rightarrow$  read out 128 channels in parallel

If it's possible, it must be good to have the nhits and cluster size distributions of PHENIX FVTX AAA

Cheng-Wei Shih (NCU, Taiwan)

INTT meeting

SPHE

# FPHX chip manual - phase architecture

The procedures in FPHX chip: sensed  $\rightarrow$  amplified  $\rightarrow$  discriminated  $\rightarrow$  acquisition  $\rightarrow$  sorted  $\rightarrow$  serialized  $\rightarrow$  read out

128 channels in parallel

These twin requirements of low-latency and zero dead time give rise to the notion of phase architecture. During any given phase, amplification, discrimination, acquisition, sorting, serialization and output must happen. However, amplification, discrimination and acquisition are happening for hits that are occurring in *this* phase. Sorting is happening for hits that occurred in the last phase. Serialization and output are happening for hits that occurred at least two phases ago.

This approach would require redundant circuitry. For example, there would be Phase 1 acquisition circuitry and Phase 2 acquisition circuitry and Phase 3 acquisition circuitry and Phase 4 acquisition circuitry. Moreover, there would have to be additional circuitry to manage the flow of data through these different phases. However, this approach would enable the job to be done without requiring excessive speed and the consequent power that would require.

Though I didn't find the redundant circuitry in the block diagram

Cheng-Wei Shih (NCU, Taiwan)

The requirement of "four-hits-in-four-beam-crossings" suggests that a cyclic progression of four phases (Phase 1 -> Phase 2 -> Phase 3 -> Phase 4 -> Phase 1 -> etc) could be used as the cornerstone of an architecture built to work for Phenix. During

# FPHX chip manual - phase architecture

### In front end

|         |                       | BCO -2     | BCO -    |

|---------|-----------------------|------------|----------|

|         | ampl, disc, acqui     |            |          |

| Phase 1 | sort                  |            | hit1_bcc |

|         | serialization, output | hit1_bco-2 |          |

|         | ampl, disc, acqui     |            |          |

| Phase 2 | sort                  |            |          |

|         | serialization, output |            |          |

|         | ampl, disc, acqui     |            |          |

| Phase 3 | sort                  |            |          |

|         | serialization, output |            |          |

|         | ampl, disc, acqui     |            |          |

| Phase 4 | sort                  |            |          |

|         | serialization, output |            |          |

|         |                       |            | •        |

In given phase, all the steps must happened, dealing with different hits from different phases

INTT meeting

Cheng-Wei Shih (NCU, Taiwan)

SPHE

# The logic of chip (tentative, conceptual)

### The FPHX chip manual

#### \*Key: relevant parts for this issue but not fully understood

#### **Token Logic**

The Token Logic divides the chip into individual channels, blocks of eight channels and banks of 32 channels. It performs this division with three token tiers. The Tier 3 token selects which bank of 32 has access to the bus. The Tier 2 token selects which block of 8 has access to the bus. Finally, the Tier 1 token selects which individual channel has the bus. A channel can only have the bus if it has all three tokens AND a hit to output.

The direct question would be, how long does it take to process one hit, and in what sequence the hits are sent to ROC?

#### INTT meeting

Cheng-Wei Shih (NCU, Taiwan)

(The followings are based on the observations and limited understanding in the FPHX chip manual) • The sequence of signal processing does not follow the channel ID - The channels are categorized into 4 groups (**phases**) - The phase where hit is assigned to is based on the phase state

### The hypothesis:

### **Tentative conceptual conclusion**

• It seems that the sequence of data transmission of each phase is from the hit with smaller channel ID to the that of large channel ID

• It seems that the data transmission of the 4 phases follows some order (cannot be all the phases at once)

- It's partially because of the FIFO

- In one period of time (say 1 BCO), one chip can send out two hits by two data lines, `SerialOut1` and `SerialOut2`

• 2 out of 4 phases successfully send out all the hits to the FELIX in time - Result in the structure of zebra crosswalk

• Rest 2 phases can only send of partial hits to FELIX in time

- Upon some channel ID (some where channel ID 43 or 46), it's already out of time (open\_time). The FELIX servers therefore reject the hits

Result in the big chunk

INTT meeting

#### SPHE

#### The FPHX back-end

#### Chip Organization

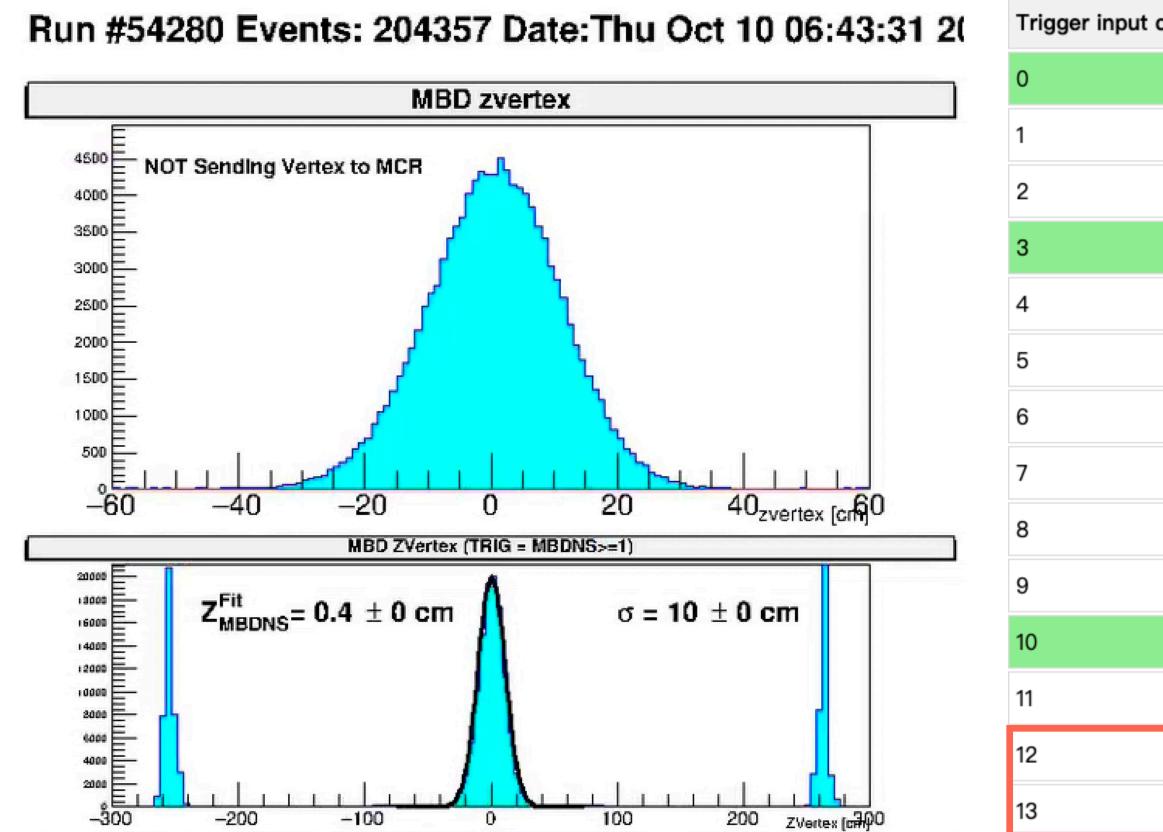

# **Run description - 54280**

- Spike appears at each end of MBD

- The mini-bias definition is not yet available (as far as I know)

- Live trigger available to constraint the MBD vertex Z

#### **INTT** meeting

| channel | Name                      | enabled | Scaledown | Raw         | Live <\div> | Scaled   | Live (%) |

|---------|---------------------------|---------|-----------|-------------|-------------|----------|----------|

|         | Clock                     | yes     | 93810     | 33836274325 | 33663041357 | 358838   | 99.5     |

|         | ZDC South                 | yes     | off       | 102829214   | 102308816   | 0        | 99.5     |

|         | ZDC North                 | yes     | off       | 98430768    | 95872319    | 0        | 97.4     |

|         | ZDC Coincidence           | yes     | 60        | 9417100     | 9370209     | 153672   | 99.5     |

|         | HCAL Singles/Coincidence  | yes     | off       | 30282609    | 30125423    | 0        | 99.5     |

|         |                           | yes     | off       | 33836274325 | 33663041357 | 0        | 99.5     |

|         |                           | yes     | off       | 0           | 0           | 0        | 0        |

|         |                           | yes     | off       | 0           | 0           | 0        | 0        |

|         | MBD S >= 2                | yes     | off       | 86958423    | 86380777    | 0        | 99.3     |

|         | MBD N >= 2                | yes     | off       | 85797943    | 85195687    | 0        | 99.3     |

|         | MBD N&S >= 2              | yes     | 0         | 10242665    | 10187457    | 10187457 | 99.5     |

|         | MBD N&S >= 1              | yes     | off       | 18093659    | 17967450    | 0        | 99.3     |

|         | MBD N&S >= 2, vtx < 10 cm | yes     | off       | 4021509     | 4000602     | 0        | 99.5     |

|         | MBD N&S >= 2, vtx < 30 cm | yes     | off       | 5799143     | 5768655     | 0        | 99.5     |