# The Ladder and Readout Cables of Intermediate Silicon Strip Detector for sPHENIX\*

- Y. Akiba<sup>a,b</sup>, H. Aso<sup>g,a</sup>, J. T. Bertaux<sup>i,b</sup>, D. Cacace<sup>c</sup>, K. Y. Chen<sup>d</sup>, K. Y. Cheng<sup>d,b</sup>, A. Enokizono<sup>a</sup>,

- H. Enyo<sup>a,b</sup>, K. Fujiki<sup>g,a</sup>, Y. Fujino<sup>g,a</sup>, M. Fujiiwara<sup>e,a</sup>, T. Hachiya<sup>e,b</sup>, T. Harada<sup>g,a</sup>, S. Hasegawa<sup>f</sup>,

- M. Hata $^{e,b}$ , B. Hong $^k$ , J. Hwang $^{k,b}$ , T. Ichino $^{g,a}$ , M. Ikemoto $^{e,a}$ , H. Imagawa $^{g,a}$ , H. Imai $^{g,a,b}$ ,

- Y. Ishigaki<sup>e,a</sup>, M. Isshiki<sup>e</sup>, K. Iwatsuki<sup>e,a</sup>, R. Kan<sup>e</sup>, M. Kano<sup>e,a</sup>, T. Kato<sup>g,a</sup>, Y. Kawashima<sup>g,a</sup>,

- T. Kikuchi<sup>g,a</sup>, T. Kondo<sup>h</sup>, C. M. Kuo<sup>d</sup>, C. Kureha<sup>e</sup>, T. Kumaoka<sup>a</sup>, H. S. Li<sup>i</sup>, R. S. Lu<sup>i</sup>,

- E. Mannel<sup>c</sup>, H. Masuda<sup>g,a</sup>, G. Mitsuka<sup>b</sup>, N. Morimoto<sup>e,a</sup>, M. Morita<sup>e,b</sup>, I. Nakagawa<sup>a,b,\*</sup>,

- Y. Nakamura<sup>g,a</sup>, G. Nakano<sup>g,a</sup>, Y. Namimoto<sup>e,b</sup>, D. Nemoto<sup>g,a</sup>, S. Nishimori<sup>e</sup>, R. Nouicer<sup>c</sup>,

- G. Nukazuka<sup>a</sup>, I. Omae<sup>e,a</sup>, R. Pisani<sup>c</sup>, Y. Sekiguchi<sup>a</sup>, M. Shibata<sup>e,b</sup>, C. W. Shih<sup>d,b</sup>, K. Shiina<sup>g,a</sup>,

- M. Shimomura<sup>e</sup>, R. Shishikura<sup>g,a</sup>, M. Stojanovic<sup>i,b</sup>, K. Sugino<sup>e</sup>, Y. Sugiyama<sup>e</sup>, A. Suzuki<sup>e,b</sup>,

- R. Takahama $^{e,b}$ , W. C. Tang $^{d,b}$ , Y. Terasaka $^{e}$ , T. Todoroki $^{\bar{b}}$ , H. Tsujibata $^{e,a}$ , T. Tsuruta $^{g,a}$ ,

- Y. Yamaguchi<sup>b</sup>, H. Yanagawa<sup>g,a</sup>, M. Watanabe<sup>e,b</sup>, R. Xiao<sup>i</sup> and W. Xie<sup>i</sup>

### ARTICLE INFO

## ABSTRACT

A new silicon-strip-type detector was developed for precise charged-particle tracking in the central rapidity region of heavy ion collisions. A new detector and collaboration at the Relativistic Heavy Ion Collider at Brookhaven National Laboratory is sPHENIX, which is a major upgrade of the PHENIX detector. The intermediate tracker (INTT) includes the advanced tracking system of the sPHENIX detector complex together with a CMOS monolithic-active-pixel-sensor (MAPS) based silicon-pixel vertex detector (MVTX), a time-projection chamber (TPC), and a micromegas-based detector. The INTT detector is barrel shaped and comprises 56 silicon ladders. Two different types of strip sensors of 78  $\mu m$  pitch and 320  $\mu m$  thick are mounted on each half of a silicon ladder. Each strip sensor is segmented into 8×2 and 5×2 blocks with lengths of 16 and 20 mm. Strips are read out with a silicon strip-readout (FPHX) chip. In order to transmit massive data from the FPHX to the down stream readout electronics card (ROC), a series of long and high speed readout cables were developed. This document focus on the silicon ladder, the readout cables, and the ROC.

# 1. Introduction

The sPHENIX detector [1, 2] at the Relativistic Heavy

Ion Collider (RHIC) at Brookhaven National Laboratory,

USA is a major upgrade of the PHENIX detector [3], which

- was decommissioned in 2017. The sPHENIX experiment

- collects high statistics proton-proton, proton-nucleus, and

- nucleus-nucleus data, enabling state-of-the-art studies of jet

- modification, upsilon suppression, and open heavy-flavor

itaru@riken.jp (I. Nakagawa)

ORCID(s):

production to probe the microscopic nature of the strongly-coupled quark-gluon plasma. Such measurements are complementary to those of experiments at the Large Hadron Collider (LHC) at CERN, and will allow a broad range of cold quantum-chromodynamic studies [4].

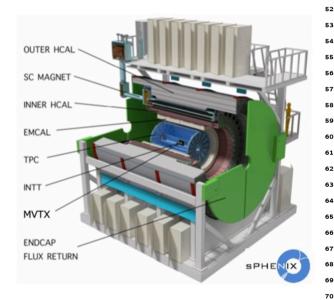

The sPHENIX detector provides precision vertexing, tracking, and electromagnetic and hadronic calorimetry in the central pseudorapidity region  $|\eta|$ <1.1 with full azimuthal coverage at the full RHIC collision rate. A comprehensive assessment of these requirements led to the development of the reference design shown in Fig. 1. In its overall layout, sPHENIX follows the typical geometry of modern collider detectors. The tracking system comprises

<sup>&</sup>lt;sup>a</sup>Nishina Center for Accelerator-Based Science, RIKEN, 2-1 Hirosawa, Wako, 351-0198, Saitama, Japan

<sup>&</sup>lt;sup>b</sup>RIKEN BNL Research Center, 20 Pennsylvania Avenue, Upton, 11973, NY, U.S.A.

<sup>&</sup>lt;sup>c</sup>Brookhaven National Laboratory, 20 Pennsylvania Avenue, Upton, 11973, NY, U.S.A.

<sup>&</sup>lt;sup>d</sup>Department of Physics and Center for High Energy and High Field Physics, National Central University, No.300, Zhongda Rd., Zhongli Dist., Taoyuan City, 32001, Taiwan

<sup>&</sup>lt;sup>e</sup>Department of Mathematical and Physical Sciences, Nara Women's University, Kitauoya-Higashimachi, Nara, 630-8506, Nara, Japan

fAdvanced Science Research Center, Japan Atomic Energy Agency, 2-4 Shirakata Shirane, Tokai-mura, Naka-gun, 319-1195, Ibaraki, Japan

<sup>&</sup>lt;sup>8</sup>Rikkyo University, Department of Physics, 3-34-1 Nishi-Ikebukuro, Toshima, Tokyo, 171-8501, Tokyo, Japan

<sup>&</sup>lt;sup>h</sup>Tokyo Metropolitan Industrial Technology Research Institute, 2-4-10, Aomi, Koto, Tokyo, 135-0064, Tokyo, Japan

<sup>&</sup>lt;sup>i</sup>Department of Physics and Astronomy, Purdue University, 525 Northwestern Ave., West Lafayette, 47907, IN, U.S.A.

<sup>&</sup>lt;sup>j</sup>Department of Physics, National Taiwan University, No.1 Sec.4 Roosevelt Road, Taipei, 10617, Taiwan

<sup>&</sup>lt;sup>k</sup>Korea University, Department of Physics, Anam-dong 5, Seongbuk-gu, Seoul, 02841, Korea

<sup>\*</sup>This work is supported by

<sup>\*</sup>I. Nakagawa

Table 1

Number of the INTT silicon ladders of the inner and outer layers of the INTT barrel detector

|                   | Inner | Outer |

|-------------------|-------|-------|

| Number of ladders | 24    | 32    |

a CMOS monolithic-active-pixel-sensor (MAPS) microvertex detector (MVTX), a silicon-strip intermediate tracker (INTT), and a time-projection chamber (TPC). For calibration, a micromegas based detector (TPOT) [5] partially covers the outside of the TPC acceptance. The calorimeter stack includes a tungsten/scintillating fiber electromagnetic calorimeter (EMCAL) and aluminum/scintillator and steel/scintillator tile hadronic calorimeter (HCAL), divided into inner and outer parts. The inner HCAL sits inside the 1.4 T superconducting solenoid, which was refurbished from the decommissioned BaBar detector [6].

24

26

28

30

31

32

37

30

40

42

43

Figure 1: The mechanical drawing of the sPHENIX detector.

This document features the detail of the INTT silicon<sub>74</sub> ladder, its readout cables, and the readout electronics card. <sub>75</sub>

### 2. Detector Overview

The barrel-type INTT detector comprises inner and outer 19 layers of INTT silicon ladders. The adjacent ladders are 19 staggered to prevent dead space between them in the azimuthal acceptance. The inner and outer barrels have 24 and 32 ladders, respectively as summarized in the Table 1. 18 The details of the INTT barrel is beyond the scope of this 19 document and a separate paper is under preparation.

The designs of the INTT ladder and its readout are constrained by the specification of of the FPHX readout chip and the readout card (ROC) of the FVTX detector[7] in PHENIX. Since the INTT reuses the FPHX design and

Table 2

The components and total number of channels of the INTT module and ladder. The details of silicon strip sensor type-A and B are to be discussed in the section 3.1.

|         | Component                | Quantity       |

|---------|--------------------------|----------------|

|         | Silicon strip sensor     | 2 (Type-A & B) |

| Silicon | FPHX Chips               | 26             |

| module  | HDI                      | 1              |

|         | Total number of channels | 3,328          |

| Silicon | Silicon module           | 2              |

| ladder  | Stave                    | 1              |

|         | Total number of channels | 6,656          |

the ROC, the rest of INTT detector was designed to be compatible with these readout chip and electronics. The FPHX was produced news ones for the INTT detector, while the ROCs were recycled. The major difference between the FVTX and INTT detectors are mechanical concept. While the INTT is the barrel type with 2 layers, the FVTX was a disk type with 4 layers.

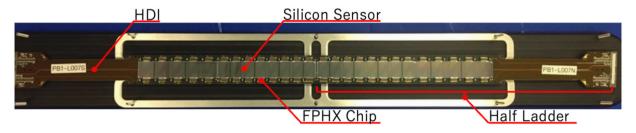

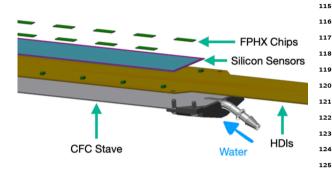

Two silicon sensors and 26 FPHX readout chips [7] are mounted on a high=density interconnect (HDI) flexible print cable to form an INTT silicon module. Two INTT modules are lined up longitudinally and glued to a carbon fiber composite (CFC) support stave to form an INTT silicon ladder, as shown in Fig. 2. These components of the INTT silicon module and the ladder are summarized in Table 2. To display the image of the layer structures of the INTT ladder, the stackup of the components of the ladder is illustrated in Fig. 3.

Both glue and carbon fibers have high thermal conductivity to diffuse heat generated by the FPHX chips. A water-cooling system removes heat from the barrel through a carbon tube implemented inside the body of the stave. Figure 3 also shows the tube attached to the edge of the CFC stave, which is the inlet of the cooling water.

The data of a given ladder are read out from both longitudinal ends for each silicon module. Thus, each HDI cable transmits data from half of a ladder. The data are further transmitted downstream from the HDI by a bus extender (BEX) cable [19] and a conversion cable (CC). The BEX is a 1.11 meter long flexible print cable (FPC) employing liquid-crystal polymer as a dielectric material to suppress losses in transmission lines. In both ends, the conversion cable comprises three components; 1)  $\mu$ -coaxial harness, 2) power and ground cables, and 3) connector print boards. The downstream end of the conversion cable is connected to the read-out card (ROC) which collects data up to seven half ladders and then transmits reformatted data to further downstream electronics via an optical fiber connection. The downstream electronics beyond the ROC and data acquisition system are beyond the scope of this document.

**Figure 2:** Photo of the INTT ladder with sensors facing up. Note the center line dividing the two halves of the sensor and the rows of FPHX chips along the sensor edges.

129

141

142

Figure 3: The stackup of the components of the INTT ladder.126

### 3. INTT Ladder

90

97

101

102

103

104

105

106

107

109

110

111

112

113

114

This section describes the electrical components and 31 support systems used to read out and power the INTT 132 The silicon-strip sensors and the FPHX readout chips are 33 introduced in subsections 3.1 and 3.2, respectively. The 134 high-density interconnects (HDI) that provide power, bias 135 voltage, and slow-control signals to the sensor are discussed in subsection 3.3. The stave support structure is discussed in subsection 3.4. The material budget of the ladder in radial 137 direction is discussed in discussed in subsection 3.5. Lastly 138 the dead space of the silicon ladder is evaluated in subsec 139 tion 3.6.

### 3.1. Silicon Sensors

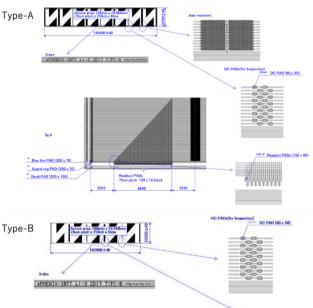

The silicon-strip sensor [8] is single-sided and AC<sub>143</sub> coupled. The design is based on and modified from the,44 PHENIX FVTX silicon mini-strip sensors [7]. The sensors (model S14629-01), as well as the FVTX sensors, were fab-146 ricated by Hamamatsu Photonics KK. There are two types, 47 of sensors (type-A and type-B), which are distinguished by,18 the length of strips and number of blocks. The type-A sensor, has an active area of  $128 \times 19.968$  mm, which is segmented<sub>150</sub> into 8 rows and 2 columns of blocks, each of which consisted 151 of 128 strips with 78 µm pitch and 16 mm long, which are 152 oriented in the longitudinal direction. Similarly, the type-B<sub>153</sub> sensor has an active area of  $100 \times 19.968$  mm, which is  $_{154}$ segmented into 5 rows and 2 columns of blocks, each of 155 which comprises 128 strips in 78  $\mu$ m pitch and 20 mm long<sub>156</sub> and is also oriented in the longitudinal direction. Table 3,157 summarizes these dimensions.

The small gap between adjacent blocks where the DC pads are laid out on the surface is completely active. The sensors were fabricated with p-implants on a 320  $\mu$ m thick n-type substrate. The strips are AC-coupled and biased through individual 15 M $\Omega$  poly-silicon resistors to a typical operating voltage of 100 V. The aluminum metallization width on the strips is 20  $\mu$ m which is wider than the implant width of 10  $\mu$ m to provide field-plate protection against micro discharges which are known to grow with radiation-induced increases in the leakage current. The strips are also protected by two p-implant guard rings and an n+ surround between the guard rings and the sensor edge. These designs follow from the silicon-strip sensors of the FVTX [7]. Figure 4 shows details of the sensor layout, including guard rings, bond-pad locations, and mechanical fiducial marks.

In Fig. 4 the strip runs horizontally (longitudinal direction). The readout lines of each strip are wired perpendicular to the strips orientation using double-metal technology. The other end of the readout lines are implemented with readout pads which transmit data to the FPHX chips using a wire bonding.

### 3.2. FPHX chip

A custom 128-channel front-end ASIC, the FPHX[10], was developed at Fermilab for use in the PHENIX FVTX Detector [7]. The size of the chip is  $9 \times 2$  mm. The chip is operated at 2.5 V and consumes power as low as 64 mW per chip. The FPHX is a mixed-mode chip with two major and distinct sections - the analog front-end and the digital back-end. The analog section consists of an integrator/shaper stage followed by a 3-bit ADC. The FPHX chip integrates and shapes signals from 128 channels of strips, digitizes and sparsifies the hit channels for each beam crossing, and serially reads out the digitized data. The back-end is a novel trigger-less data push architecture that permits dead-timeless operation and high-speed readout with very low latency. It has been designed to process up to four hits within four RHIC beam crossings. Although it takes longer, it can process more than 4 hits from a given crossing. A fully processed hit pattern is zero suppressed, contains a 7-bit time stamp in the unit of RHIC repetition frequency 9.4MHz (1/106 ns), 7-bit channel ID, and 3-bit ADC value. The data word is output over two LVDS serial lines in alternating order at up to 200 MHz clock rate. The summary of the FPHX specifications [9][10] is given in Table 5.

Table 3

The dimensions of type-A and type-B silicon strip sensors. [8]

| Item                       | Type-A                 | Type-B             | Type-A+B Total     |

|----------------------------|------------------------|--------------------|--------------------|

| Physical dimension         | 130.0 mm × 22.5 mm     | 102.0 mm × 22.5 mm | 232.0 mm × 22.5 mm |

| Active area dimension      | 128~mm 	imes 19.968~mm | 100 mm × 19.968 mm | 228 mm × 19.968 mm |

| Active area fraction       | 87.4%                  | 87.0%              |                    |

| Active cell dimension      | 16 mm × 19.968 mm      | 20 mm × 19.968 mm  | N/A                |

| # of cells                 | 8                      | 5                  | 13                 |

| Active block dimension     | 16 mm × 9.984 mm       | 20 mm × 9.984 mm   | N/A                |

| # of blocks                | 16                     | 10                 | 26                 |

| Number of blocks per cell  | 2                      |                    |                    |

| Number of strips per block | 128                    |                    |                    |

| Strip pitch                | 78 μm                  |                    |                    |

| Number of strip channels   | 2,048                  | 1,280              | 3,328              |

Figure 4: The schematics of the type-A (top) and type-B<sup>171</sup> (bottom) silicon sensors [8].

In addition, to be as "self-sufficient" as possible, the FPHX provides its own internal bias voltages and currents with minimal external support circuitry. For the user to be able to control the internal parameters and biases, a digital slow-control interface is provided on each chip to enable programming. Adjustable parameters include gain, threshold, rise time, fall time, input transistor bias current, channel mask, plus several additional fine tuning parameters [9].

Table 4

Specifications of the silicon strip sensors [8].

| Item                         | Specification       |

|------------------------------|---------------------|

| SSD type                     | AC-SSSD             |

| Nominal operating voltage    | 100 V               |

| Bias Providing Type          | Poly-Si bias        |

| Poly-Si resistance           | 15 MΩ               |

| Silicon thickness            | 320 μm              |

| Strip implant width          | $10~\mu \mathrm{m}$ |

| Strip readout aluminum width | 20 μm               |

**Table 5**Specifications of the FPHX readout chip [9].

| Item               | Specification |

|--------------------|---------------|

| Dimension          | 9 mm × 2 mm   |

| Operation voltage  | 2.5 V         |

| Power consumption  | 64 mW         |

| Number of Channels | 128           |

| ADC channels       | 3 bits        |

| Data Transmission  | 200 MHz       |

# 3.3. High-density interconnects

The HDI is a flexible print circuit board to read out a half ladder, which comprises two silicon sensors with 26 FPHX chips. The basic layer structure design of the HDI follows from the FVTX [7]. The geometrical constraint for the silicon ladder is somewhat less stringent for the INTT than for the FVTX. Thus, the circuit design parameters such as line and space are relaxed from the FVTX, which resulted in improved yield rate in the fabricating process. The HDI was designed by HAYASHI-REPIC Co., Ltd. and fabricated by YAMASHITA MATERIALS CORPORATION in Japan. The width of the HDI is 38 mm in the sensor area and 43 mm at the connector end. The length is 398 mm, which is the longest limit of industry fabrication for the multilayer FPC in an automated manner using dedicated fabrication machines.

159

160

161

162

163

164

165

166

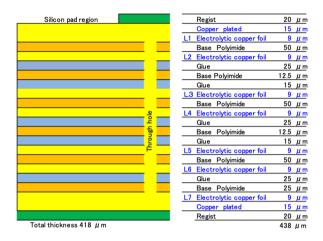

The HDI is seven layered and is the stack up of 9  $\mu$ m $_{17}$ thick electrolytic copper foil, 50  $\mu$ m thick polymide, and 15 $_{18}$ to 25  $\mu$ m thick resin glue. The total thickness is 418  $\mu$ m $_{19}$ in the sensor area. As discussed in subsection 3.5, the totab $_{20}$  thickness of copper layers is 68  $\mu$ m which is the major $_{22}$  component of the material budget of the INTT ladder. The $_{22}$  top and bottom copper foil layers were plated with 15  $\mu$ m $_{23}$  thick copper $_{1}$ . Shown in Fig. 5 is the cross section of the seven-layer structure of the HDI.

Figure 5: Seven layer structure of HDI.

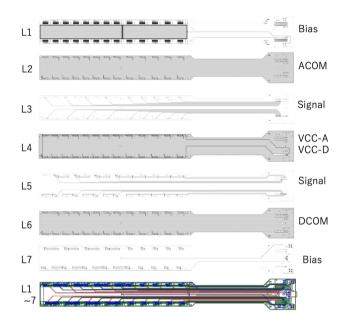

The schematic of each layer is shown in Fig. 6. From the top to bottom layers, each layer has dedicated purposes to transmit bias for the type-B silicon sensor (L1), analogue ground (L2), signals (L3), DC powers for the analog and digital parts of FPHX (L4), signal (L5), digital ground (L6), and for the type-A sensor and signals (L7). There are two thermostats implemented on the L7 to monitor the cooling status of heat generated during operation from the FPHX chips.

There are 122 signal lines total. They are 52 output data and 8 slow-control & clock LVDS pairs and two dedicated lines to inject calibration pulses to the FPHX. Signal transmission lines are mainly placed in layers 3 and 5 to be shielded from external electromagnetic (EM) fields by keeping these layers between solid-copper layers which are assigned for either analog or digital grounds or the DC power. The line & space are both 60  $\mu$ m. The characteristic impedance is designed to be 100  $\Omega$  differential for these LVDS pair lines to ensure matching with the rest of the<sup>224</sup> readout cable chain.

Some signal lines running in the sensor region L7 is not<sup>226</sup> the same design as in the FVTX. These signal lines were<sup>227</sup> changed to keep the HDI width as narrow as possible and<sup>228</sup> thus would not fit within the signal layers. The narrow width<sup>229</sup> enables building the barrel detector as round as possible by<sup>330</sup> minimizing physical interference between adjacent ladders.

Because the back plane of L7 is not shielded by either the solid foil ground or the power layers, the signal lines are exposed to the external EM fields. Thus, the length of the lines were kept as short as possible (< a few cm). Figure 7 shows a photo of the HDI cables with L1 and L7 face up. Table 6 summarizes the major specifications of the HDI cable.

**Figure 6:** The schematic of each layer of the HDI. The ACOM and DCOM layers provide analog and digital grounds to FPHX chips, respectively. The 2.5 V power solid lines for the analog and digital parts of the FPHX chip share the L4, but they are electrically isolated within the layer. The bottom schematic figure shows (in different colors) the overlay of line patterns for all seven layers.

Figure 7: Photo of the HDI cables with L1 and L7 face up.

Pairs of connectors for data, LV power for the FPHX, and grounds are implemented in the end of the HDI. The model of the data connector is Hirose Co. DF18C-100DP-0.4V(51) plug, which consists of 100 channels with 400  $\mu$ m pitch between conducting pins. Also, there are two bias connectors and 3-pin thermostat connectors implemented in the end of the HDI.

# **3.4.** Stave

The stave is a mechanical support made mainly of carbon fiber composite (CFC) skins. The stave itself plus an extension for mechanical attachment spans 497 mm long and

<sup>&</sup>lt;sup>1</sup>The copper plate was 15  $\mu$ m thick for the 1st and 2nd batches of the<sub>232</sub> HDI production. The thickness increased to 25  $\mu$ m for the 3rd batch in HDI production. The total radiation length of the silicon ladder is increased by 3%.

271

272

274

**Table 6**Specifications of the HDI cable. The characteristic impedance is for the LVDS pair.

| Item                                | Specification        | <sup>-</sup> 265 |

|-------------------------------------|----------------------|------------------|

| Dimension                           | 398 mm × 38 mm       | 266              |

| Width of connector ends             | 43 mm                | 267              |

| Total thickness (sensor pad region) | $418~\mu \mathrm{m}$ | 268              |

| Conductive material                 | Copper               |                  |

| Dielectric material                 | Polymide             |                  |

| Number of layers                    | 7                    |                  |

| Number of signal lines              | 122                  |                  |

| Line and space                      | 60 μm & 60 μm        |                  |

| Characteristic impedance            | 100 Ω                |                  |

**Table 7**Specifications of the CFRP prepreg.

236

237

238

240

242

243

244

245

248

250

251

252

253

255

256

257

259

260

261

| Item                  | Specification         |

|-----------------------|-----------------------|

| CFRP prepreg          | NT91500-520S [12]     |

| Carbon fiber          | XN-90                 |

| Resin                 | 25R epoxy             |

| Resin weight fraction | 20 %                  |

| density               | $2.19 \text{ g/cm}^3$ |

| Thermal conductivity  | 500 W/mK              |

| Tensile module        | 860 GPa               |

| Tensilie strength     | 3430 MPa              |

| Thickness             | 100 μm                |

38 mm wide, which matches with the HDI width around the sensor area and accommodates two silicon modules per stave forming the INTT silicon ladder. The heat load expected from each half ladder is 64 mW  $\times$  26 FPHX chips or  $\approx 1.7^{79}$  W. The total heat load over the entire INTT is about 186 W for 112 half ladders.

The stave is required not only for the rigidity of the support structure, but also for high thermal conductivity to dissipate local heat generated by the FPHX chips. The main component of the stave is made of a carbon fiber reinforced plastic prepreg (CFRP). The GRANOC prepreg sheet model NT91500-520S of Nippon Graphite Fiber Co. was used, which comprises 25R epoxy and XN-90 carbon fiber with a high thermal conductivity of 500 W/mK, with resin weight fractions of 20% [12]. The thickness of 0.10 mm with density of 2.19 g/cm<sup>3</sup> prepreg provides satisfactory mechanical strength with tensile module and strength of 860 GPa and 3430 MPa, respectively. Table 7 summarizes<sup>281</sup> the specifications of the CFRP prepreg.

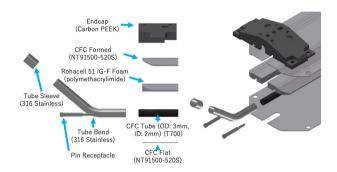

Figure 8 shows the stack up of the stave and the mechan-<sup>283</sup> ical attachments of its edge. The shells of the stave are CFC<sup>284</sup> plates at the top and bottom are flat and formed, respsec-<sup>285</sup> tively. The formed plate is U-shaped to accommodate the<sup>286</sup> 3 mm diameter cooling tube between two CFC plates with<sub>287</sub> 3 mm thick ROHACELL 110 RIST form [13] that tapers<sub>288</sub> down near the edge forming a structural core. A cooling tube is made of Toreyca T700C carbon fiber prepreg [11]

fabricated by Kimuraya Co., Japan. The NT91500-520S sheet is unidirectional with high thermal conductivity. To provide omnidirectional rigidity, each CFC plate has three unidirectional sheet layers with high thermal conductivity oriented in longitudinal, transverse, and longitudinal directions. The thickness of the CFC plate is 0.33 mm and the total thickness of the stave is 3.76 mm.

**Figure 8:** The mechanical design of the edge of the stave. The HDI is assembled on the bottom flat CFC plate.

The mechanical attachment of both edges of the stave comprise the end caps, SUS316 cooling-tube extensions, and pairs of pin receptacles manufactured by Mill-Max MFG Co. for grounding. The endcap is made of Ketron CA30 PEEK [14] manufactured by Mitsubishi Chemical Co. The stainless tubes and the cooling tubes were glued using the Henkel LOCTITE EA 9396 adhesive [15]. The rest of the stave pieces are assembled using the graphite conductive EP75-1 epoxy adhesive (MasterBond Co.) [16]. Figure 9 shows the engineering drawing of the INTT stave. Table 8 summarizes the material list of stave components and specifications.

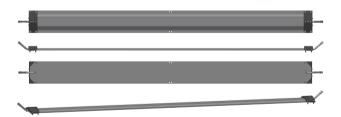

**Figure 9:** The INTT stave. The HDI is assembled on the bottom flat CFC plate.

The staves were fully fabricated by Asuka Co., Japan including the baking process of the CFC plates. To ensure meeting the requirements, the following four tests were applied to staves and to every cooling tube (after the stainless extensions were glued). Only components that passed examination were used.

- 1. Burst test: Keep the tube at the high pressure of  $60 \pm 2$  psi and won't burst for 1 hour.

- 2. Leak test: less than 0.2 ml-mbar/min.

- 3. Heat-cycle test :  $40 \leftrightarrow 0^{\circ}$ C (one cycle).

321

323

324

327

328

331

334

**Table 8**The material list of stave components and specifications. The total thickness is at the sensor region.

| Item                        | Model/Specification      |

|-----------------------------|--------------------------|

| Dimension                   | 497 mm × 38 mm           |

| Total thickness             | 3.76 mm                  |

| Adhesive for stave assembly | MasterBond EP75-1 [16]   |

| Structure core              | ROHACELL 110 RIST [13]   |

| End cap                     | Ketron CA3 PEEK [14]     |

| CFC cooling tube            | Toreyca T700C [11]       |

| Cooling tube extension      | SUS316                   |

| Cooling tube adhesive       | Henkel LOCTITE 9396 [15] |

Table 9

The material budget of the silicon ladder. The TC-2810 is the thermally conductive glue. The radiation thickness of the  $HDI^{316}$  listed in the table is for the production batch 1 and 2.

| Item           | Thickness | Radiation Length |

|----------------|-----------|------------------|

| item           | mm        | $X/X_0$ %        |

| Silicon Sensor | 0.32      | 0.34             |

| Silver epoxy   | 0.01      | 0.02             |

| HDI            | 0.42      | 0.43             |

| TC-2810        | 0.05      | 0.02             |

| Stave          | 3.76      | 0.33             |

| Total          | 4.56      | 1.14             |

4. Flatness < 100  $\mu$ m of the flat side of the stave and alignment positions are within specified tolerance. 330

The staves were assembled with only those cooling tubes<sub>332</sub> that passed the 1 and 2 examinations.

# 3.5. Material Budget

291

292

293

295

297

299

300

301

302

304

305

306

308

309

310

312

313

314

Table 9 summarizes the material budget of the silicon<sub>336</sub> ladder. The total thickness of the silicon pad area of the<sub>337</sub> ladder is 4.57 mm and its effective radiation length  $X/X_{0338}$  is 1.14%. The largest contributions to the budget is the HDI whose radiation lengths is  $X/X_0 = 0.43\%$ . The silicon and<sub>339</sub> the staves are similar radiation length as  $X/X_0 = 0.34\%$  and<sub>340</sub>  $X/X_0 = 0.33\%$ , respectively.

The material budget of the HDI is largely governed by<sub>342</sub> the copper layers. As shown in Fig. 5, there are 7 layers of<sub>343</sub> 9  $\mu$ m thick copper which total 63  $\mu$ m. Furthermore, both<sub>344</sub> top and bottom surface layers are plated by 15  $\mu$ m thickness<sub>345</sub> copper<sup>2</sup>. While the simple stack up of these copper sheets<sub>346</sub> results in 93  $\mu$ m, the effective amount of copper in the signal<sub>347</sub> layers is much less than solid ground layers.

Table 10 summarizes the effective copper thickness of<sub>349</sub> each layer, which was estimated based on the residual copper<sub>350</sub> fraction after the etching process of the HDI fabrication. The<sub>351</sub> effective total thickness is estimated to be 44.7  $\mu$ m, which<sub>352</sub> is approximately 48% of the 93  $\mu$ m total stack-up thickness<sub>353</sub>

**Table 10**The effective thickness of the HDI's copper layers.

| Layer | Function    | Residual copper | Effective         |

|-------|-------------|-----------------|-------------------|

| Layer | Tunction    | fraction %      | thickness $\mu$ m |

| 1     | Bias + AGND | 71.3            | 17.1              |

| 2     | AGND        | 93.5            | 8.42              |

| 3     | Signal      | 6.5             | 0.59              |

| 4     | Power       | 94.0            | 8.64              |

| 5     | Signal      | 7.2             | 0.65              |

| 6     | DGND        | 93.2            | 8.38              |

| 7     | Bias+Signal | 4.7             | 1.12              |

|       | Total       |                 | 44.7              |

the corresponding radiation length  $X/X_0$  is 0.31%. The total thickness of polymide and glue layers is 325  $\mu$ m with  $X/X_0$  of 0.11. The total radiation length of the HDI in the silicon pad area is thus 0.43%.

The silicon sensors were glued on the bias pads of the top layer of the HDI using electrically conductive silver epoxy, i.e. Henkel LOCTITE ABLESTIC 2902 adhesive. The average thickness of the epoxy was aimed to be 9  $\mu$ m based on the 50  $\mu$ m thick glue mask, which has total of 295 glue potting holes with 2 mm diameter each. The radiation length of the silver epoxy was then calculated to be  $X/X_0=0.02\%$  based on the mixing ratio of the silver powder and the epoxy of 0.21:0.79 [17]. Due to the short radiation length  $X_0=8.54$  mm of the silver material, the contribution of the silver epoxy to the total material budget can be nonnegligible. Without the glue mask, the contribution of the 50  $\mu$ m thick silver epoxy is as significant as 12% of the total material budget.

To propagate the heat generated by the FPHX chips, high thermally conductive epoxy adhesive glue,  $3M^{TM}$  TC-2810 [18], was used to assemble the HDI and the stave. The radiation length for the 50  $\mu$ m thick the epoxy makes a very small contribution to the total material budget of the silicon ladder, unlike the silver compound one.

# 3.6. Dead Space

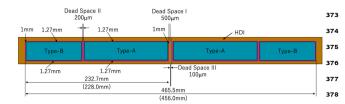

Due to the precision limit of the silicon sensor alignment during the assembly process of the silicon sensors on the sensor pads of the HDI, there are small dead spaces between the edge of the type-A sensor and the tip of the HDI (dead space I), and also the type-A and type-B sensors (dead space II). They are 0.5 and 0.2 mm, respectively as shown in Figure 10.

As the result of the dead spaces in the silicon alignment, the total distance from the boundary of two half ladders to the large rapidity end of type-B sensor is 232.7 mm, while the length of the active region of type-A and type-B sensors is 228.0 mm as tabulated in Table 3. This result in 98% coverage of the active region in the longitudinal direction as summarized in Table 11. On the contrary, there is no additional dead space originated from the alignment in the transverse direction. The fraction of the active region in the transverse direction is thus 88.7% as tabulated in Table 12.

$<sup>^2</sup>$ The thickness of the copper plate was 20  $\mu m$  only for the las<sup>354</sup> production batch, which increases the radiation length of the third batch<sup>955</sup> HDIs by  $X/X_0=0.02\%$ .

30E

397

399

400

401

402

404

405

406

408

409

410

423

424

425

426

**Figure 10:** Dead spaces of the INTT ladder. The number in  $_{380}$  braket is the longitudinal length of the active region of the  $_{381}$  type-A and B sensors altogether.

Table 11

The dimension of the dead space and region in the longitudinal direction of the half ladder.

| Longitudinal    | Physical                   | Active   |

|-----------------|----------------------------|----------|

| Dead space I    | 0.5 mm                     | 0 mm     |

| Type-A          | 130 mm                     | 128 mm   |

| Dead space II   | 0.2 mm                     | 0 mm     |

| Type-B          | 102 mm                     | 100 mm   |

| Total           | 132.7 mm                   | 228.0 mm |

| The fraction of | longitudinal active length | 98.0%    |

**Table 12**The physical and active area of the half ladder.

| Transverse                               | Physical | Active    |

|------------------------------------------|----------|-----------|

| Type-A & B                               | 22.5 mm  | 19.968 mm |

| The fraction of transverse active length |          | 88.7%     |

**Table 13**The physical and active region of the half ladder.

357

358

359

361

362

363

365

367

370

371

372

|                             | Physical                | Active                  |

|-----------------------------|-------------------------|-------------------------|

| Area                        | 5235.75 mm <sup>2</sup> | 4552.70 mm <sup>2</sup> |

| The fraction of active area |                         | 87.0%                   |

The resulting fraction of the active area of the half ladder is 87.0% as tabulated in Table 13.

Lastly, there is another dead space of 0.1 mm between two half silicon ladders (Dead Space III in Figure 10) originated from the alignment precision of the two half silicon modules on the stave. The resulting physical length between the large rapidity end of type-B sensors of two half ladders is 465.5 mm while the total longitudinal length of the active regions of 4 silicon sensors is 456.0 mm. This dead space is relatively minor enough, the fraction of the length of active region still stays as 98.0% in the longitudinal direction for the full ladder.

# 4. INTT Readout Cables and Front End Circuit Board

barrel must be transmitted all the way to the outside of the TPC volume. The ROCs from the FVTX detector, which are downstream electronics for signal processing, cannot fit within the inner diameter of the TPC.

Massive raw data generated from the INTT must be transmitted at high-speed to the ROC through a curved cable path for longer than 1 m. Because no commercial cable satisfies the requirements, a novel bus-extender cable was developed based on flexible printed circuits (FPC). This technology simultaneously satisfies the requirements of high-density signal lines, flexibility, and long cable length. In contrast, the specification of line and space of the bus extender prevented its connector-end design to be compatible with the input connector ports of the existing ROC. Therefore, another 15 to 25 cm conversion cable was developed to interconnect between the bus extender and the ROC. Flexibility in three-dimensions for the conversion cable is required to guide the connection smoothly without introducing any stress at the ROC input connector, This is needed to absorb the geometrical mismatch of the downstream end of the bus extender and the corresponding input connector location of the ROC.

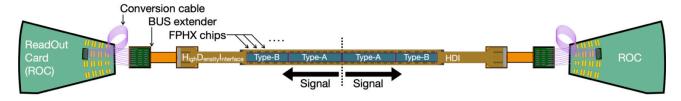

The schematics of the INTT silicon ladder and full readout cable chain up to the ROC is depicted in Fig. 11. The data of each half ladder is readout from opposite side of the full ladder and processed by different ROCs.

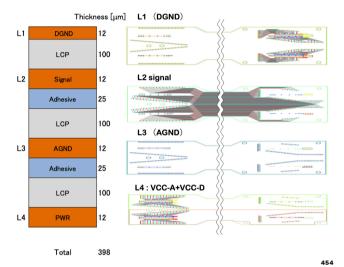

### 4.1. Bus Extender Cable

Only key features of the bus extender (BEX) are described here, because details of the BEX cable are discussed elsewhere [19]. This flexible printed circuit (FPC) cable comprises four layers of three flexible-copper-clad laminate (FCCL) as shown in Fig. 12. The top and third layers are for the digital and analog grounds, respectively. The second layer is used for signal lines. The bottom layer has the power supply lines for the FPHX chips. The choice of the fourlayer structure, instead of the seven-layer structure of the HDI, is primarily driven by fabrication constraints. The yield rate is a big concern for the BEX. The main driver is the signal layer due to its required microfabrication accuracy over the extraordinary length of 1.11 meters. Reducing the number of signal layers was chosen to minimize the risk in the fabrication process. All of the BEX signal lines were thus integrated into a single layer.

Polymide is the most popular market choice of a dielectric material for the FPCs and its fabrication technology is well established in industry. For the BEX case, liquid crystal polymer (LCP) was chosen as the dielectric material due to its lower transmission loss of signal amplitude and the availability of thicker FCCLs in the industrial market compared to polymide. These features are advantageous for the bus extender, whose design is strictly constrained by the precision and yield limit in the fabrication process due to its extraordinarily long length.

The realistic limit of the line and space for the BEX were both found to be 130  $\mu$ m. To achieve a reasonable yield rate in the fabrication factory, which was Printed

Figure 11: The schematics of the INTT silicon ladder and full readout cable chain up to the ROC.

Figure 12: Four layer structure of the BEX (left), and  $_{455}$  schematics of each conductive layer (right) from L1 to L4 $_{456}$

Denshi Kenkyusho Co., Ltd. Given the line and space, the thickness of the dielectric material is required to be as thick as  $100~\mu m$  to match the differential characteristic impedance of  $100~\Omega$ . While such a thick polymide is not available in the industrial market, the  $100~\mu m$  thickness is available in the FERIOS model LCP from Panasonic Industry [20]. The key specifications of the LCP to make the low transmission loss possible are the dielectric constant  $\epsilon=3.3$  and the dissipation factor  $\tan\delta=0.002$ .

429

431

433

435

437

441

445

450

452

453

For the bonding sheet, the a specially optimized model for LCP was employed with thickness of  $25 \mu m$  was chosen for having a low dielectric constant. As a consequence of R&D, this was also a crucial choice to achieve decent yield rate in the through-holes plating process [19] by Taiyo Manufacturing Co., Ltd. because the fabrication technology for the LCP is not as well established as for the polymide. Table 14 summarizes the specifications of the BEX cable.

Pairs of DF18C-100DS-0.4V(81) receptacle connectors<sub>aso</sub> manufactured by Hirose Electric Co. Ltd. are implemented<sub>460</sub> at both ends of the bus extender as shown in Fig. 13. The<sub>461</sub> space between a pair of DF18 plugs is 26 mm which is<sub>462</sub> incompatible with the 10 mm spacing of the input connector<sub>463</sub> pair of the ROC. This extra spacing between the connector<sub>464</sub> pairs of the BEX is caused by the difficulty to wire  $122_{465}$  signal lines of 130  $\mu$ m line & space into the short connector<sub>466</sub>

**Table 14**Specifications of the BEX cable.

| Item                       | Specification         |  |

|----------------------------|-----------------------|--|

| Dimension                  | 1.11 m × 34 mm        |  |

| Width (connector region)   | 43 mm                 |  |

| Total thickness            | $398~\mu\mathrm{m}$   |  |

| Dielectric material        | LCP                   |  |

| Dielectric model           | Panasonic FELIOS [20] |  |

| Dielectric layer thickness | $100~\mu \mathrm{m}$  |  |

| Bonding sheet thickness    | 25 μm                 |  |

| Number of layers           | 4                     |  |

| Number of signal lines     | 122                   |  |

| Line and space             | 130 & 130 μm          |  |

|                            |                       |  |

spacing. Due to the incompatibility of the connector layout between the BEX and the ROC, a conversion cable was introduced which converts the connector spacing from the BEX to the ROC spacing.

Figure 13: A photograph of the 1.11 meter long BEX cable.

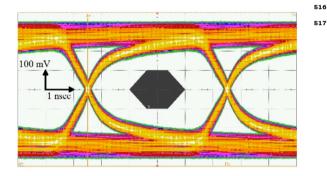

The bus extender successfully moderated the signal attenuation. However, the signal level is still questionable due to the extraordinarily long cable length as a multilayered FPC. The performance of signal transmission was evaluated by measuring; 1) S-parameters, 2) eye-diagram, and 3) time-domain reflectometry (TDR). From the S-parameter measurement, the insertion and reflection losses are -2.7 and -23 dB, respectively at 200 MHz. The measured eye diagram is shown in Fig. 14. The waveform is confirmed to

502

503

505

506

Table 15

467

469

471

473

475

476

478

480

482

486

487

489

490

491

494

495

The performance of the BEX cable. The insertion loss and re-497 turn losses are the performance at 200 MHz. The characteristic impedance is the differential of the LVDS pair.

| Item                     | Performance |

|--------------------------|-------------|

| Insertion Loss           | -2.7 dB     |

| Return Loss              | -23 dB      |

| Characteristic impedance | 90 Ω        |

exhibit a sufficient margin to a defined mask<sup>3</sup> by observing<sub>507</sub> 1 million waveforms of the 200 MHz signal (see the solid<sub>508</sub> hexagon in the middle of Fig. 14). The measured charac<sub>509</sub> teristic impedance was 90  $\Omega$  differential in the TDR mea<sub>510</sub> surement. This is 10% smaller than the default 100  $\Omega$ , it is<sub>511</sub> confirmed to be permissible by the return loss measurement<sub>512</sub> of the daisy chain with the conversion cable as discussed in<sub>513</sub> subsection 4.2. Table 15 summarizes the performance of the<sub>514</sub> BEX cable.

**Figure 14:** The measured eye-diagram of the BEX as a result of transmitting 200 MHz signals for 1 million times [19].

### 4.2. Conversion Cable

As discussed in previous sections, the FPC is the first choice of technology to satisfy the high-performance requirements of signal transmission, high signal-line density, and flexibility. However, it is diffcult for the FPC to satisfy an additional and unique requirement as the last stage of the readout cable series. The requirement is flexibility in three518 dimensions to connect the downstream end of the BEX and519 the input connector ports of the ROC board without intro-520 ducing any stress at the connection. Due to the geometrica1521 mismatch between the INTT barrel ladders and the input522 connector layout of the ROC, flexibility in three dimensions523 is crucial for the conversion cable. If the FPC cable has524 directivity, then stress is induced at the connector end, whicl5256 would bend the cable to the transverse direction of the cable526 plane.

A  $\mu$ -coax technology was chosen. Although the signals line density cannot be as high as the FPC, the three dimensional flexibility offers a good trade-off in the INTT readout design. According to an engineering study, due to its lacks

of flexibility the FPC solution would require as many as 14 different designs in curving and length to interconnect mismatching connector geometries between the BEX and input connectors of the ROC. Furthermore, spare cables of all designs would be needed for risk management, which leads to high cost inefficiency. The  $\mu$ -coax solution reduces the number of designs to be only two in different lengths.

The CABLINE-UX II model manufactured by I-PEX Inc. [21] was employed as the last stage of the signal transmission cable chain for the INTT ladder. The AWG#44 harness is made of silver-plated copper alloy with a center conductor insulated by  $30\mu m$  thick perfluoroalkoxy alkane (PFA) dielectric material from tinned copper alloy with wire wrapping in the outer spiral shield. The shield is covered by the outermost jacket made of the PFA, as well forming a four-layered coaxial cable with total thickness of 0.24  $\pm$  0.01 mm. The characteristic impedance of the harness is  $45\,\Omega$  (90 differential for a LVDS pair). A slim plug and small connectors are assembled for both ends of the harnesses to bundle 50 harnesses in the wire spacing with 0.25 mm pitch. Finally, the harness bundle is wrapped by an acetate cloth adhesive tape.

**Figure 15:** Conversion cable type-AC (top) type-BD (bottom). The bundles in the middle of the cable are 15 cm length  $\mu$ -coax harnesses with four white jacket cables for the power and ground cables. The larger PC board is the connector for the BEX side and the smaller board is for the ROC side.

The conversion cable interconnecting between the BEX and ROC comprises three μ-coax bundles, two power and two ground cables, and the PC boards in both ends. The AWG#24 power and ground cables in both ends are assembled with HJ-3 male pins manufactured by MAC EIGHT Co. Ltd.. The male pin and the receptacle connection are secured by the HH-3-R lock (see Section 4.3). The wire gauge is optimized to be AWG#24 to drop the voltage properly and to provide the FPHX chip power from the slightly higher regulator voltage output at the ROC. Three UX II receptacles and four HH-3-G sockets (manufactured by MAC EIGHT Co. Ltd.) are implemented on the top side of the PC board and two DF18C-100DS-0.4V(81) receptacle connectors are implemented on the bottom side of the board. The PC board is fabricated by Hayashi-REPIC Co. Ltd. and eight layered

<sup>&</sup>lt;sup>3</sup>Private communication with the FPHX chip developers.

**Table 16**Specifications of the conversion cable. The characteristic<sup>574</sup> impedance is given in differential of the LVDS pair.

575

| Item                         | Specification      | 57   |

|------------------------------|--------------------|------|

| μ-coax make                  | I-PEX Inc.         | 57   |

| $\mu$ -coa $	imes$ model     | CABLINE-UX II [21] | 57   |

| Harness AWG                  | 44                 | 57   |

| Characteristic impedance     | 90 Ω               | 58   |

| Number of harness per bundle | 50                 | 58   |

| Number of bundle             | 3                  | 58   |

| Power/ground cable AWG       | 24                 | 58   |

| Number of power cable        | 2                  | 58   |

| Number of ground cable       | 2                  | 58   |

| Length                       | 15 & 25 cm         | . 58 |

with dedicated layers for the digital and the analog-power and ground. The dimensions are 48 mm wide  $\times$  52 mm long<sub>889</sub> for the BEX end to match the size of the connector end, while the ROC side is rather compact with dimensions 25 mm wide  $\times$  25 mm long. There are two types of conversion cables namely "type-AC" and "type-BC" and the difference is so the channel mapping is compatible with the channel map, which are differently designed for the columns A&C and B&D of the input ports on the ROC. There are two different lengths of harnesses for the power and ground cables, which are 15 so and 25 cm, respectively.

### 4.3. ROC

533

534

536

537

538

540

542

544

548

551

552

553

555

556

557

559

560

561

563

565

567

569

571

The readout card (ROC) is a multilayered circuit board miplemented outside of the TPC volume. The ROCs were refurbished after the FVTX operation in the PHENIX experiment and reused for the INTT. ROC details are described elsewhere [7]. Any aspects of ROC usage that are different from the FVTX or customized for sPHENIX are discussed below.

Twelve pairs of DF18C-100DP-0.4V(51) plug connectors and four pairs of DF18C-60DP-0.4V(51) are implemented in the ROC as input ports for a half ladder. The DF18C-60DP-0.4V(51) plug connector has 60 pins and is not used for the INTT.

The ROC boards are originally implemented with 2.5 V<sup>611</sup> regulators to provide analog and digital power for the FPHX<sup>612</sup> chips with an operating voltage of 2.5 V for both analog and digital [9]. The voltage drop in the power-transfer line was minor in the FVTX owing to the short readout-cable length and low power consumption of the FPHX chip. On the contrary, as has been discussed in the previous sections, the INTT operates in the higher-power consumption mode due to its extraordinarily long readout cable chain. The FPHX operates with higher LVDS current for output data transmission than do the FVTX chips so that the signal amplitude is kept well above the receiver driver threshold.

The maximum drawing current per half ladder (26 FPHX chips) for the analog and digital power of the FPHX chips is measured to be 0.21 and 0.42 amps, respectively. Although the ROC are designed to allocate reasonably large physical

cross sections or american wire gauge (AWG) for the power transmission lines, the resistances of these cables is a couple hundred  $m\Omega$ . The resulting voltage drop of the daisy chain of the readout cables amounts to as much as 0.2 to 0.4 V which is sizable enough for the FPHX chips to possibly malfunction due to insufficient voltage supply.

To compensate for the voltage drop, the surface mounted regulators for the FPHX power are upgraded to supply larger output voltages. The pin layouts of the upgraded regulators match the pad pattern of the ROC. Newly implemented regulators are MCP1700-2802E/TT and MCP1726-3002E/MF (Microchip Technology Inc.) with outputs of 2.8 and 3.0 V for analog and digital power, respectively. With drawing currents increased for higher voltage outputs, the supplied voltages at the FPHX location are calculated to be  $\approx 2.5$  to 2.6 V for both analog and digital.

# 5. Radiation Hardness

In the INTT readout system (see Section 4), there are a few materials for which radiation hardness is either not known or known to be not durable. In this section, the radiation hardness is evaluated for these items. Also discussed is the study of the potential radiation damage of the ROC boards during the preceding PHENIX operation.

### 5.1. Bus Extender

The FPC with standard polymide is widely used in radiation environments and its radiation hardness is well established. However, because LCP is a relatively new material being used for the dielectric layer of the FPC, the radiation hardness of the FPC with LCP has not been established as well as that of the polymide. The radiation hardness of the LCP material itself is proven to be as durable as polymide [23] although, the radiation hardness of the bonding sheet employed for the BEX was not known. The overall mechanical characteristics of the BEX after assembly was measured before and after a radiation exposure rather than investigating the radiation hardness of the bonding sheet itself. The primary concerns are the degradation in the flexibility of the BEX and the peel strength of the bonding sheet due to radiation damage.

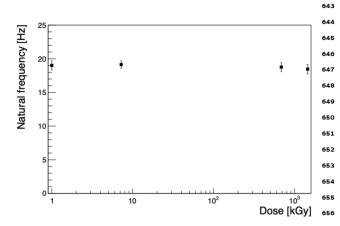

A few samples of the BEX cable were exposed to <sup>60</sup>Co source for 7.2 kGy, 685 kGy, 1.45 MGy at National Institutes for Quantum Science and Technology, Japan. The expected radiation dose at the location where the BEX is installed in sPHENIX is approximately 5 kGy for five years operation<sup>4</sup>. The mechanical performances were evaluated by following two tests; 1) stress test to evaluate the flexibility, and 2) peel strength test between the copper and the LCP layers [19]. As the test item 1), the Young's modulus was measured for the samples before and after the radiation exposure. Figure 16 shows the Young's modulus of these samples based on natural frequency measurements. No degradation of flexibility was observed within the accuracy of the measurements (7%)

<sup>&</sup>lt;sup>4</sup>including an extra two years of operation beyond the officially approved three years.

in any samples. The error was estimated by the standards deviation of multiple samples within the same radiation doses group.

626

628

629

630

631

633

634

635

637

639

Figure 16: The Young's modulus measurement results of  $_{658}$  samples exposed to various radiation dose. The vertical axis is the natural frequency in the unit of Hz, while the horizontal axis is the radiation dose in the unit of kGy. The measurement of the sample with no radiation exposure is plotted purposely at 1 kGy.

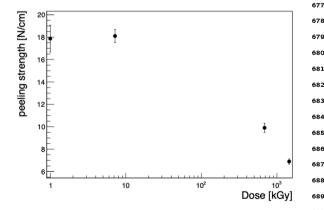

As shown in Fig. 17, approximately 50% and 70% degra-<sup>564</sup> dations were observed in the peel strength for 685 kGy and <sup>565</sup> 1.45 MGy samples, respectively. However, the measured <sup>566</sup> peel strength of 18 N/cm for the 7.2 kGy sample proved to <sup>667</sup> be, sufficiently strong and is similar to the typical level of <sup>668</sup> polymide-based FPC. Although the safety margin to keep <sup>669</sup> this peel strength for possible unexpected extra radiation <sup>670</sup> dose may be marginal, it is unlikely that FCCL layers would <sup>671</sup> fall apart by gravity even the peel strength was weakened by <sup>672</sup> 50%. It was thus concluded that the radiation hardness of the <sup>673</sup> BEX is expected to be durable for the duration of sPHENIX <sup>674</sup> operation.

Figure 17: The peel strength measurement results of samples<sub>691</sub> exposed to various radiation doses. The vertical axis is the peel<sub>692</sub> strength in units of N/cm, while the horizontal axis is radiation dose in units of kGy. The measurement of the sample with no radiation exposure is plotted at 1 kGy on purpose.

### 5.2. Conversion Cable

The material "fluorinated resin", which is used as a dielectric insulator for the  $\mu$ -coax cable [21], is reported to be weak against radiation [23] compared to popular dielectric insulator materials like polyimide or LCP. The estimated equivalent neutrons at the location of conversion cables to be installed is  $0.15 \times 10^{12}$  for three years of sPHENIX operation.

In order to address the radiation hardness of the  $\mu$ -coax harness for three years of sPHENIX operation, the effect of radiation was studied at the RIKEN Accelerator-driven compact neutron systems facility (RANS), Japan. Three samples of harness bundle were exposed to the RANS neutron beam at energies up to 5 MeV. Each sample was exposed to 1.3, 2.6, and  $4.0 \times 10^{12}$  equivalent neutrons. These are factors of 9, 17, and 27, respectively, more than the estimated radiation dose for the INTT operation in sPHENIX. The signal transmission performances were compared before and after the irradiation to evaluate the radiation effect. The comparisons were made for the S-parameters, the eye diagrams, and the TDR. No degradation was observed for all samples in any of these measurements, regardless of the exposed radiation dose. Thus, it is reasonable to conclude that the radiation hardness of the conversion cable is durable for the INTT operation as well.

### 5.3. ROC

The radiation dose of the ROC boards throughout five years of operation of the FVTX detector in PHENIX is estimated to have been approximately 300 Gy, while corresponding radiation dosage for three years of the INTT operation in sPHENIX is estimated to be approximately 50 Gy. The dose for the INTT is moderate owing to the relatively farther distance of the ROC position from the collision point compared to that of the FVTX in PHENIX. Here the radiation hardness of the ROC board with respect to the total dose of 350 Gy is evaluated.

The ROC board is designed to be radiation hard and in fact it utilizes the FLASH-based ACTEL ProASIC3E FPGAs [7] which is known to be radiation hard. The optical data transmission system of the ROC board comprises the model TLK2711 (Texas Instruments) as the serializer/deserializer of data. There is a study of the radiation tolerance of the TLK2711 [24]. In this study, the increase of leakage current and the bit-error rate was monitored as a function of radiation dose. The first bit error appeared ≈280–420 Gy and the TLK2711 encountered functional failure as low as 700 Gy depending on the beam condition of the radiation exposure, e.g., high (low) intensity and short (long) duration. While the leakage current stays the same up to 400 Gy, a rather rapid increase of current was observed beyond that point.

According to the above study, the condition of the TLK2711 are already in the range that some bit error symptom may start after the FVTX use. Altough it was preferable to replace them all before the reuse for the INTT, the model was discontinued. Unforatunately, insufficient quantities were available in the market place to replace them

760

all. Hence, the replacement candidates are prioritized and limited to only those which already have bit-error symptoms. The only ROCs installed are those which passed the various function tests including no bit-error symptoms.

# 6. Summary

697

699

700

701

703

705

707

709

711

712 713

715 716

717

718

719

720

721

722

723

724

726

727

730

731

732

733

735

736

737

738 739

740 741

743

744

745

749

750

752

A new silicon-strip detector was developed for the sPHENIX experiment at RHIC. The silicon ladder consisted of silicon-strip sensors, FPHX chips, HDIs, and a high thermally conductive carbon-fiber stave. The ladder was designed to be as thin as  $X/X_0 = 1.19\%$ . The bus extender and the conversion cables were developed to transmit signals from the ladder to the ROC board. The 1.11 m long bus extender cable employs the novel low attenuation LCP as the the conversion cable employs the novel low attenuation LCP as the the conversion cable employs in order to connect the bus extender end to the input/output or ports of the ROC board without introducing any stress at the connection.

The result of the study indicated that both the bus extender and the conversion cables are sufficiently radiation hard against estimated radiation dose for three years of the INTT operation in the sPHENIX experiment. In contrast, the exposed dose for TLK2711 chips of the ROC board throughout five years of the FVTX operation in the PHENIX experiment caused some bit errors to start to appear. Any chips showing these symptoms were replaced with new chips. The ROCs are installed relatively far away from the collision point for INTT operation in sPHENIX as opposed to FVTX in PHENIX. Thus, the radiation dose for the ROC boards in three years of INTT operation in sPHENIX is estimated to be relatively moderate, i.e. 1/6 of that of the FVTX in PHENIX.

### 728 References

- An upgrade concept from the PHENIX collaboration, arXiv:1207.6378v2 (2012).

- [2] Technical Design Report of sPHENIX (2019), https://indico.bnl.gov/event/7081/

- [3] K. Adcox et al., Nucl. Instr. and Meth. in Physics Research Section A 499 (2003) 469.

- [4] R. Belmont, et al., Predictions for the sPHENIX physics program, Nucl. Phys. A 1043 (2024) 122821, http://dx.doi.org/10.1016/j.nuclphysa.2024.122821.

- [5] S. Aune *et al.*, Nucl. Instr. and Meth. in Physics Research A 1066 (2024) 169615.

- [6] B. Aubert et al., Nucl. Instr. and Meth. in Physics Research A 479 (2002) 1.

- [7] C. Aidala et al., Nucl. Instr. and Meth. in Physics Research A 755 (2014) 44.

- [8] Hamamatsu Photonics KK, model S14629-01 data sheet.

- [9] J.S. Kapustinsky, Nucl. Instr. and Meth. in Physics Research A 617 (2010) 546.

- 747 [10] T. Zimmerman and J. Hoff, "FPHX Chip Documentation", Fermilab (2009).

- [11] Toray carbon fibers, TORAYCA T700 Data sheet.

- [12] Nippon Graphite Fiber Corporation, Granoc PREPREG NT91500-520S Technical data.

- [13] Evonik Industries AG, Rohacelll IG-F data sheet.

- [14] Mitsubishi Chemical Advanced Materials, Ketron CA30 PEEK data sheet.

- [15] The Henkel Corporation, LOCTITE EA 9396 AERO Technical process bulletin.

- [16] MasterBond, EP75-1 Technical data sheet.

- [17] The Henkel Corporation, LOCTITE ABLESTIC 2902 Technical data sheet.

- [18] 3M, Thermally conductive epoxy adhesive TC-2810 Technical data (2018).

- [19] T. Kondo *et al.*, Development of Long and High-Density Flexible Printed Circuits, Journal of The Japan Institute of Electronics Packaging, E21-007-1, 15 (2022).

- [20] Panasonic Corporation, FELIOS data sheet.

- [21] I-PEX Inc., CABLINE-UX II data sheet.

- [22] R. A. Matula, Electrical resistivity of copper, gold, palladium, and silver, Journal of Physical and Chemical Reference Data 8 (1979) 1147.

- [23] L. Whinnery et al., "Radiation Effects on Teflon Wires", SAND2017-9103C, 656517 (2017).

- [24] A. Aloisio and R. Giordano, "Results of the TLK2711-A Radiation Tolerance Tests", XVI SuperB Workshop, Frascati, Italy (2011).