4th BIC In-person Workshop, Apr 9, 2025 9-Chip PCB Testing **Bobae Kim** bobae.kim@anl.gov

### **Contents**

- Introduction

- Astropix

- Structure of Imaging Layer with AstroPix in BIC

- AstroPix 9 Chip PCB Test Module

- Testing Setup

- AstroPix Testing Result and Status

- ✓ AstroPix v3 Quad chip + GECCO board: Injection test

- ✓ AstroPix v3 Quad chip + CMOD board: Injection and Source tests

- ## 9 Chip PCB: HV issue

- ✓ AstroPix v4 single chip

- Summary & Plan

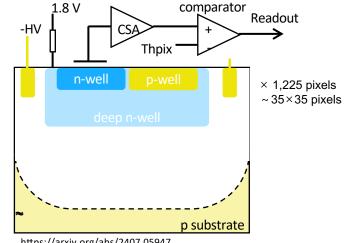

### Overview of AstroPix

High-voltage CMOS monolithic active pixel sensor (HV-CMOS MAPS)

- based on ATLASpix3 [arXiv:2109.13409]

- Originally developed for space-based missions, specifically for gamma-ray astrophysics

- NASA AMEGO-X space mission and ComPair2 project

- Use as the imaging layers in the barrel imaging calorimeter for nuclear physics applications.

#### Astropix v3 single chips

- $-2\times2$  cm<sup>2</sup> -size with 35  $\times$  35 pixel matrix

- 500 µm pixel pitch, 725 µm thickness

- ToT (Time over Threshold) clock: 12-bit at 200 MHz (5 ns)

#### Astropix v4 single chips

- 1 x 1 cm<sup>2</sup> -size with 13  $\times$  16 pixel matrix

- 500 µm pixel pitch

- Individual pixel readout

- 3 timestamps, 3.25 ns time resolution

- TuneDAC for pixel-by-pixel thresholds

https://arxiv.org/abs/2407.05947

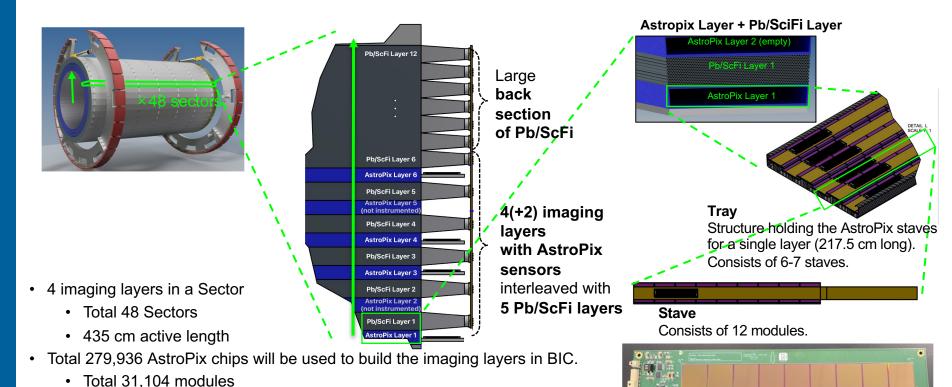

# Structure of Imaging Layer with AstroPix in BIC

• All Trays will be built using same modules, standardizing the loading procedure

• The first prototype module, built with v3 sensors for initial testing.

U.S. DEPARTMENT Augument of Emergy laboratory is a U.S. Department of Emergy laboratory

9 AstroPix sensors daisy-chained together on PCB.

**AstroPix Module**

Argonne 📤

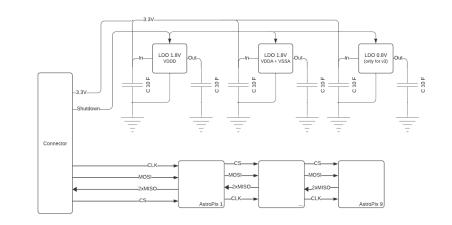

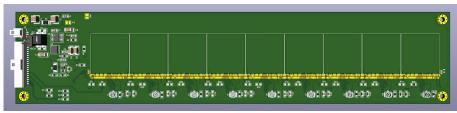

### **AstroPix 9 Chip PCB Test Module**

Similar design to quad chip board (no busbar required)

Nine AstroPix Chips, **Daisy-chained on the Module**Each Module plugs into its adjacent Module

All Modules will be controlled by the End-of-Tray Card

The broadcast commands/data readout through **SPI protocol**

One main HV line (~500V) and one (or 2) LV line (3.3V)

Voltage Regulators (LDO) to regulate power on each Module

- Analog and digital power of 1.8V at Module

4 differential data SPI (CIk, MOSI, 2MISO) common for stave

One **single-ended Chip-select SPI** per Module

Approximately 24 I/O + GND Pins per Stave

Exploring connector options (radiation hard, smaller size)

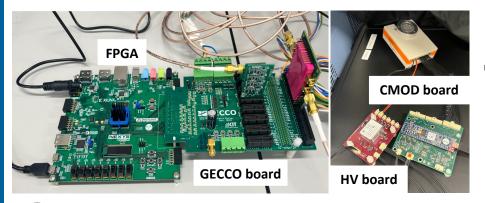

### **Testing Setup**

#### **Available Astropix and setup at ANL**

- AstroPix + GECCO board

- v3 single chip testing based on ASTEP sw/fw used in FY24 beam test at FNAL

- v4 single chip testing based on astropix-python sw/fw

- AstroPix + CMOD board + ASTEP sw/fw

- 1 layer quad chip working

Available up to 3 layers: work in progress

- ## 9 chip PCB: work in progress

- W112Q07 + v.1.0.0 carrier board

- W06Q08 + v.1.0.0 carrier board (Noisy)

- W112Q04 + v.1.0.1 carrier board

- W112Q06 + v.1.0.1 carrier board

- ! W08Q09 + v.1.0.1 carrier board + bus bar

- W101Q01 + v.1.0.1 carrier board + bus bar

- W101Q02 + v.1.0.1 carrier board + bus bar

- W101Q04 + v.1.0.1 carrier board + bus bar

- W101Q12 + v.1.0.1 carrier board + bus bar (kapton behind chip)

#### 9 chip PCB module (9 Astropix v3 single chips)

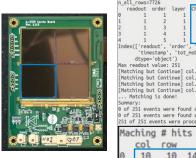

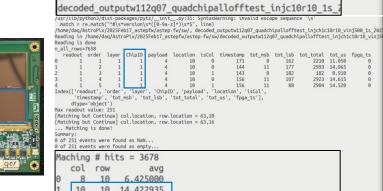

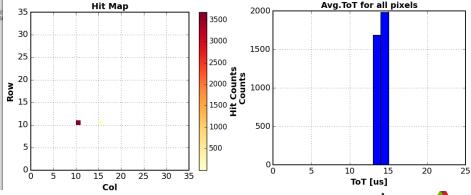

### **Astropix Testing (0)**

### **Quad Chip+GECCO board: Injection Test**

Injected 300 mV to [10,10] on chip0 and chip1; W112Q07

decoded outputw112g07 quadchipallofftest injch1c10r10 vin

U.S. DEPARTMENT Argonne National Laboratory is a of ENERGY Managed by UChicago Argonne, LLC

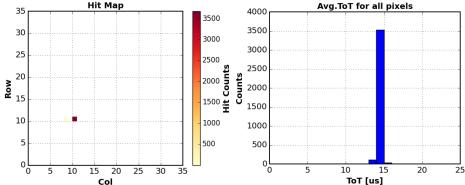

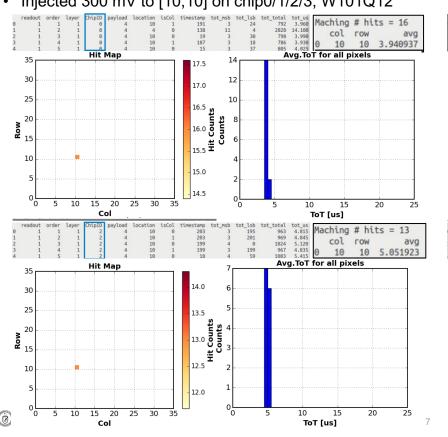

# **Astropix Testing (1)**

### **Quad Chip: Injection Test**

• Injected 300 mV to [10,10] on chip0/1/2/3; W101Q12

# **Astropix Testing (2)**

U.S. DEPARTMENT

of ENERGY

Argonne National Laboratory is a

U.S. Department of Energy laboratory

managed by UChicago Argonne, LLC.

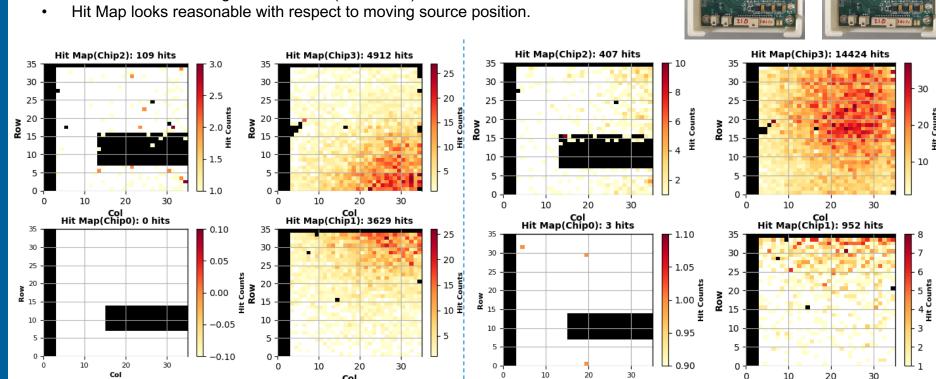

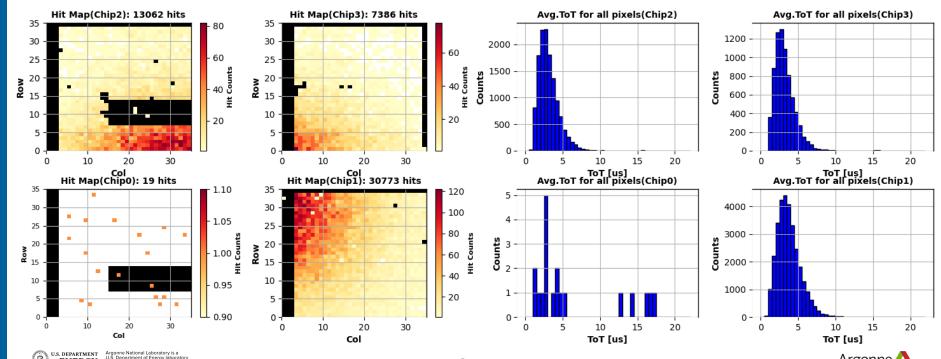

#### **Quad Chip: Sr90 Source Test (1)**

Sr90 source test using CMOD board (W101Q12)

Col

Col

Sr90

Sr90

Col

### **Astropix Testing (3)**

#### **Quad Chip: Sr90 Source Test (2)**

- Sr90 source test using CMOD board (W101Q12)

- The hit map aligns well with the source position at the center of the quad chip.

- The ToT distribution is well-described by a Landau convoluted with a Gaussian function.

### **Astropix Testing (4)**

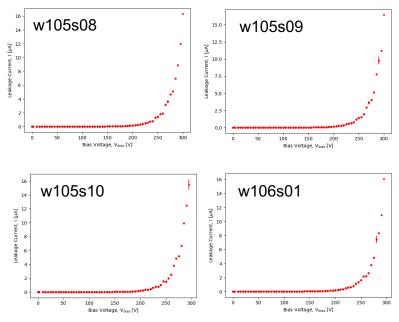

#### **Current Status of 9 Chip PCB: HV issue**

- Unable to apply high voltage to 9 chip PCB due to overcurrent under investigation

- High voltage could be applied to the bare PCB (without chips)

- IV measurement of four AstroPix v3 single chips before assembly (w105s08/s09/s10 and w106s01)

- Unable to apply high voltage to 9 chip PCB with four mounted chips

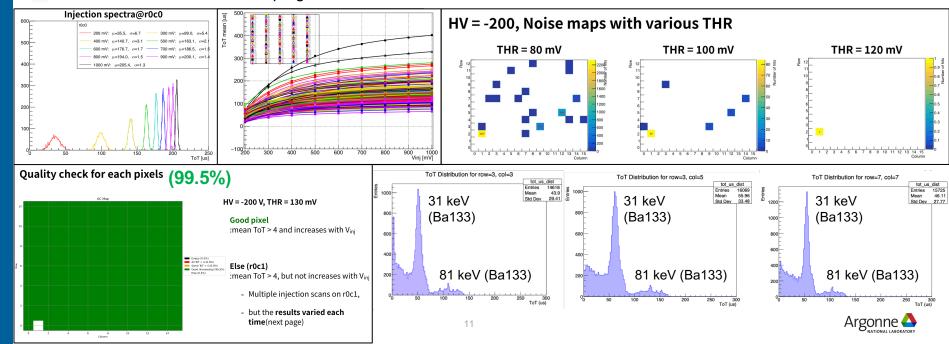

# **Astropix Testing (5)**

#### Astropix v4 single chip (YoonHa)

- ✓ Optimized the configuration for v4 testing

- ☑ Injection scan (HV = -200 V, threshold = 130 mV)

- ✓ Noise scan

- Source test for calibration curve at Busan National University: in progress

- Beam test at KEK or CERN: in progress

# **Summary & Plan**

- Astropix v3 single and quad chip, v4 single chip testing

- ✓ AstroPix v3 Quad chip + GECCO board: Injection test

- ✓ AstroPix v3 Quad chip + CMOD board: Injection and Source test

- ## 9 Chip PCB: HV issue

- ✓ AstroPix v4 Single chip

- Prototype module (9 AstroPix v3 single chips) testing will be done by July 2025 for PDR.

#### Not shown: **AstroPix and BIC Timeline** Early CD4 (Oct 2032) CD4 (Oct 2034) We are here **FY19 FY20 FY21** FY22 **FY23** FY24 **FY25 FY26 FY27 FY28 FY29** Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 01 02 03 Q2 Q3 Q4 Q2 Q3 Q2 Q3 Q1 Q2 Q3 v3 has comprehensive test program: benchtop and testbeam, irradiation, Design & Fabr. AstroPix v1 Test quad-chip readout for NASA payload mission (A-STEP), integration with Design & Fabr. AstroPix v2 Test Pb/SciFi for ePIC (R&D studies and test article production) Design & Fabr. AstroPix v3 Test **Test** first v5 wafers used for preproduction Design & Fabr. AstroPix v4 **Test** Start of production driven by project fund availability **EIC Project Milestone** Design AstroPix v5 (estimated ~ 1 year after CD2/3) Test & Fabr. New AstroPix version AstroPix v6 AstroPix v6 Production Fab. Test (production) Design and generic R&D ePIC BIC Timeline Final design and EIC R&D **BIC Preproduction BIC Production** CD2/3 C<sub>D</sub>0 CD1 CD3a Start of BIC installation at BNL AstroPix v5 AstroPix v1 pre-production chip HV-CMOS MAPS based on ATLASPix3. 1.87 x 1.9575 cm<sup>2</sup> chip, 500 µm pixel pitch designed for the AMEGO-X NASA mission, Design identical to v4 (with bug fixes) optimized for power dissipation AstroPix v2 AstroPix v3 AstroPix v4 and energy resolution AstroPix v6 First full-size chip Final design but smaller size NIMA 1019 (2021) 165795 production chip 2 x 2 cm<sup>2</sup> chip, 500 µm pixel pitch 1 x 1 cm<sup>2</sup> chip, 250 µm pixel pitch 2 x 2 cm<sup>2</sup> chip, 500 µm pixel pitch 1 x 1 cm<sup>2</sup> chip, 500 µm pixel pitch 0.45 x 0.45 cm<sup>2</sup> chip, 175 µm pixel pitch Design identical to v5 (with bug fixes) 35 x 35 pixel matrix Row/column readout Individual pixel readout 18 x 18 pixel matrix Argonne National Laboratory is a Power dissipation of Engray laboratory and Engray laboratory and Power dissipation of Engray laboratory and Engray laboratory and Power dissipation of Engray laboratory and Power dissipa Row/column readout Power dissipation <1 mW/cm<sup>2</sup> 3 timestamps, 3.25 ns time resolution Power dissipation 3.4 mW/cm<sup>2</sup> TuneDAC for pixel-by-pixel thresholds 2.5 MHz timestamp, 200 MHz ToT