# eRD107: Longitudinally separated Forward HCal (LFHCal)

**April 17, 2025**

Friederike Bock (ORNL) for the eRD107 consortium

Participating institutes: ORNL, BNL, FNAL, ISU, GSU, Yale, UCR, UTK, UTA, Valpo, Debrezen

### The General Idea

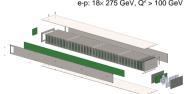

### **Concept:**

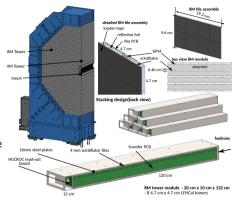

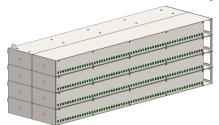

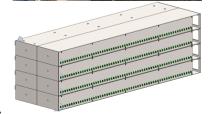

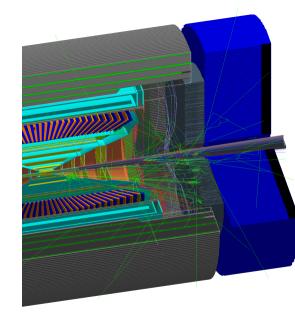

- CALICE AHCal inspired Fe-Scintillator calorimeter with SiPM on-tile-readout (modification since last review)

- Two main parts:

- ► LFHCal built mostly out of 10x20x132 cm<sup>3</sup> 8M modules (modified length to accommodate larger amount of services in barrel)

- ▶ Insert built out of 2 halves surrounding the beam pipe

#### LFHCal:

- ▶ 60 layers of steel interleaved with scintillator material

- ► Transverse tower size 5x5 cm<sup>2</sup>

- ► Multiple consecutive tiles summed to 7 longitudinal segments per tower

#### Insert:

- ▶ 60 layers of steel interleaved with scintillator

- ► Hexagonal tiles of 8 cm<sup>2</sup> each read-out individually

1/23

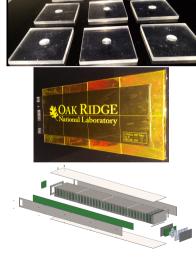

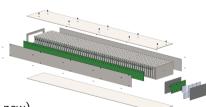

# **LFHCal 8M Scintillator Tile assembly**

2/23

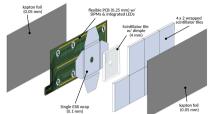

- Tiles of  $\approx 0.4x5x5$  cm<sup>3</sup> with dimples individually wrapped in ESR foil assembled in a grid of 4x2 tiles

- 8 tiles are backed by a flexible PCB equipped with 8 SiPMs and LEDs sandwiched with Kapton foil

- Flexible PCB wrapped around side of absorber to connect with long PCB along the side of the module

- Tiles either injection molded or machined out of cast sheets

### **Read-out LFHCal & insert**

- High granularity needed to try to distinguish shower maxima close to beam pipe

- LFHCal: read out in 7 layers longitudinally (5 or 10 SiPMs summed) desirable min measurable tower energy 3-5 MeV, max 20-30 GeV in single tower segment

- insert: read out every single tile desirable min measurable tower energy  $\sim 0.1-0.5~\text{MeV}/$  tile

- SiPMs mounted to flexible PCBs, passive signal transfer to back side of calorimeter using long transfer PCB

- 1 SiPM-HGCROC (up to 70 channels) per 8M module (56 channels) in the back, 320 HGCROCs for insert readout

# Reminder: Remaining eRD107 Milestones

- Tile production optimization using machining & injection molding

- ► Evaluation of tolerance compliance for machined tiles

- Test module assembly & beam test

- ► First prototype of full 8M module

- ► Integration of final read-out

- ► Test beam evaluation of prototype (optionally with ECal in front)

# eRD107 - Progress - executive summary

- Prototype tile production using machining & injection molding

- ► Evaluation of tolerance compliance for machined tiles completed

- 2 Integration of final read-out

- ► Third iteration of sensor board produced and operated in TB

- ► First passive summing test board produced

- ► First test beam with HGCROC read-out for LFHCal completed reading every single SiPM & analysis ongoing

- Preparations for 2025 TB-campaigns & TB analysis

- ► Test beam analysis from 2023 & 2024 on-going, aiming at paper combined paper for late summer

- Preparations for large scale 8 x 8M module test beam CERN at SPS & PS in Oct/Nov ongoing

Largest fraction of TB components and efforts from 2024 & 2025 have been financed by PED,  $\approx 1/20$  for 2024 from remaining R&D funds.

# Scintillator Production - Tolerance evaluation (1)

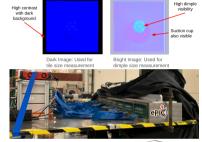

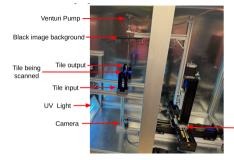

- Yale setup created for fully automated tile dimension scanning using X-Y translation stage, camera & UV light source

- Evaluation of outer dimensions of machined tiles & dimple size

- Large scale evaluation possible without significant human intervention

Yale

Dark Image: Used for

Bright Image: Used for dimple size measurement

Molded Tile

# **Scintillator Production - Tolerance evaluation (2)**

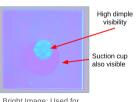

- Measured dimensions molded and machined tiles with calipers (for external size) and automated measurement

- Molded tiles compliant within measurement uncertainties with specifications

- Machined tiles with significant variations beyond acceptable limits

- Variations in particular on thickness beyond expected values

- ⇒ Need to incorpate these variations in design and possible specification modifications for the machined tile production

## Test beam - August 2024

**Dates:** 28<sup>th</sup> Aug-11<sup>th</sup> Sept 2024 **Location:** PS - T09 **Main purpose:** First full module test & H2GCROC tests **Setup:**

- Full 8M module testing 65 layers of absorber & scintillator per layer 8 channels (swapping scintillator geometry either 8M module or insert )

- Readout with multiple CAEN DT5202 64ch CITIROC SiPM readout units (2nd week) and H2GCROCs (1st week)

- Had to be postponed from May to August due to delays in deliveries of components & new H2GCROC firmware and boards tested during the ALICE FoCal TB in May 2024

#### **Main expected measurements:**

- Energy resolution estimates for hadrons and electrons for full length module with both read-out versions

- Assessment of longitudinal leakage

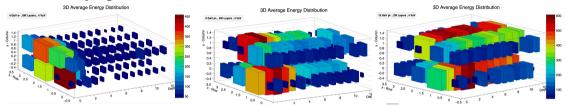

- Longitudinal shower development

- Read-out validation

- Part of campaign with EEEMC in front

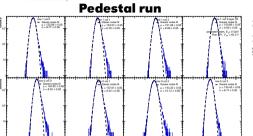

# **HGCROC** online monitoring

#### $\mu$ for calibrations

| i ioi cui  |            |

|------------|------------|

| Run 281    | Run 281    |

| FPGA 2     | FPGA 2     |

| ASIC 1     | ASIC 1     |

| Channel 64 | Channel 63 |

|            |            |

| Run 281    | Run 281    |

| FPCA 2     | FPGA 2     |

| ASIC 1     | ASIC 1     |

| Channel 55 | Channel 56 |

|            |            |

| Run 281    | Run 281    |

| FPGA 2     | FPGA 2     |

| ASIC 1     | ASIC 1     |

| Channel 45 | Channel 46 |

| Run 281    | Run 281    |

| FPGA 2     | FPGA 2     |

| ASIC 1     | ASIC 1     |

| Channel 37 | Channel 36 |

| Run 281    | Run 281    |

| FPGA 2     | FPGA 2     |

| ASIC 1     | ASIC 1     |

| Channel 34 | Channel 33 |

|            |            |

| Run 281    | Run 281    |

| FPGA 2     | FPGA 2     |

| ASIC 1     | ASIC 1     |

| Channel 25 | Channel 26 |

|            |            |

| Run 281    | Run 281    |

| FPGA 2     | FPGA 2     |

| ASIC 1     | ASIC 1     |

| Channel 16 | Channel 14 |

|            |            |

| Run 281    | Run 281    |

| FPGA 2     | FPGA 2     |

| ASIC 1     | ASIC 1     |

| Channel 7  | Channel 6  |

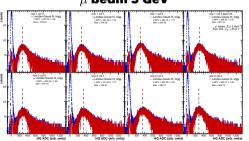

### 4 GeV e<sup>-</sup> for first energy resolution

#### layer 1-8

| - <b>u</b> c • c                        |                                           | st chick g                      | y i cooia                                 |                                           |                                           | iayei      |                                           |

|-----------------------------------------|-------------------------------------------|---------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|------------|-------------------------------------------|

| Run 331                                 | Run 331                                   |                                 | Run 331                                   | Run 331                                   | Run 331                                   | Run 33T    | Run 331                                   |

| FPGA 2                                  | FPGA 2                                    |                                 | FPGA 2                                    | FPGA 2                                    | FPGA 2                                    | FPCA 2     | FPGA 2                                    |

| ASIC 1                                  | ASIC 1                                    |                                 | ASIC 1                                    | ASIC 1                                    | ASIC 1                                    | ASIC 1     | ASIC 1                                    |

| Channel 64                              | Channel 63                                |                                 | Channel 65                                | Channel 69                                | Channel 70                                | Channel 67 | Channel 68                                |

| Run 331<br>FPGA<br>ASIC 1<br>Channel 55 | Run 331<br>FPGA 2<br>ASIC 1<br>Channel 56 |                                 | Run 331<br>FPGA 2<br>ASIC 1<br>Channel 58 | Run 331<br>FPGA 2<br>ASIC 1<br>Channel 62 | Run 331<br>FPGA 2<br>ASIC 1<br>Channel 61 |            | Run 331<br>FPGA 2<br>ASIC 1<br>Channel 59 |

| Run 331                                 | Run 331                                   | Run 331                         | Run 331                                   | Run 331                                   | Run 331                                   | Run 331    | Run 331                                   |

| FPGA 2                                  | FPGA 2                                    | FPGA 2                          | FPGA 2                                    | FPGA 2                                    | FPGA 2                                    | FPGA 2     | FPGA 2                                    |

| ASIC 1                                  | ASIC 1                                    | ASIC 1                          | ASIC 1                                    | ASIC 1                                    | ASIC 1                                    | ASIC 1     | ASIC 1                                    |

| Channel 45                              | Channel 46                                | Channel 47                      | Channel 48                                | Channel 52                                | Channel 51                                | Channel 50 | — Channel 49                              |

| Run 331                                 | Run 331                                   | Run 331                         | Run 331                                   | Run 331                                   | Run 331                                   | Run 331    | Run 331                                   |

| FPGA 2                                  | FPGA 2                                    | FPGA 2                          | FPGA 2                                    | FPGA 2                                    | FPGA 2                                    | FPGA 2     | FPGA 2                                    |

| ASIC 1                                  | ASIC 1                                    | ASIC 1                          | ASIC 1                                    | ASIC 1                                    | ASIC 1                                    | ASIC 1     | ASIC 1                                    |

| Channel 37                              | Channel 36                                | Channel 39                      | Channel 38                                | Channel 42                                | Channel 43                                | Channel 40 | Channel 41                                |

| Run 331                                 | Run 331                                   | Run 331                         | Run 331                                   | Run 331                                   | Run 331                                   | Run 331    | Run 331                                   |

| FPGA 2                                  | FPGA 2                                    | FPGA 2                          | FPGA 2                                    | FPGA 2                                    | EPGA 2                                    | FPGA 2     | FPGA 2                                    |

| ASIC 1                                  | —ASIC 1                                   | ASIC 1                          | ASIC 1                                    | ASIC 1                                    | ASIC 1                                    | ASIC 1     | ASIC 1                                    |

| —Channel 34                             | Channel 33                                | Ghannel 32                      | Channel 31                                | Channel 27                                | Channel 28                                | Channel 29 | Channel 30                                |

| Run 331                                 | Run 331                                   |                                 | Run 331                                   | Run 331                                   | Run 331                                   | Run 334    | Run 331                                   |

| FPGA 2                                  | FPGA 2                                    |                                 | FPGA 2                                    | FPGA 2                                    | FPGA 2                                    | FPGA 2     | FPGA 2                                    |

| ASIC 1                                  | — ASIC 1                                  |                                 | ASIC 1                                    | ASIC 1                                    | ASIC 1                                    | ASIC 1     | ASIC 1                                    |

| Channel 25                              | Channel 26                                |                                 | Channel 24                                | Channel 20                                | Channel 19                                | Channel 22 | Channel 21                                |

| Run 331                                 | Run 331                                   |                                 | Run 331                                   | Run 331                                   | Run 331                                   | Run 331    | Run 331                                   |

| FPGA 2                                  | FPGA 2                                    |                                 | FPGA 2                                    | FPGA 2                                    | FPGA 2                                    | FPGA 2     | FPGA 2                                    |

| ASIC 1                                  | ASIC 1                                    |                                 | ASIC 1                                    | ASIC 1                                    | ASIC 1                                    | ASIC 1     | ASIC 1                                    |

| Channel 16                              | Channel 14                                |                                 | Channel 12                                | Channel 9                                 | -Channel 11                               | Channel 10 | Channel 13                                |

| Run 331                                 | Run 331                                   | Run 331 FPGA 2 ASIC 1 Channel 5 | Run 331                                   | Run 331                                   | Run 331                                   | Run 331    | Run 331                                   |

| FPGA 2                                  | FPGA 2                                    |                                 | FPGA 2                                    | FPGA 2                                    | FPGA 2                                    | FPGA 2     | FPGA 2                                    |

| ASIC 1                                  | ASIC 1                                    |                                 | ASIC 1                                    | ASIC 1                                    | ASIC 1                                    | ASIC 1     | ASIC 1                                    |

| — Channel 7                             | Channel 6                                 |                                 | Channel 4                                 | Channel 0                                 | Channel 1                                 | Channel 2  | Channel 3                                 |

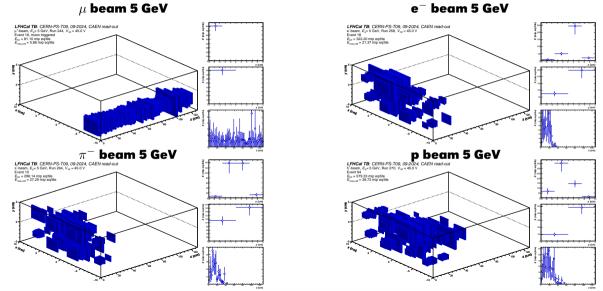

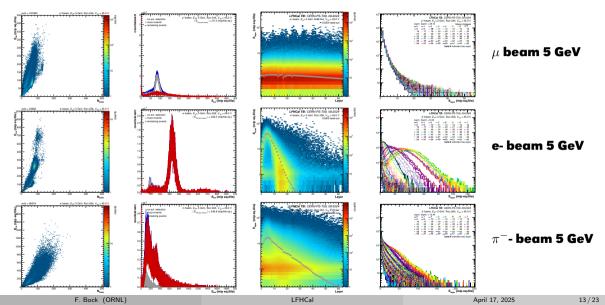

# 2023/2024 Test Beam analysis

#### **Test Beam data:**

- 2023: Data primarily used for scintillator evaluation

- 2024: Two large data sets with HGCROC & CAEN read-out collected with massive support from ePIC collaborators from various institutes

#### **Test Beam analysis:**

- Large participation in test beam analysis from grad students & under-grad students

- Common framework developed and being used for all existing TB campaigns, analysis full done in this

- Current focus on establishing stable calibrations (single cell level) for all channels & runs within

each data set

- Aiming at full publication in late summer based off the 2023 & 2024 test beam campaigns

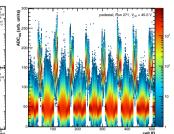

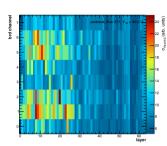

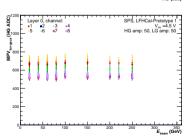

## **Calibrations**

$\mu$  beam 5 GeV

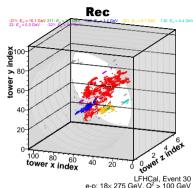

# First Calibrated Event displays from last year

# First Highlights from last year

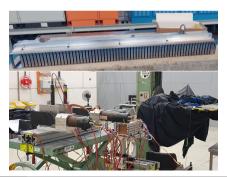

### **Test Beam Plans 2025**

**Requested time:** 1 week each **Main purpose:** Resultion studies

**Location:** CERN SPS (29th Oct) & PS (17th Nov.)

### Setup:

- Very similar to 2024 setup, with more modules

- 8 full 8M modules (ideally 40x40x132 cm)

- Readout with H2GCROCs

- Same setup in both areas

### Main expected measurements:

- Energy resolution for hadrons and electrons

- Assessment of longitudinal/transversal leakage

- Longitudinal shower development

- Final-Flexible PCB validation & first long PCB validation

#### Where we are?:

- 8 Absorber structures produced (last 3 at Nickel-plating right now)

- Flex-PCB design available & SiPMs to be delivered in June

- First design of long board available, will be send for prototype production within the next weeks

- Evaluation board for passive summing created and under test

## eRD107 - milestones & executive summary

#### **Milestones**

- Tile production optimization using machining & injection molding

- ► Evaluation of tolerance compliance for machined tiles

- Test module assembly & beam test

- ► First prototype of full 8M module

- ► Integration of final read-out

- ► Test beam evaluation of prototype (optionally with ECal in front)

#### **Executive summary**

- Prototype tile production using machining & injection molding

- ► Evaluation of tolerance compliance for machined tiles completed

- Integration of final read-out

- ► Third iteration of sensor board produced and operated in TB

- ► First passive summing test board produced

- ► First test beam with HGCROC read-out for LFHCal completed reading every single SiPM & analysis ongoing

- Preparations for 2025 TB-campaigns & TB analysis

- ► Test beam analysis from 2023 & 2024 on-going, aiming at paper combined paper for late summer

- ▶ Preparations for large scale 8 x 8M module test beam CERN at SPS & PS in Oct/Nov ongoing

Dark Image: Used for

# Thanks!

### eRD107 - Progress - executive summary - 2024

#### ① Reconstruction optimization

- ► Realistic implementation of geometry in ePIC software stack

- ► ML assisted absorber optimization in full geometry setup

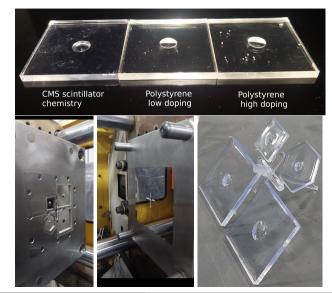

#### 2 Prototype tile production using machining & injection molding

- ► Ongoing machining studies for tile production

- ► First tile production with injection molding at Fermilab with different tile chemistries

#### 3 Tile Characterization

- Light yield studies of machined & injection molded tiles with different dimple sizes, machining techniques and wrappings ongoing

- ► Position scan of response on-going

#### Sensor board development

- ► Third iteration of sensor board produced in three different processes

- Tests of calibration circuits ongoing

#### ⑤ Preparations for third TB-campaign (Aug 2024) & TB analysis

- ► Test beam analysis from Sept. & Oct. 2023 on-going

- ► Currently setting up in PS beam line, TB starting today

# **Tile production R&D**

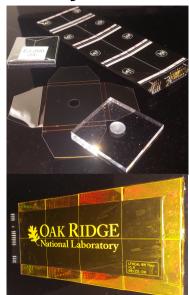

- First larger scale injection molding production by Fermilab with 3 different chemistries

- Additional scintillator machining studies on the way

- Produced tiles with different dimple sizes

- Additional production to come in the coming months to equipp August test beam modules

# **Scintillator Characterization & Optimization**

- Started measuring cosmics MIP light yields for different SiPMs types

- ► 1.3 × 1.3 mm

- ightarrow pprox 12 14 p.e. for machined tiles

- $\rightarrow~\approx 11-13$  p.e. for injection molded tiles,

- ▶ 3 × 3 mm

- $ightarrow \approx 60-76$  p.e for machined tiles

- Testing different scintillator materials (EJ-200, BC-408 & Fermilab injection molded with different chemistries)

- Systematic evaluation of impact of machining defects ongoing and large scale sample on-going

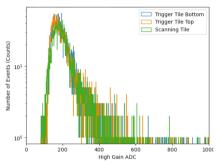

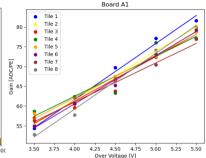

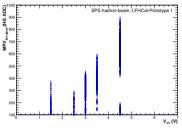

- Single photon spectra for every SiPM of the TB assemblies vs  $V_{\rm civ}$

### **LFHCal: Test beams 2023**

#### **Dates:**

SPS: 6<sup>th</sup> - 13<sup>th</sup> Sept.

PS: 11<sup>th</sup> - 18<sup>th</sup> Oct.

### Setup:

Parasitic to FoCal-H/FoCal-E at SPS and PS

Setup consists out of maximum 14 layers of 8M tile assemblies

Sept: w/o absorber layers

Oct: w/ absorber layers (4 tungsten, 10 steel)

Read-out: CAEN DT5202 64ch CITIROC SiPM readout unit or H2GCROC

### Main expected measurements:

- Light yields per tile

- Shower profile measurements with different absorbers

- Cross talk estimates of different tiles

- Use it as testing setup for SiPM-H2GCROC

- If placed behind FoCal-H, measure part of leakage

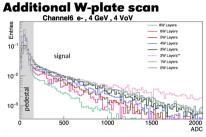

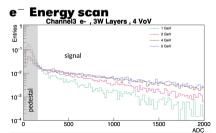

### LFHCal TB 2023: Data obtained - CAEN read-out

### October campaign

#### September campaign - Hodoscope setup

- Full  $V_{ov}$  scan e<sup>-</sup>/h

- Gain-scan

- Position scan

- Possibly leakage measurement of FoCal-H

### October campaign - mini-LFHCal

- Full  $V_{ov}$  & gain scan  $e^-/\pi^-$

- Position scan

- Scan with additional W-plates upfront (e<sup>-</sup>)

- e<sup>-</sup> shower development (1-5 GeV)

- $\pi^-$  shower development (5,10,15 GeV)

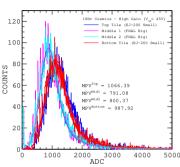

## LFHCal TB 2023: First results - CAEN read-out

### **MIP** response for scintillators

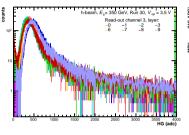

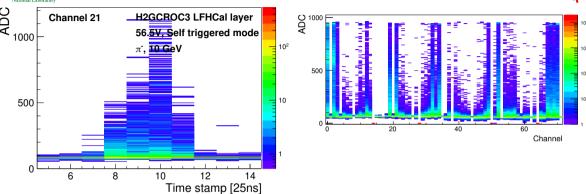

### LFHCal TB 2023: First results - H2GCROCv3a

- H2GCROC read-out ready just in time for last 1.5 days of data taking (Oct.)

- Self-triggered data obtained

- Unfortunately externally triggered setup couldn't be operated due to beam stop of PS during last night

- New prototype board on time for delivery for testing significantly ahead of TB

F. Bock (ORNL) LFHCal April 17, 2025 23/23